# **Heterogeneous Modular Platform**

Sergey Shumarayev

CTO Office, Programmable Solution Group, Intel® Corporation

## **Motivations**

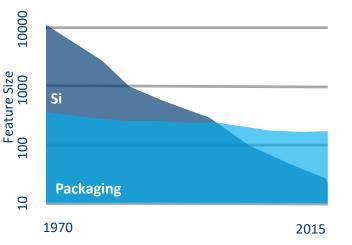

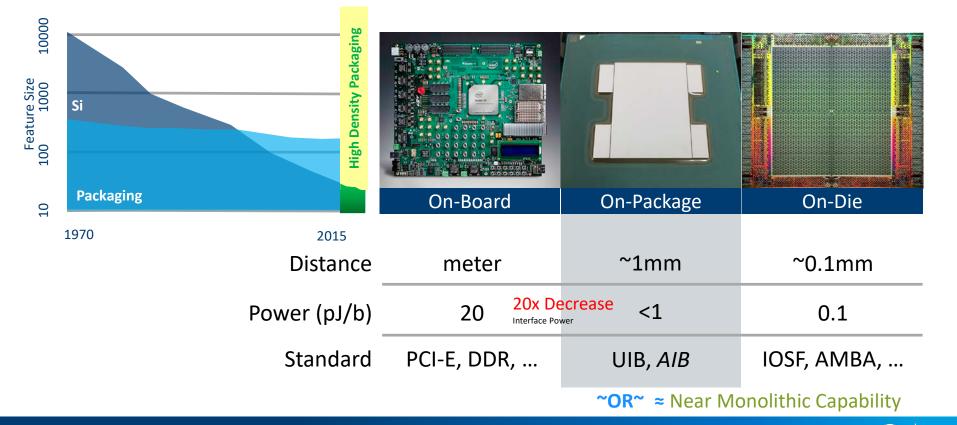

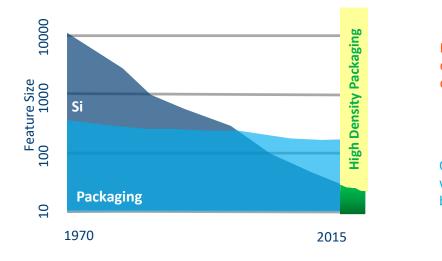

#### Disparity between silicon and package/board technologies

- Drove SERDES needs to connect the dies

- Increase in serialization requirements

- SERDES up to ~30% area and ~30% power in high end system

Manufacturing cost increase and yields decrease with significant non-reparable die size for analog

- Increased complexity, system latency, and power

- Long coupled development cycles for analog + digital on same monolithic die

## **Motivations**

Programmable Solutions Group

# **High Density Packaging** Technology **Enables Heterogeneous** Integration

#### Cramming More Components onto Integrated Circuits

GORDON E. MOORE, LIFE FELLOW, IEEE

#### VIII. DAY OF RECKONING

Clearly, we will be able to build such component crammed equipment. Next, we ask under what circumstances we should do it. The total cost of making a particular system function must be minimized. To do so, we could amortize the engineering over several identical items, or evolve flexible techniques for the engineering of large functions so that no disproportionate expense need be borne by a particular array...

...It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected.

#### Cramming More Components onto Integrated Circuits

GORDON E. MOORE, LIFE FELLOW, IEEE

...It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected.

# Heterogeneous is part of Moore's law More of Moore

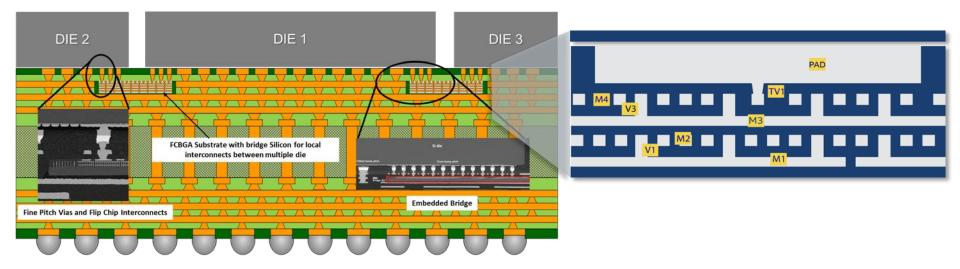

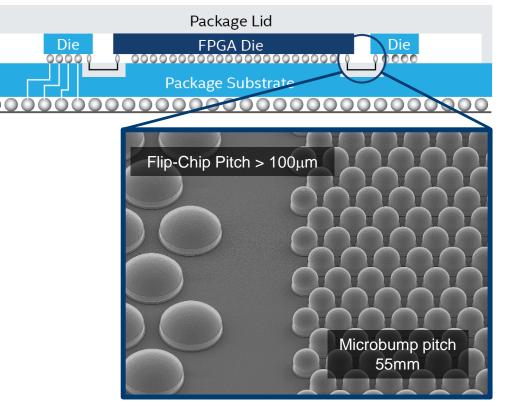

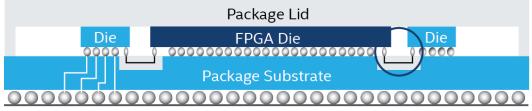

## Intel<sup>®</sup> Embedded Multi-Die Interconnect Bridge (EMIB) Technology

## Intel® Embedded Multi-Die Interconnect Bridge (EMIB) Technology

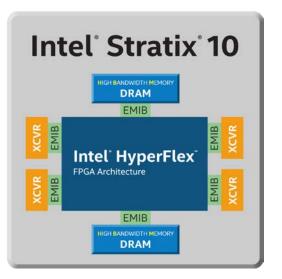

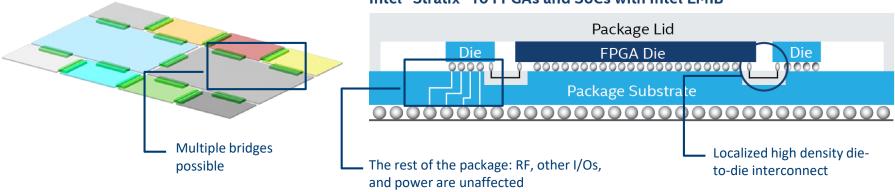

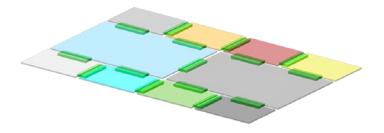

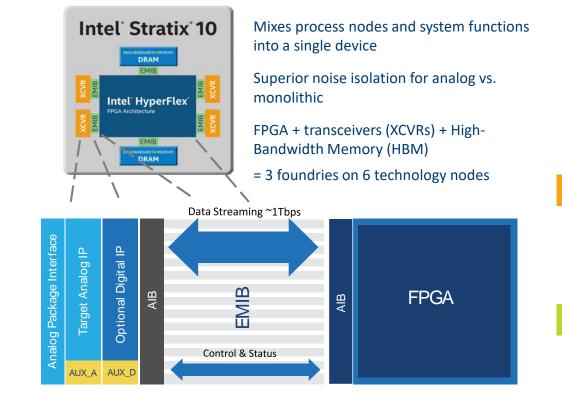

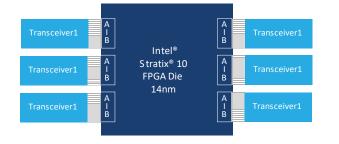

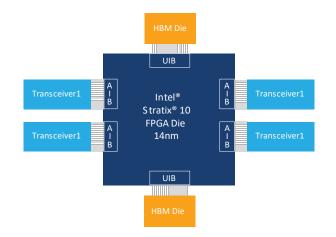

#### Intel® Stratix® 10 FPGAs and SoCs with Intel EMIB

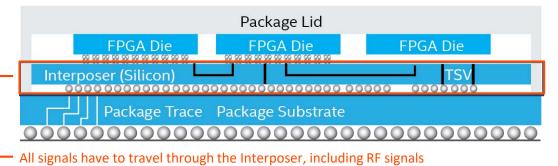

#### High Density Package Technology Offerings

#### Intel® Stratix® 10 FPGAs and SoCs with Intel EMIB

#### **Other Multi-Die Integration**

#### Intel<sup>®</sup> Embedded Multi-Die Interconnect Bridge (EMIB) Technology

Intel® Stratix® 10 FPGAs and SoCs with Intel EMIB

# Reduced Fabrication and Assembly Cost Effective, High Performance Solution No Reticle Size Limitations

## **Optimized Interface PPA**

′intel

## Choosing Die to Die Signaling

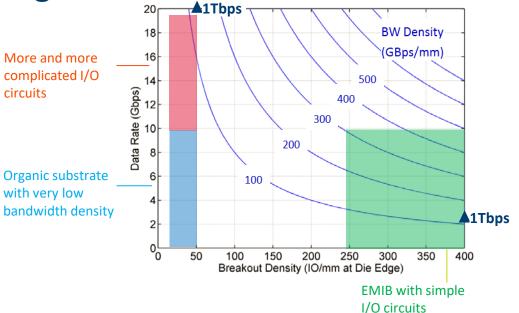

Disparity Gap is addressed by High Density Packaging

- EMIB with Simple parallel IO circuitry is preferred over serial signaling:

- ✓ power↓ + latency↓ + scalability↑

## Intel<sup>®</sup> Stratix<sup>®</sup> A New Class of Product = Platform

cycles

## Chiplets, Platforms, and SiP?

A chiplet is a functional, verified, re-usable physical IP block

Realized in physical form, i.e. in effect a building block (e.g. processor, converters, memory, waveform generators, filters, etc.)

High performance (based on 2.5D/3D) system in package (SiP) :

- Created through integration of chiplets vs. monolithically

- Platform provides framework governing composition rules

## Intel<sup>®</sup> PSG SiP Interface Options: AIB and UIB

Two types of interfaces for two types of applications use cases

UIB general purpose SiP interface for HBM and ASIC

Programmable Data Rate of up to 2Gbps per physical line

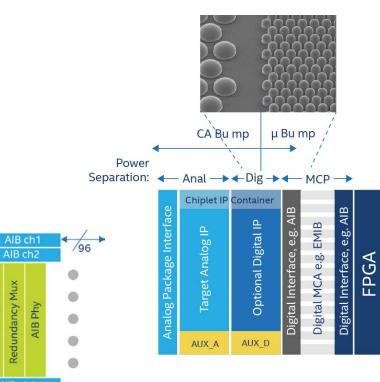

## Intel<sup>®</sup> PSG AIB Architecture Overview

Power separation for improved flexibility and PI

The AIB is subdivided into 25 logical channels:

24 are user channels + aux to handshake

Adaptor for light weight data streaming

- Abstract Phy details from target IP provider

- AIB Phy redundancy steering:

- Invisible to IP designer

96

Redundancy Mux

AIB Aux

AIB Adaptor

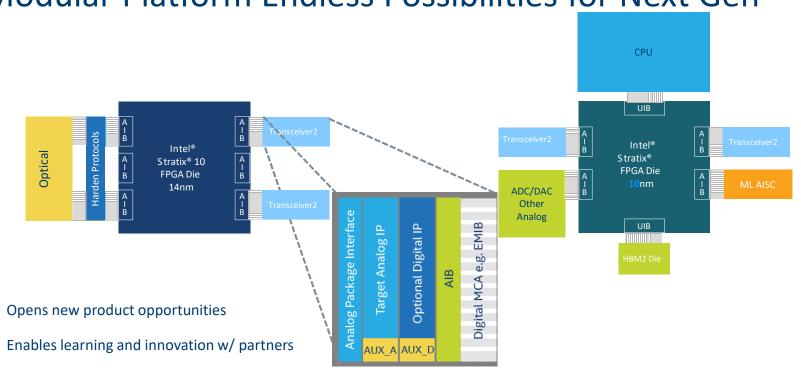

## Modular Platform Enables Heterogeneous Systems

- Decouples ASIC / FPGA / Analog design cycles

- Improved TTM

- Reduced deployment and development cost

## Modular Platform Enables Cost-Effective Upgrades

- Facilitate revolutionary capability for best-of-breed technology selection

- Expedited time to market

- AIB & UIB provides flexible HBM and TRCVers attachment

## Modular Platform Endless Possibilities for Next Gen

Accelerates transformative market deployment

#### Heterogeneous 3D System-in-Package (SiP) Integration

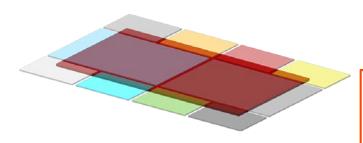

#### Efficient and Scalable Integration Using Intel<sup>®</sup> EMIB

Convergence of process nodes and system functions into a **Multi Chip Package (MCP).** Mix and match process nodes

Enables higher efficiency and flexibility.

>20K EMIB connections up to 2 Gbps each

## Reduces size, weight, and power

Heterogeneous Integration For More of Moore

Intel<sup>®</sup> EMIB Technology is Cost Effective, High Performance Solution

Programmable interface (e.g. UIB and AIB) for flexible attachment

Intel<sup>®</sup> Stratix<sup>®</sup> A New Class of Product = Heterogeneous MCP Platform

# Heterogeneous Integration

## Legal Notices and Disclaimers

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

All products, computer systems, dates and figures specified are preliminary based on current expectations, and are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

© 2017 Intel Corporation. Intel, the Intel logo, and others are trademarks of Intel Corporation in the U.S. and/or other countries.

Altera, Arria, Cyclone, Enpirion, Max, Megcore, Nios, Quartus and Stratix, words and logos are trademarks of Altera and registered in the U.S. Patent and Trademark Office and in other countries.

\*Other names and brands may be claimed as the property of others.