#### Eta Compute Self-timed ARM M3 Microcontroller for Energy Harvested Applications

### Agenda

#### Motivation

- A New Paradigm

- Dial Technology

- Chip Architecture

- Measured Results

- Sensor Reference Design

#### Deploying Billions of Sensors Require

- Low cost

- Small size

- Robust operation in unfriendly environments

- Standardized hardware and easy software development

- ARM processors with standard wireless

- NO BATTERIES....

### Issues with Batteries

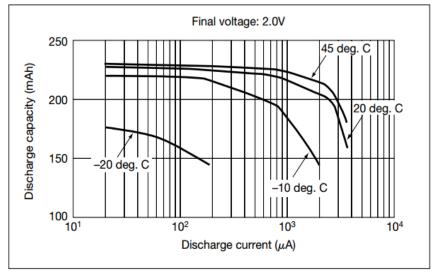

Relationship between Discharge Current and Discharge Capacity

Limited temperature range Limited capacity

#### Hazardous Waste / Disposal

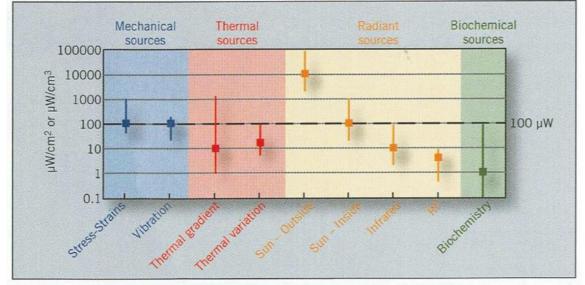

#### Power Available from Energy Harvesting

- EH can supply 1uW to 100uW indoors (exclude PV outdoors)

- EH can support sensor fusion computations

- Storage from super-caps or rechargeable batteries for wireless connections

A comparison of ambient energy sources (before conversion). (Source: CEA-Leti).

### Agenda

- Motivation

- A New Paradigm

- Dial Technology

- Chip Architecture

- Measured Results

- Sensor Reference Design

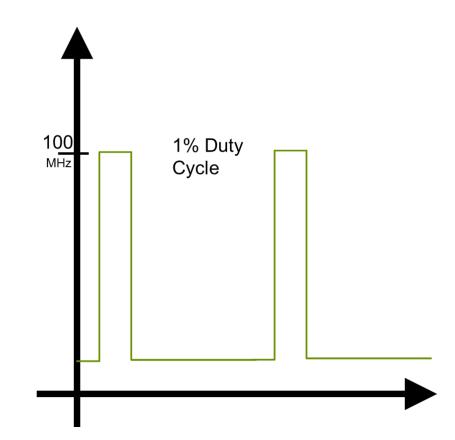

### "Race to Idle" Paradigm

Minimize energy use by running fast and switching to idle

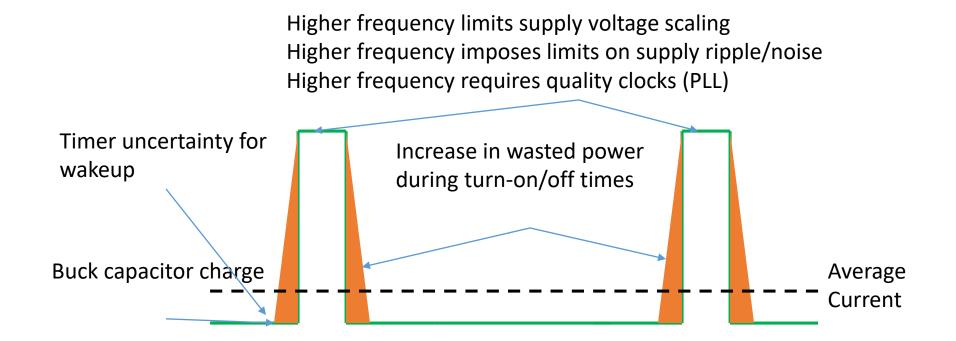

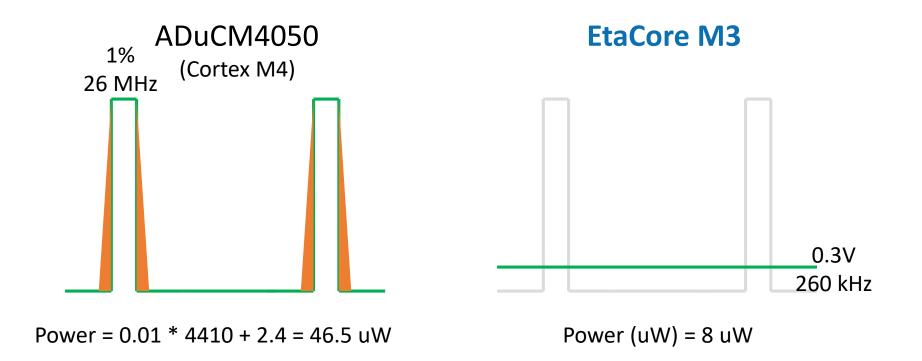

### "Race to Idle" Wastes Energy

• Microcontrollers increasing frequency to reduce active time

### "Always-on" Paradigm

6x better without even accounting for wasted power !

### Software – "Race to Idle"

In EM4, the current is down to 20 nA and all chip functionality is turned off

except the pin reset, GPIO pin wake-up, GPIO pin retention, Backup RTC (including retention RAM) and the Power-On Reset. All pins are put into their

#### • Familiarize yourself with processor energy modes and transition times

#### Table 3.1. Energy Mode Description 8 EM0 - Energy Mode 0 In EM0, the CPU is running and consuming as little as 211 µA/MHz, when running code from flash. All peripherals can be active. (Run mode) 4 Average current (μA) EM1 – Energy Mode 1 In EM1, the CPU is sleeping and the power consumption is only 63 µA/MHz. 2 (Sleep Mode) All peripherals, including DMA, PRS and memory system, are still available. 1 In EM2 the high frequency oscillator is turned off, but with the 32.768 kHz oscillator running, selected low energy peripherals (LCD, RTC, LETIMER, EM2 – Energy Mode 2 PCNT, LEUART, I<sup>2</sup>C, LESENSE, OPAMP, USB, WDOG and ACMP) are still (Deep Sleep Mode) available. This gives a high degree of autonomous operation with a current consumption as low as 0.95 µA with RTC enabled. Power-on Reset, Brown-0.5 out Detection and full RAM and CPU retention is also included. In EM3, the low-frequency oscillator is disabled, but there is still full CPU and RAM retention, as well as Power-on Reset, Pin reset, EM4 wake-up and 0.25 EM3 - Energy Mode 3 Brown-out Detection, with a consumption of only 0.65 µA. The low-power (Stop Mode) 125 250 1000 2000 4000 ACMP, asynchronous external interrupt, PCNT, and I<sup>2</sup>C can wake-up the 500 8000 16000 32000 device. Even in this mode, the wake-up time is a few microseconds Wake-up period (ms)

EM4 - Energy Mode 4

reset state

(Shutoff Mode)

EM2 (GG)

EM2 (LG)

\_\_\_\_EM4

### Software – "Race to Idle"

- Familiarize yourself with different clocks

- Organize code to minimize wakeups

| Oscillator Type F |                                                            | Frequency                                                                               | Typical consumption | Typical start-<br>up time | Typical use                     |

|-------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------|---------------------------|---------------------------------|

| HFRCO             | Internal RC                                                | Run-time selectable: 1,<br>7, 11, 14, 21 or 28 MHz                                      | 22-106 µA           | 1 µs                      | Main HF clock                   |

| HFXO              | External crystal/ceramic<br>resonator or external<br>clock | Fixed: 4 -32/48 MHz<br>for resonators. Less<br>than 32 or 48 MHz for<br>external clock. | 85-165 μA           | 400 µs                    | Main HF clock                   |

| AUXHFRCO          | Internal RC                                                | Run-time selectable: 1,<br>7, 11, 14, 21 or 28 MHz                                      | 22-106 µA           | 1 µs                      | Debug and flash<br>write timing |

| LFRCO             | Internal RC                                                | Fixed: 32 kHz                                                                           | 190 nA              | 150 µs                    | LF peripheral<br>clock          |

| LFXO              | External crystal/ceramic<br>resonator or external<br>clock | Fixed: 32.768 kHz<br>for resonators. Less<br>than 48 or 32 MHz for<br>external clock    | 190 nA              | 400 ms                    | LF peripheral<br>clock          |

| ULFRCO            | Internal RC                                                | Fixed: 1 kHz                                                                            | NA (always on)      | NA (always on)            | Watchdog clock                  |

### Software – "Always on"

• Power constrained : Determine available power and set voltage

#### OR

• Performance constrained : Determine MIPS needed and set voltage

## Agenda

- Motivation

- A New Paradigm

- Dial Technology

- Chip Architecture

- Measured Results

- Sensor Reference Design

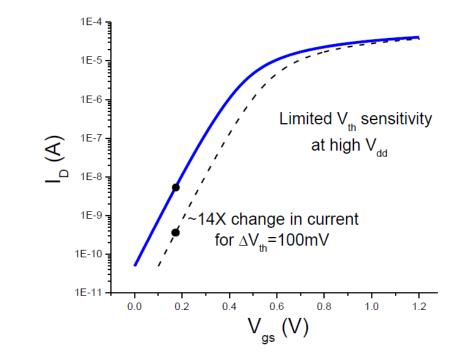

## Challenges in Deep Subthreshold Operation

- Model quality

- Large delay variation over PVT

- Lognormal delay distribution – timing closure tools ?

- 3x mismatch between adjacent gates

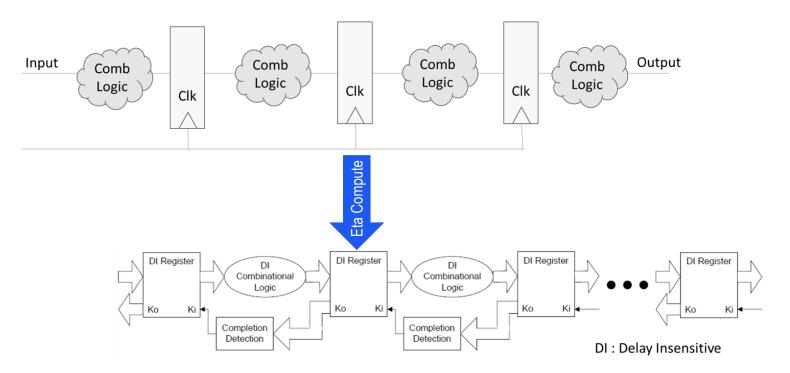

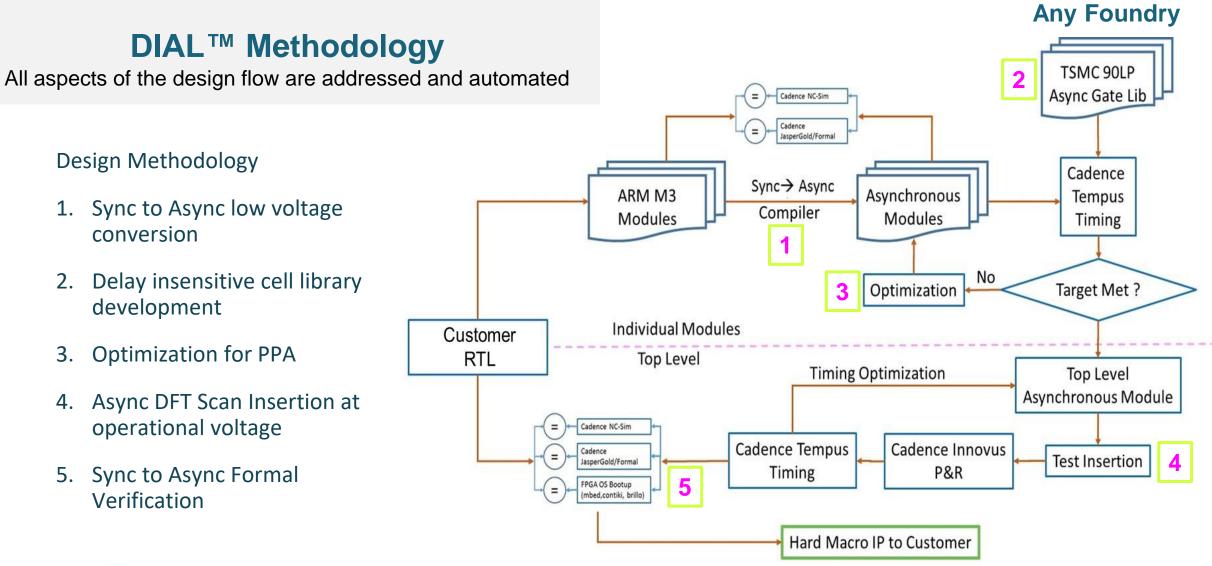

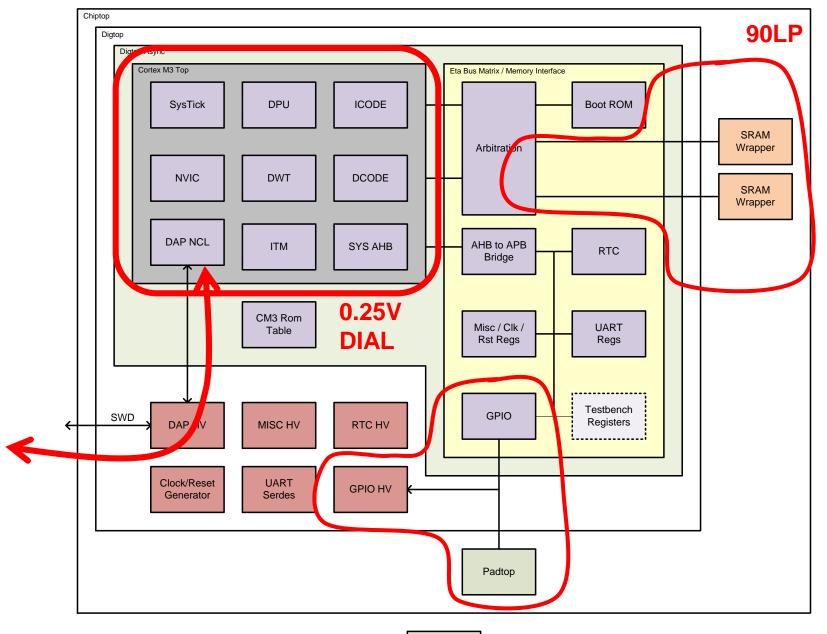

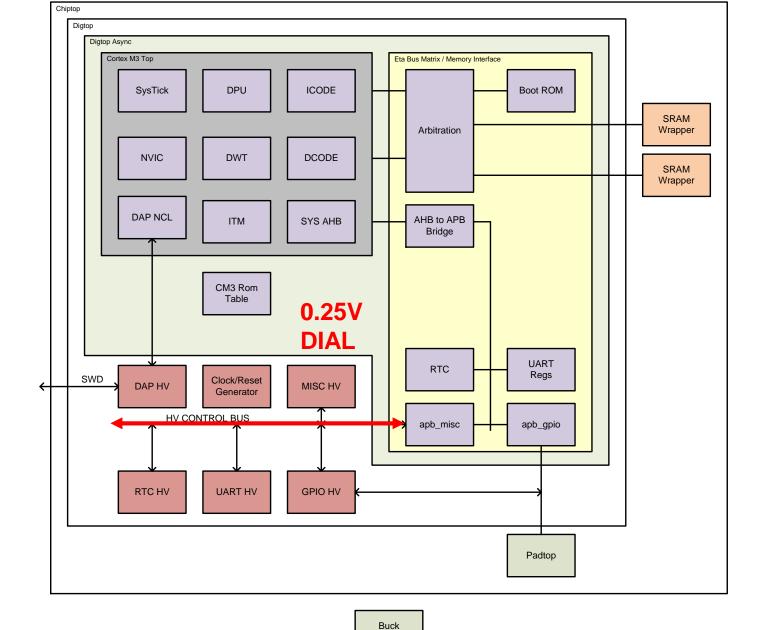

### DIAL Architecture

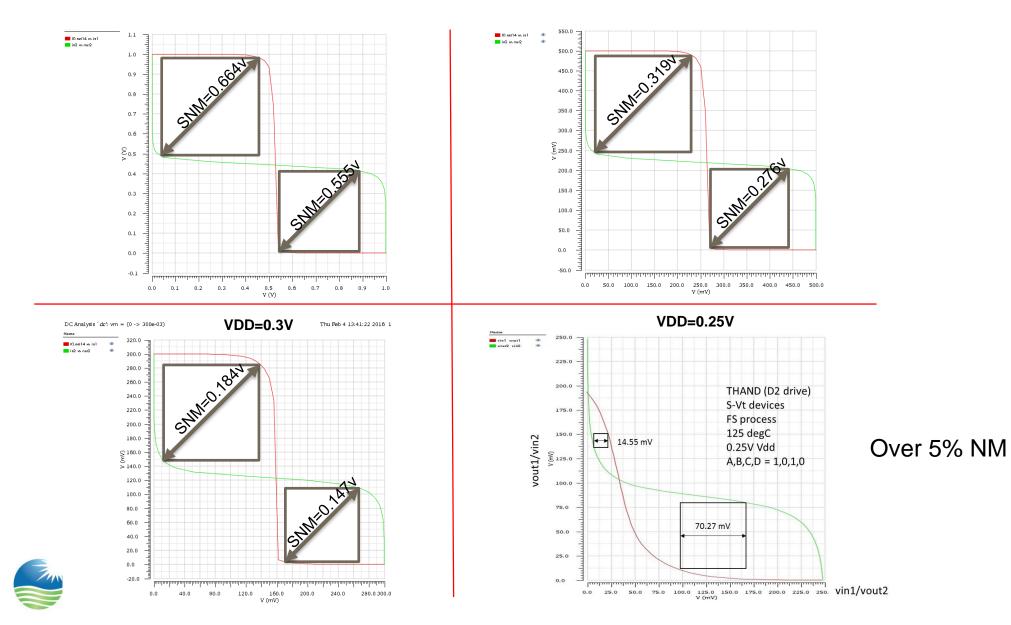

• Circuit operates from 0.25 – 1.2V continuously with no resets required

#### **Foundry Library**

- We've done 180nm, 130nm, 90nm and 55nm

- Deep sub-threshold operation

- 5X MIPS/Watts of any competing processor

- Used this logic to develop low power SoC

- Allows processor operation down to 0.25V

- Robust across and temperature

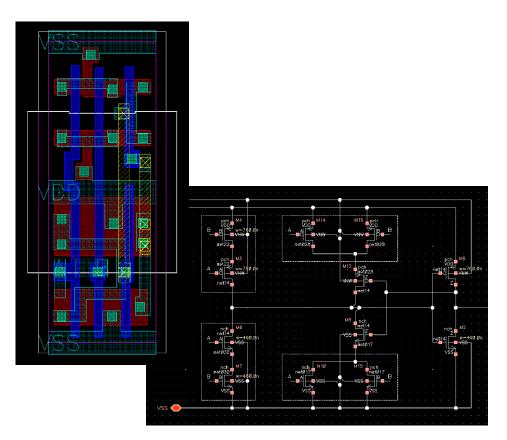

#### **Design for Low-Voltage Operation over Corners**

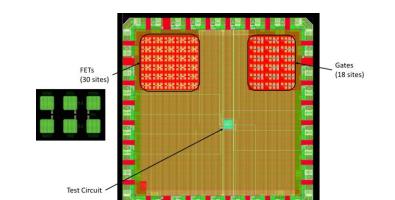

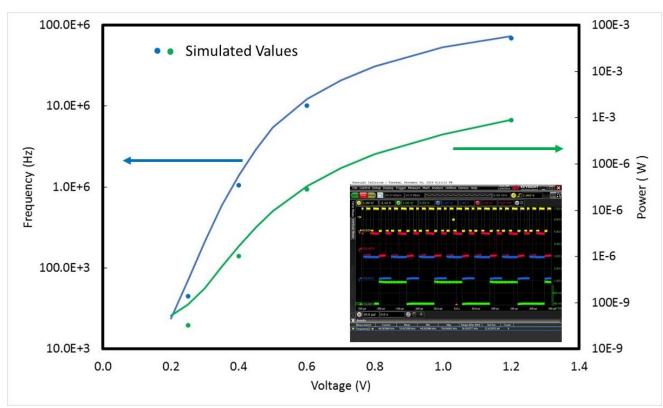

#### Silicon Measurements of Test Circuits and Cell Library

- Transistor chains and gates for standard cell characterization – in progress

- Example of TSMC90LP

- 32 bit counter test chip shows good match between measurements and simulations

- 25 kHz / 50 nW

- Today we also have a fully functional fully self timed Cortex M3 SOC in DIAL technology.

#### Build Into a Holistic Low Power Platform

- Low-voltage, delay insensitive logic

- 1 patent granted, 15 pending

- Digital circuits

- Coolflux DSP

- Real Time Clocks

- AES

- Asynchronous SAR ADC

- High efficiency power management

- Unique interfaces to SRAM, UART...

"Eta Compute can safely claim without contradiction that they have developed the world's lowest power microcontroller IP" Bernard Murphy: SemiWiki, ex-CTO Atrenta

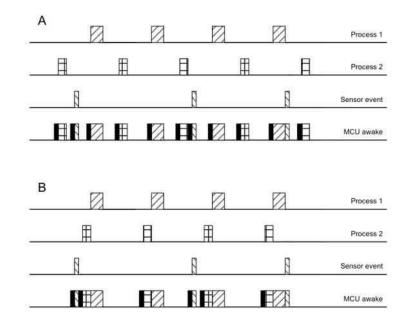

#### Benefits of an Always On Processor

- Fast interrupt response

- Regular monitoring of sensor to alter node behavior

- Optimize transducer energy conversion (MPPT)

- Schedule RF during high source energy periods

- Vary performance depending on load ("paddleshift")

- Sensor data collection / processing at low frequency

- RF transmission at high frequency

- "Pay as you go" on energy

Eta Compute

oscillator only when communicating

### Agenda

- Motivation

- A New Paradigm

- Dial Technology

- Chip Architecture

- Measured Results

- Sensor Reference Design

Converter

### Agenda

- Motivation

- A New Paradigm

- Dial Technology

- Chip Architecture

- Measured Results

- Sensor Reference Design

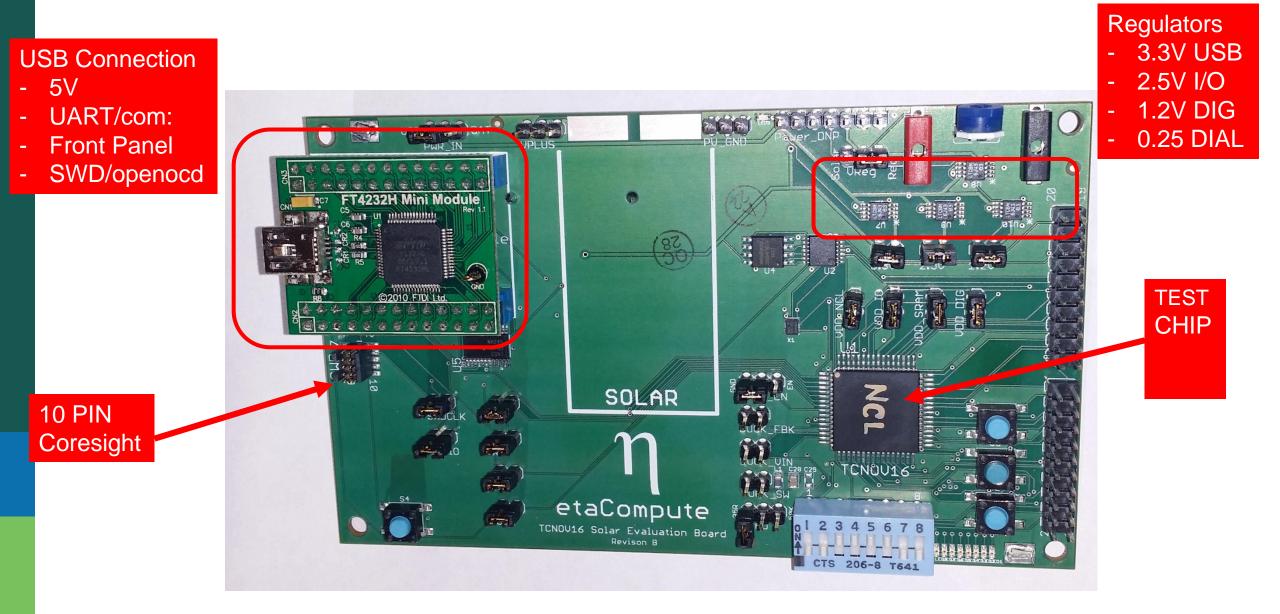

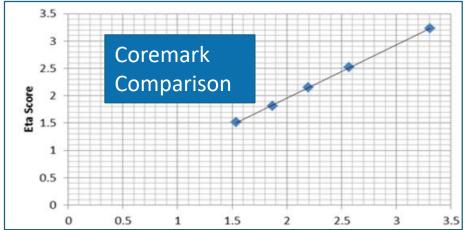

#### Silicon Measurements of ARM Cortex<sup>®</sup>-M3 based SoC

- TSMC90LP M3 Operation at 5 uW

- Optimizations yielded 30% reduction- more coming

- Standard Eclipse, Keil and Linux debug and development

- Runs >200 kHz directly off solar cell with fluorescent lighting

- Working on 55LP ARM Cortex-M3

- Further power reductions

- DSP, ADC, PMIC, RTC

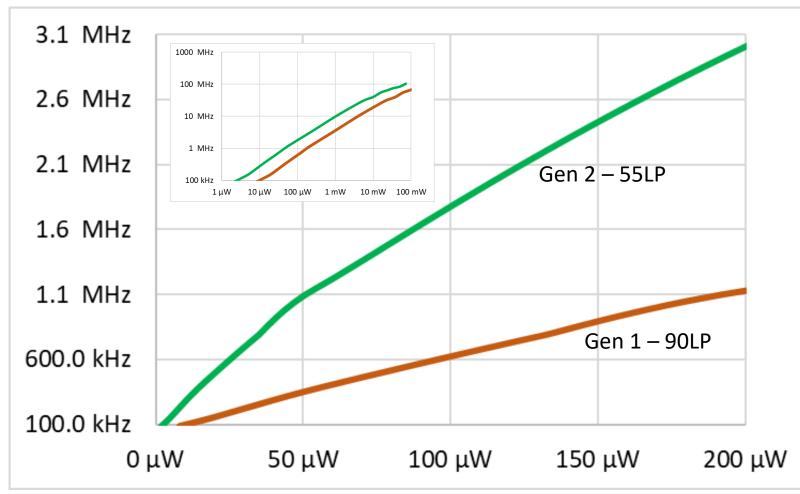

### Etacore EH - Performance

EH- enhanced DI Gen 2 in design now

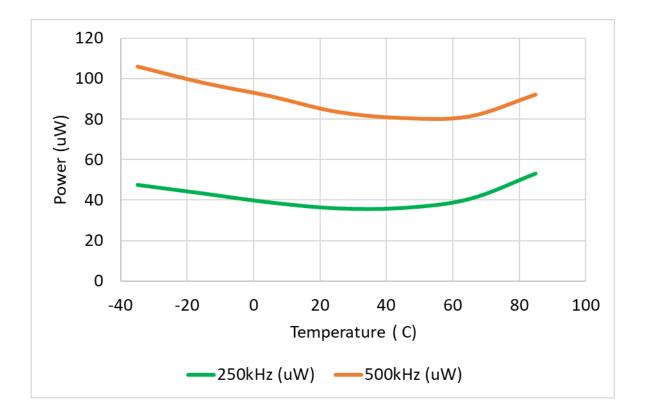

#### Minimal Power Variation across Temperature

Constant current- PMIC varies voltage for temp & process compensation

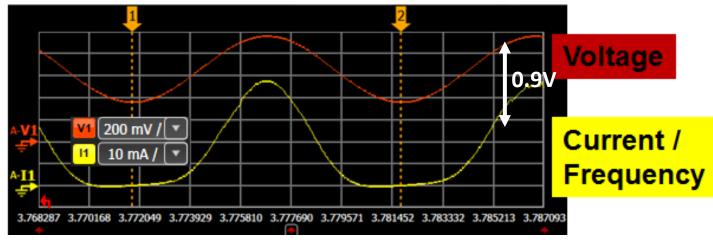

#### Robust to Power Supply Variation

### Agenda

- Motivation

- A New Paradigm

- Dial Technology

- Chip Architecture

- Measured Results

- Sensor Reference Design

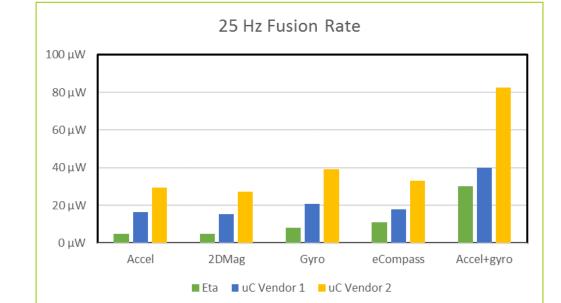

#### Sensor Fusion Applications

- Sensor hub processing using M4 instruction set

- A possible next step on our roadmap.

- Optimized design flow with EtaCore

DSP is estimated to reduce power by

over 2x compared to these numbers

- Estimated instruction count from Freescale app note

- Advantage grows exponentially with lower fusion rate

- eg. Bluetooth Beacon

|    | State               | Time (us) | Current (mA) | Comments                                 |

|----|---------------------|-----------|--------------|------------------------------------------|

| 1  | Pre-processing      | 1160      | 3.26         | Radio setup                              |

| 2  | Radio Prep          | 101       | 4.3          | Radio on / Transition to RX              |

| 3  | ТХ                  | 280       | 6.1          | 0 dBm, Channel 37, 20 bytes              |

| 4  | TX to RX Transition | 112       | 4.66         | Tx to Rx transition                      |

| 5  | RX                  | 184       | 6.47         | Receive Time                             |

| 6  | RX to TX Transition | 370       | 3.43         | Rx to Tx transition                      |

| 7  | ТХ                  | 280       | 6.1          | 0 dBm, Channel 37, 20 bytes              |

| 8  | TX to RX Transition | 112       | 4.66         | Tx to Rx transition                      |

| 9  | RX                  | 184       | 6.47         | Receive Time                             |

| 10 | RX to TX Transition | 370       | 3.43         | Rx to Tx transition                      |

| 11 | ТХ                  | 280       | 6.1          | 0 dBm, Channel 37, Aruba - 20 bytes      |

| 12 | TX to RX Transition | 112       | 4.66         | Tx to Rx transition                      |

| 13 | RX                  | 184       | 6.47         | Receive Time                             |

| 14 | Post Processing     | 685       | 2.45         | Process received packets and go to sleep |

|    | Total On Time       | 4.414     | msec         |                                          |

|    | Transmit dutycycle  | 0.5       | sec          |                                          |

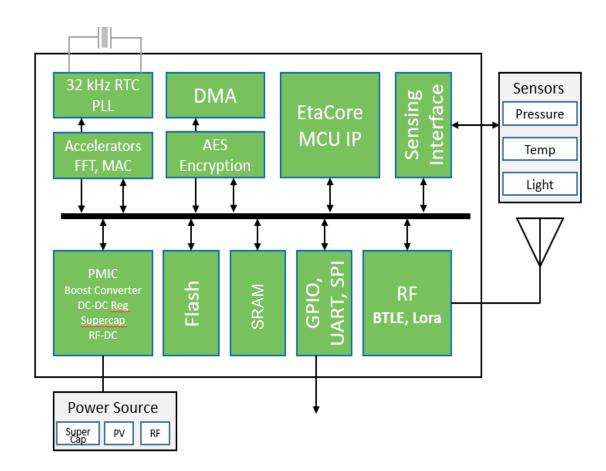

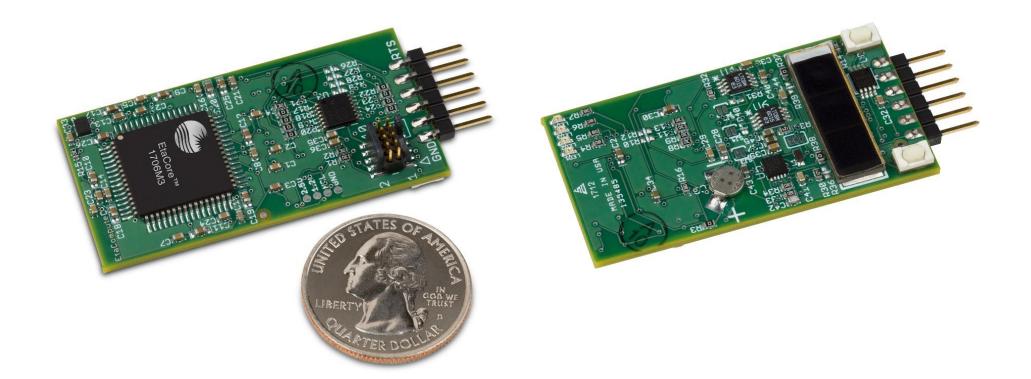

#### Energy Harvested Edge Node Based on our fully self timed Cortex M3.

## Demonstration

**Summary** Where can this technology go, all the way to neuromorphic machine learning at the edge with unsupervised learning

- Unique digital technology that enables always-on sensor nodes

- Enable more processor MIPS at much lower power consumption

- Longer battery life, small size sensor nodes

- We deliver SoC, turnkey sensor boards

# THANK YOU! David C. Baker, Ph.D. dave@etacompute.com cell: 512-585-5927