# A Perpetuum Mobile 32bit CPU on 65nm SOTB CMOS Technology with Reverse-Body-Bias Assisted Sleep Mode

Shiro Kamohara<sup>1</sup>, Nobuyuki Sugii<sup>1</sup>, Koichiro Ishibashi<sup>2</sup>, Kimiyoshi Usami<sup>3</sup>, Hideharu Amano<sup>4</sup>, Kazutoshi Kobayashi<sup>5</sup>, and Conq-Kha Pham<sup>2</sup>

<sup>1</sup>Low-power Electronics Association & Project (LEAP), Tsukuba, Japan, <sup>2</sup>The University of Electro-Communications, Tokyo, Japan, <sup>3</sup>Shibaura Institute of Technology, Tokyo, Japan, <sup>4</sup>Keio University, Yokohama, Japan, <sup>5</sup>Kyoto Institute of Technology, Kyoto, Japan

#### What is MEP (Minimum Energy Point) operation?

Any transistor should work under the condition; "lowest energy per operation"

# Big wall for MEP operation: Variability

Large Vth variability caused by RDF deteriorate the trade-off between  $V_{min}$  and standby leakage

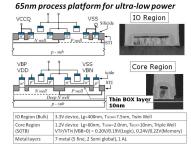

## SOTB (Silicon On Thin Buried Oxide)

SOTB drastically relax the trade-off between  $V_{min}$ and the standby leakage by two mechanism

## Mechanism of MEP operation via SOTB

## Target of SOTB to realize IoT world

Our goal is the 1/10 X reduction of an active power and the standby current to realize IoT world

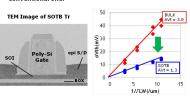

# Extreme low V., variability by SOTB

Our 65nm SOTB core transistor shows the ectreme variability reduction of 1/3 in comparison with

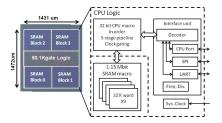

# CPU Chip Photomicrograph and Structure

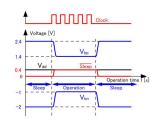

# Control method of CPU test chip

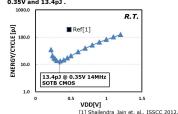

# Energy per Cycle Value of CPU

SOTB enable our test chip of a MEP operation of

0.35V and 13.4pJ .

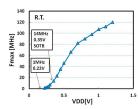

#### Maximum Operating Frequency of CPU

Even for a MEP operation, our test chip show  $\emph{F}_{max}$  of 14MHz and V<sub>min</sub> is 0.22V.

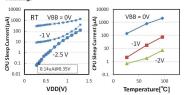

# **CPU Sleep Current**

Back bias control the standby leakage of more than 3 order and it makes the system a free for thermal

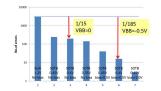

# Reliability benefit for SOTB

Soft error immunity of FF for SOTB are less than 1FIT, while those for Bulk are more than 100FIT.

# **CONCLUSIONS**

- · Perpetuum computing 32bit CPU is demonstrated with 65nm SOTB and back bias technology.

- · 13.4 pJ/cycle operating minimum energy, 0.14µA sleep current is attained.

- · The CPU operates eternally with ambient light indoor.

#### **Acknowledgments**

This work is supported by New Energy and Industrial Technology Development Organization and Ministry of Economy, Trade, and Industry of Japan.

Staffs of Renesas Electronics Corporation for chip fabrication

Universities and national institute for electrical characterization of devices, circuit design, and silicon verification:

Keio University

Kyoto Institute of Technology

Kvoto University Osaka University

Shibaura Institute of Technology

The National Institute of Advanced Industrial Science and

Technology (AIST)

The University of Electro-Communications

The University of Tokyo Tokyo University of Science