# Proceedings

Revised September 7, 2012

Copyright © HOT CHIPS, 2012. All rights reserved. All trademarks property of their respective owners.

#### Conference Day 1 Tuesday, August 28, 2012

|                                                                                                                                                                                               |                                                                                                                                                                                                                                    |                                                     |                                                                                                 | Γ                                           |                                                                                                              |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| 8:30 – 8:45am                                                                                                                                                                                 |                                                                                                                                                                                                                                    | Opening Remarks                                     |                                                                                                 | Christos Kozyrakis & Rumi Zahir             |                                                                                                              |  |

| 8:45 – 10:15am                                                                                                                                                                                |                                                                                                                                                                                                                                    | Session 1                                           |                                                                                                 | Microprocessors                             |                                                                                                              |  |

| Power Management of the Third Generation In<br>Architecture formerly codenamed Ivy Bridge<br>AMD's "Jaguar": A next generation low power ><br>proAptiv: Efficient Performance on a Fully-Synt |                                                                                                                                                                                                                                    | x86 core                                            | Sanjeev Jahagirdar, <b>Intel</b><br>Jeff Rupley, <b>AMD</b><br>Ranganathan Sudhaka, <b>MIPS</b> |                                             |                                                                                                              |  |

| 10:15 – 1                                                                                                                                                                                     | 10:45am                                                                                                                                                                                                                            | Break                                               | Student po                                                                                      | ster presentation                           | S                                                                                                            |  |

| 10:45 – 12:15pm                                                                                                                                                                               |                                                                                                                                                                                                                                    | Session 2                                           |                                                                                                 | Fabrics & Interconnects                     |                                                                                                              |  |

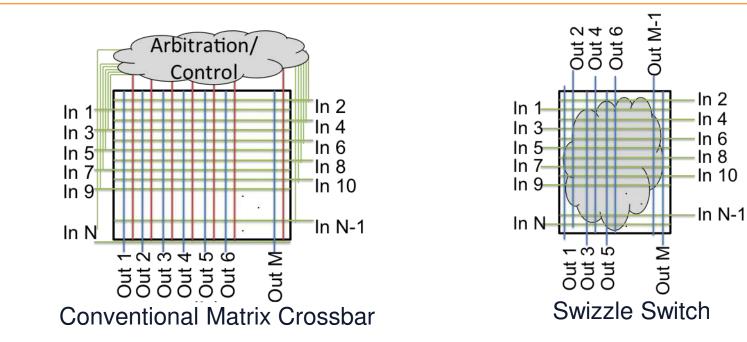

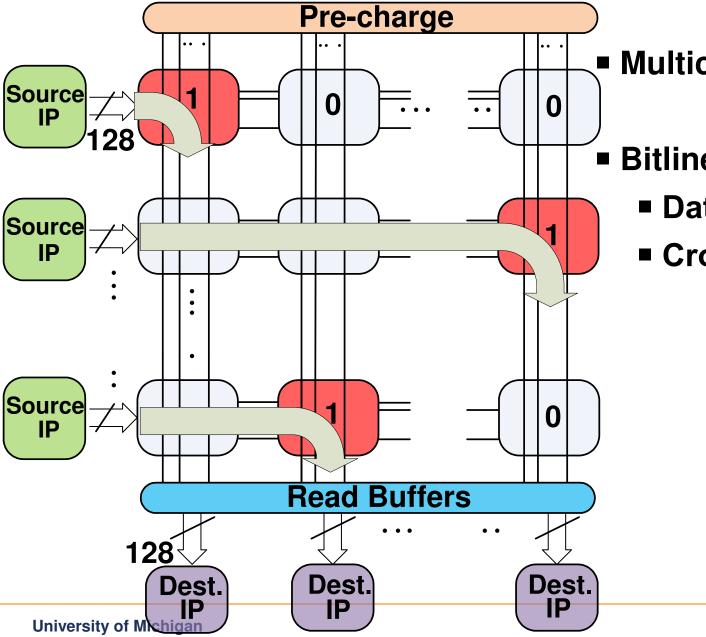

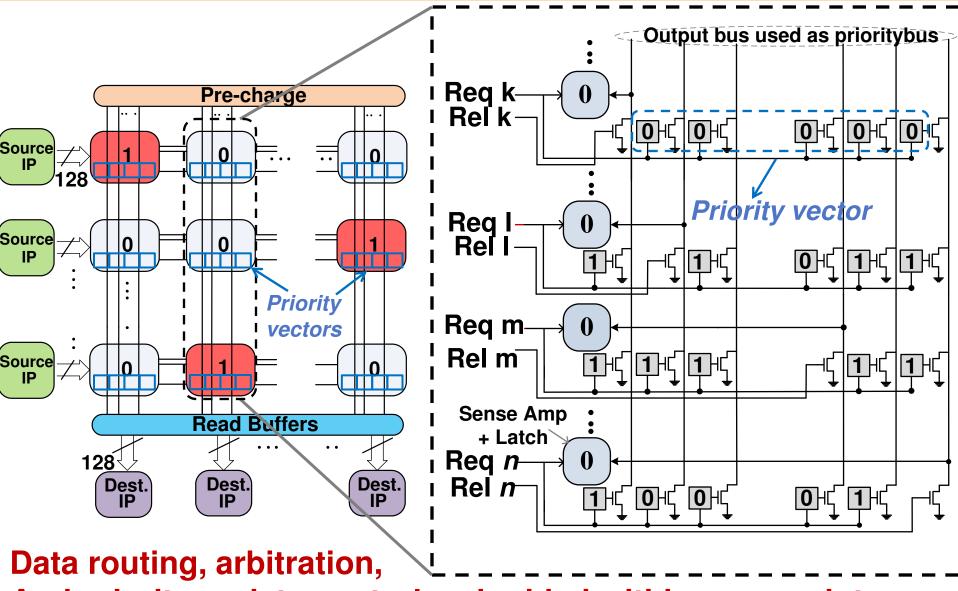

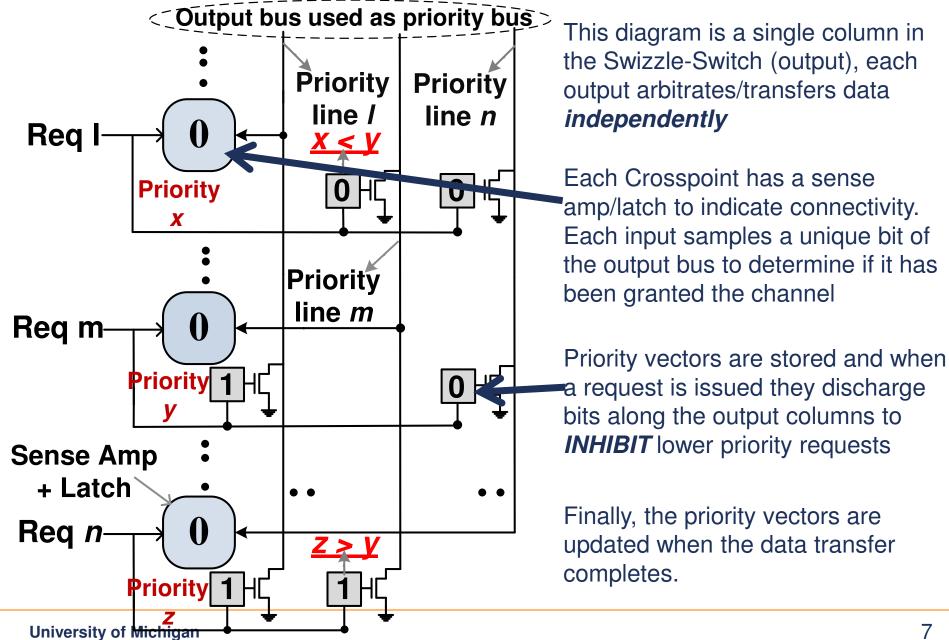

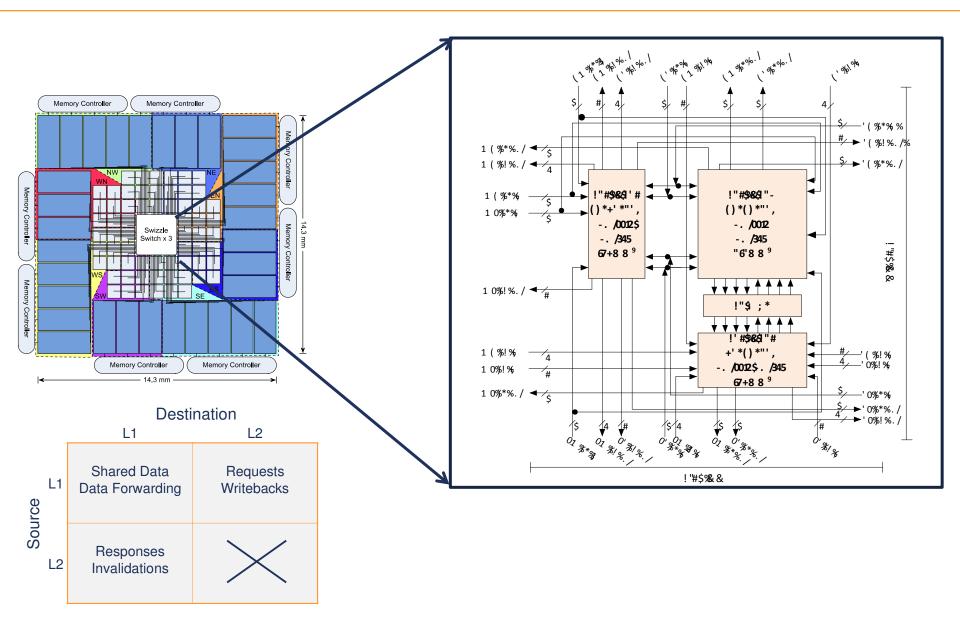

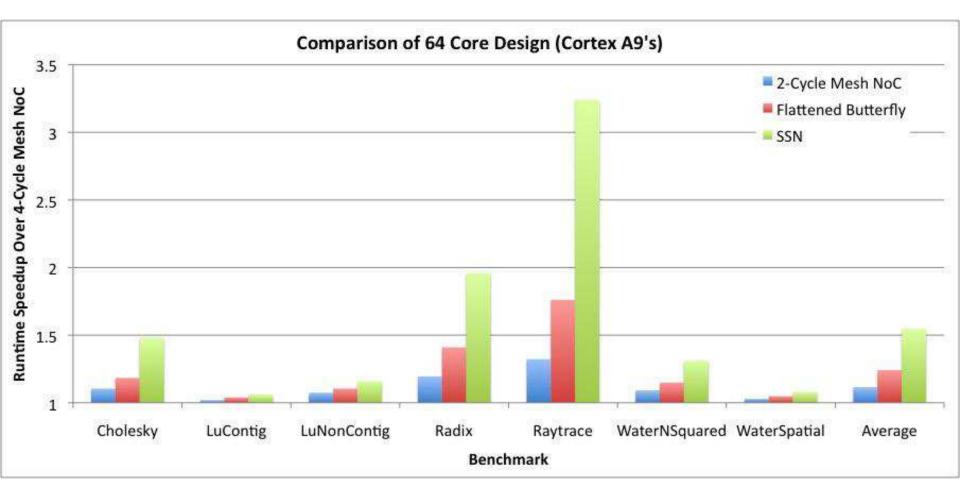

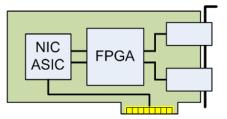

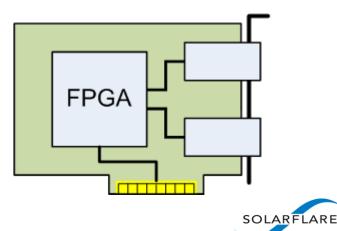

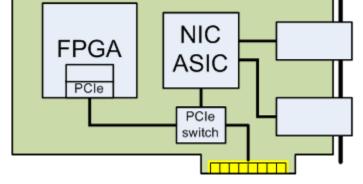

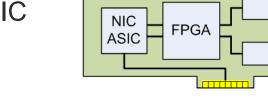

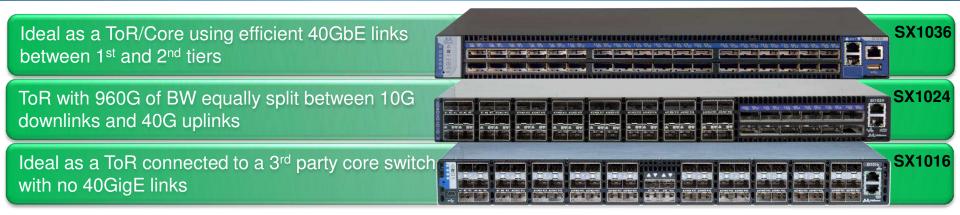

| S<br>F                                                                                                                                                                                        | ystems<br>PGA Augmente                                                                                                                                                                                                             | d ASICs: The Ti                                     | me Has Com                                                                                      | Crossbar for NoC<br>e<br>vitch Architecture | Ronald Dreslinski <b>, Michigan</b><br>David Riddoch, <b>Solarflare</b><br>Diego Crupnicoff, <b>Mellanox</b> |  |

| <b>12:15 –</b> 1                                                                                                                                                                              | 1:30pm                                                                                                                                                                                                                             | Lunch                                               |                                                                                                 |                                             |                                                                                                              |  |

| 1:30 – 2:                                                                                                                                                                                     | :30pm                                                                                                                                                                                                                              | Keynote 1                                           | The Surrou                                                                                      | Ind Computer Era                            |                                                                                                              |  |

| М                                                                                                                                                                                             | Mark Papermaster, CTO, AMD                                                                                                                                                                                                         |                                                     |                                                                                                 |                                             |                                                                                                              |  |

| 2:30 – 2:                                                                                                                                                                                     | :50pm                                                                                                                                                                                                                              | Break                                               | Student po                                                                                      | ster presentation                           | S                                                                                                            |  |

| 2:50 – 4:                                                                                                                                                                                     | :20pm                                                                                                                                                                                                                              | Session 3 Many Core                                 |                                                                                                 |                                             | GPU                                                                                                          |  |

| A<br>In                                                                                                                                                                                       | MD "Trinity" AP<br>Itel® Many Integ                                                                                                                                                                                                | U                                                   | itecture -The                                                                                   | CN) Architecture<br>first Intel® Xeon<br>r) | Michael Mantor, <b>AMD</b><br>Sebstian Nussbaum, <b>AMD</b><br>George Chrysos, <b>Intel</b>                  |  |

| 4:20 – 4:50pm                                                                                                                                                                                 |                                                                                                                                                                                                                                    | Break                                               |                                                                                                 | Student poster presentations                |                                                                                                              |  |

| 4:50 – 5:50pm                                                                                                                                                                                 |                                                                                                                                                                                                                                    | Session 4                                           |                                                                                                 | Multimedia & Im                             | aging                                                                                                        |  |

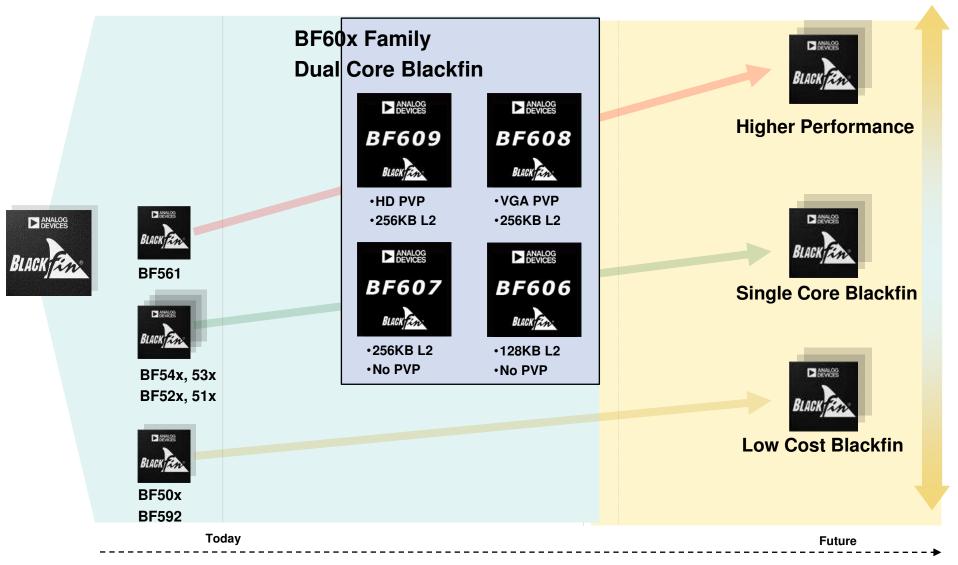

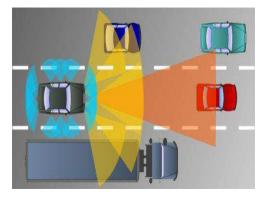

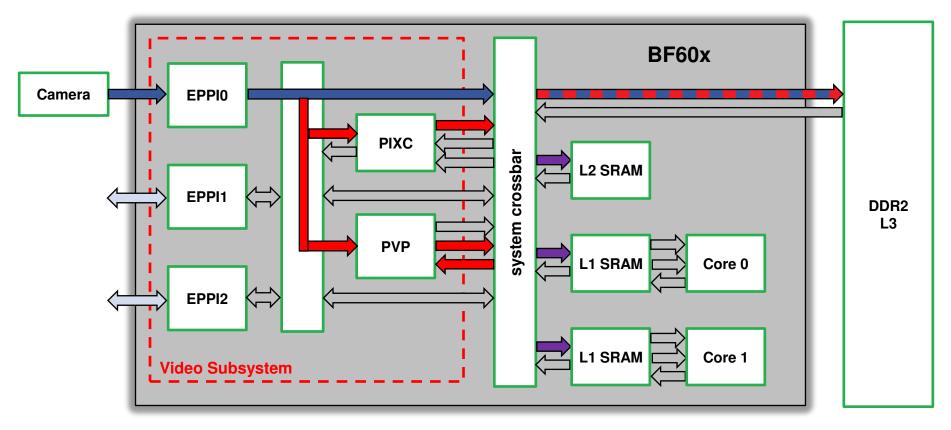

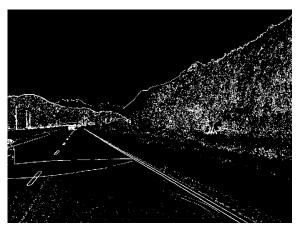

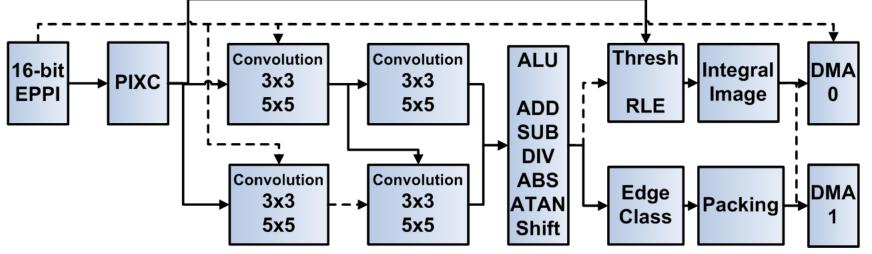

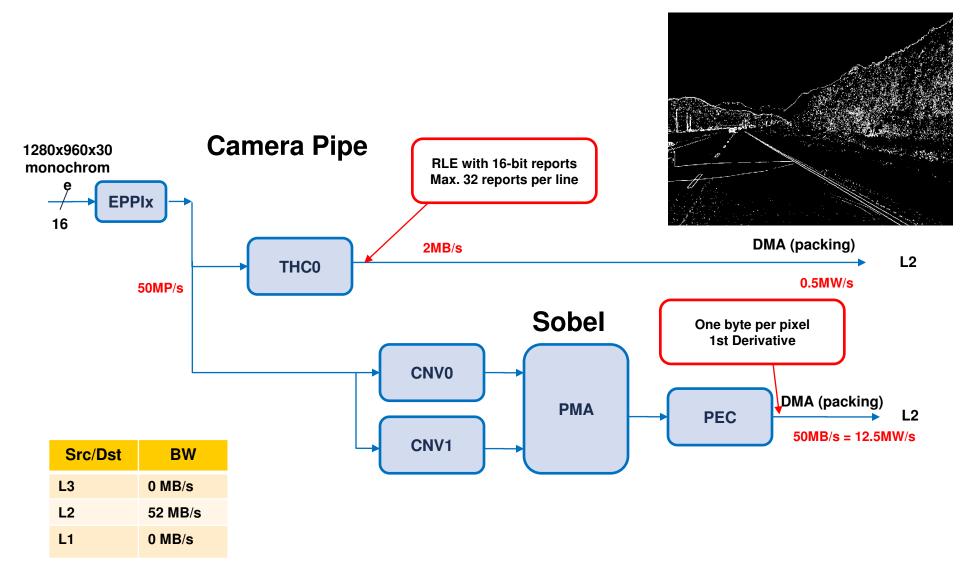

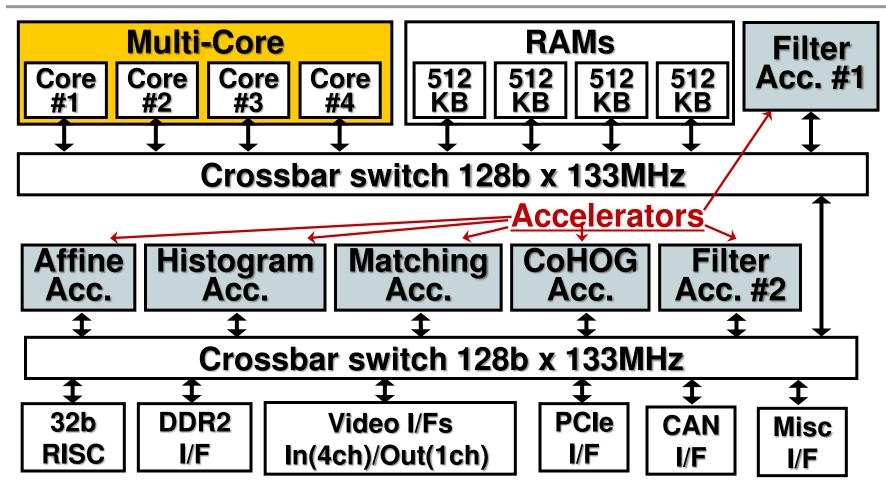

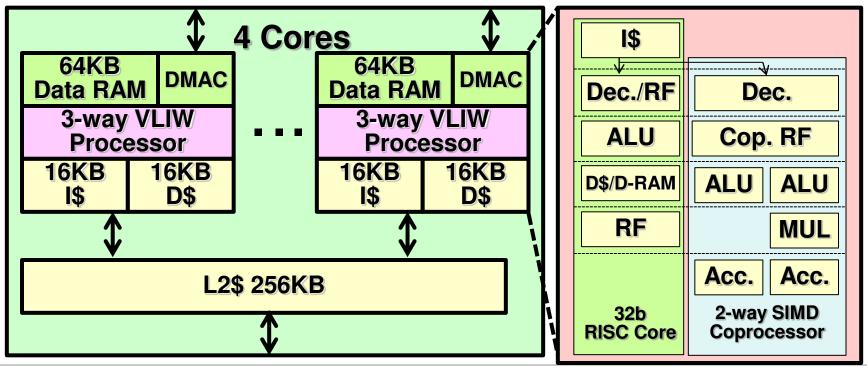

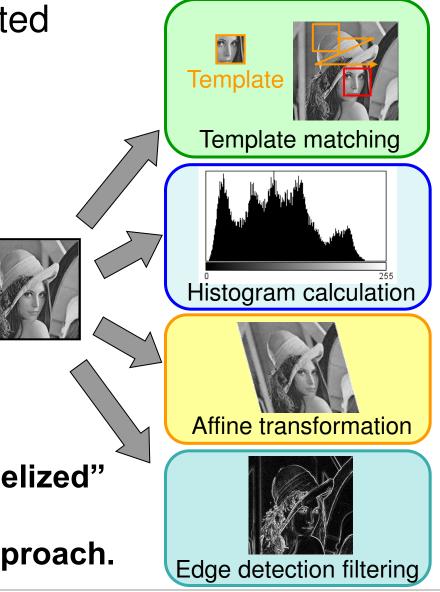

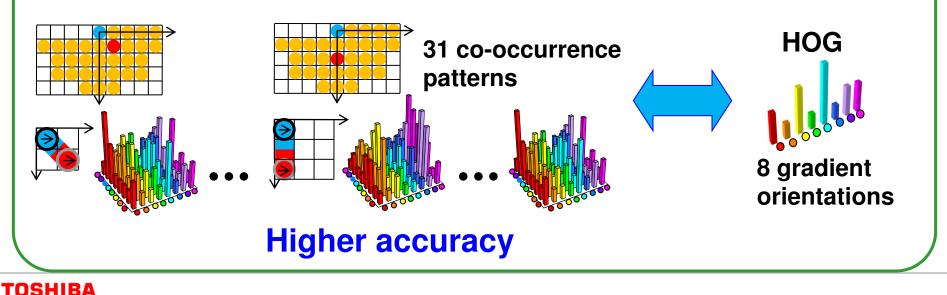

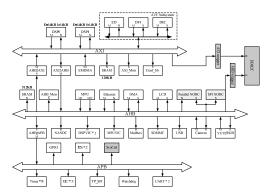

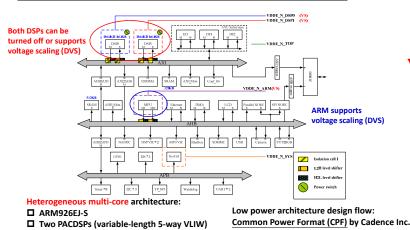

| Pi<br>m<br>Vi                                                                                                                                                                                 | ADI's Revolutionary BF60x Vision Focused Digital Signal<br>Processor System On Chip : 25 Billion Operations/Sec @ 80<br>mW and Zero Bandwidth<br>Visconti2 – A Heterogeneous Multi-Core SoC for Image-<br>Recognition Applications |                                                     |                                                                                                 |                                             |                                                                                                              |  |

| 5:50 – 6:                                                                                                                                                                                     | :50pm                                                                                                                                                                                                                              | Session 5                                           |                                                                                                 | Integration                                 |                                                                                                              |  |

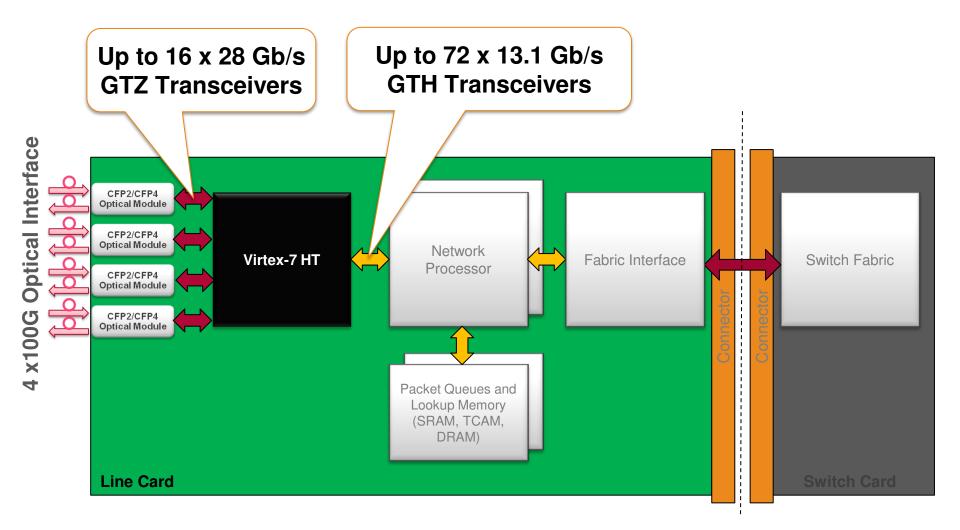

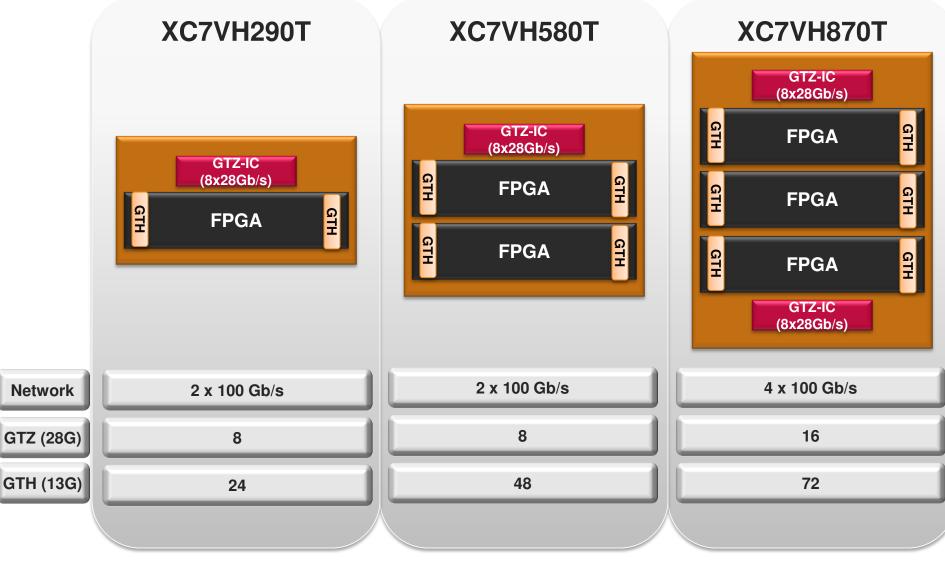

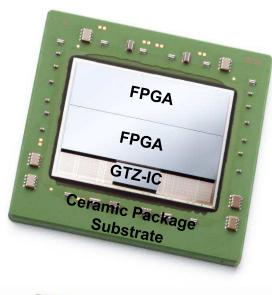

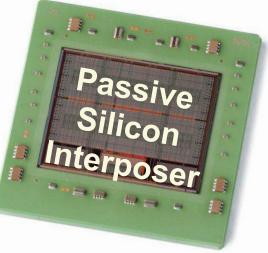

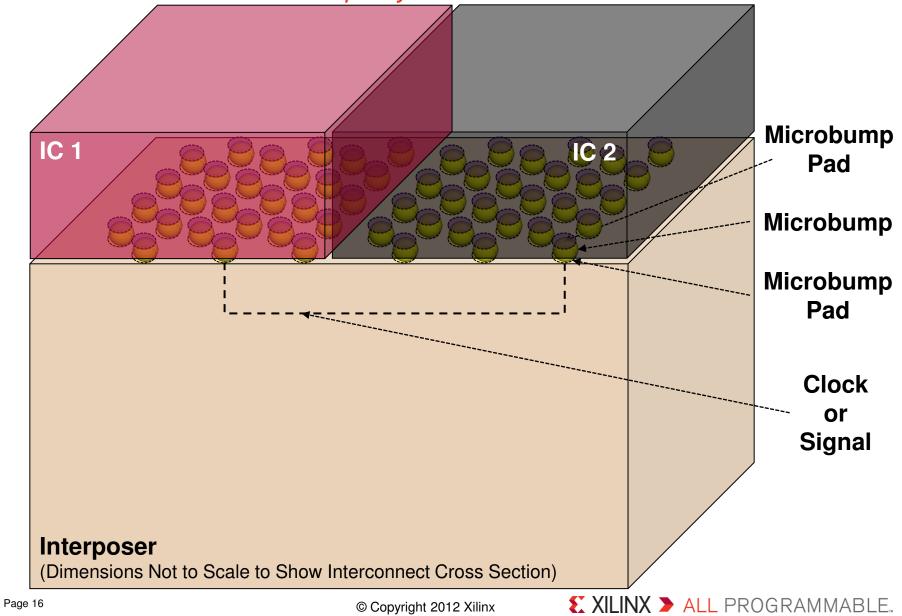

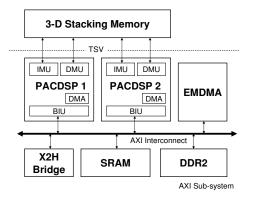

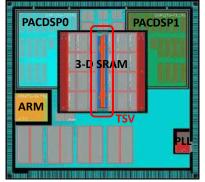

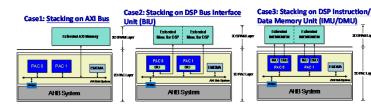

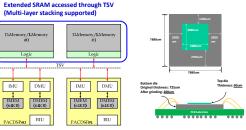

| F                                                                                                                                                                                             |                                                                                                                                                                                                                                    | Core, 3D Stacke<br>bps Transceivers<br>nterconnects |                                                                                                 |                                             | Ronald Dreslinski, <b>Michigan</b><br>Ephrem Wu, Suresh Ramalingam,<br><b>Xilinx</b>                         |  |

| 6:50 – 8:05pm Dinner                                                                                                                                                                          |                                                                                                                                                                                                                                    |                                                     |                                                                                                 |                                             |                                                                                                              |  |

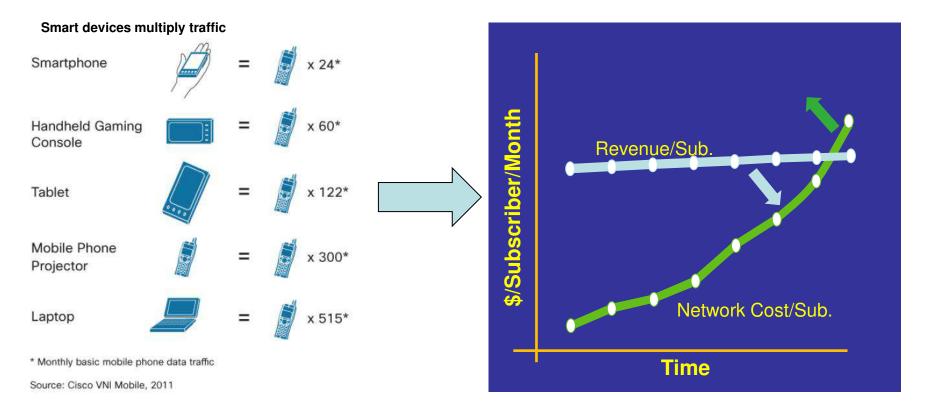

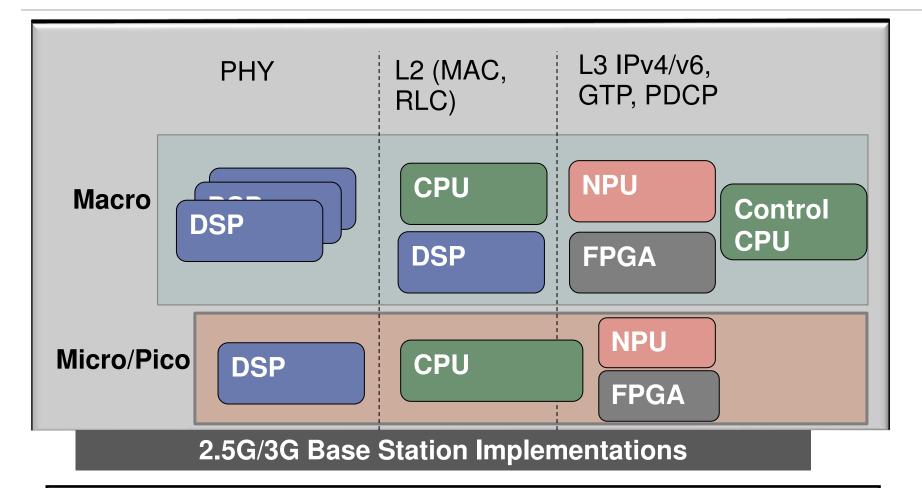

| 8:55 – 9:05pm                                                                                                                                                                                 |                                                                                                                                                                                                                                    | Keynote 2                                           |                                                                                                 | The Future of Wireless Networking           |                                                                                                              |  |

|                                                                                                                                                                                               | Marcus Weldon, CTO, Alcatel-Lucent                                                                                                                                                                                                 |                                                     |                                                                                                 |                                             |                                                                                                              |  |

#### Conference Day 2 Wednesday, August 29, 2012

| 8:45 – 10:15am Session 6 |                                                                                                                                                 |                                                                                                                   |                  | Technology & Scalability                |                                                                                                                                         |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

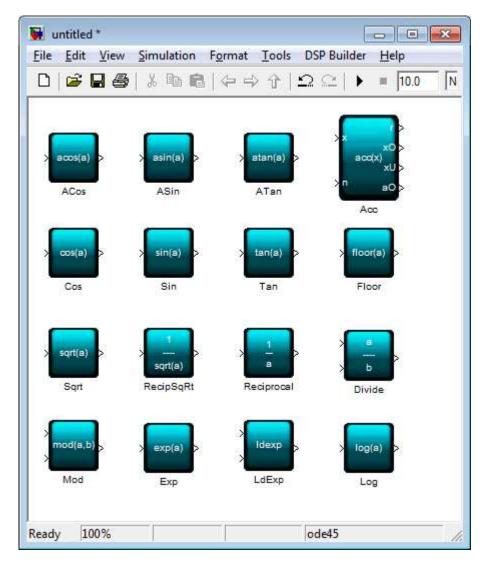

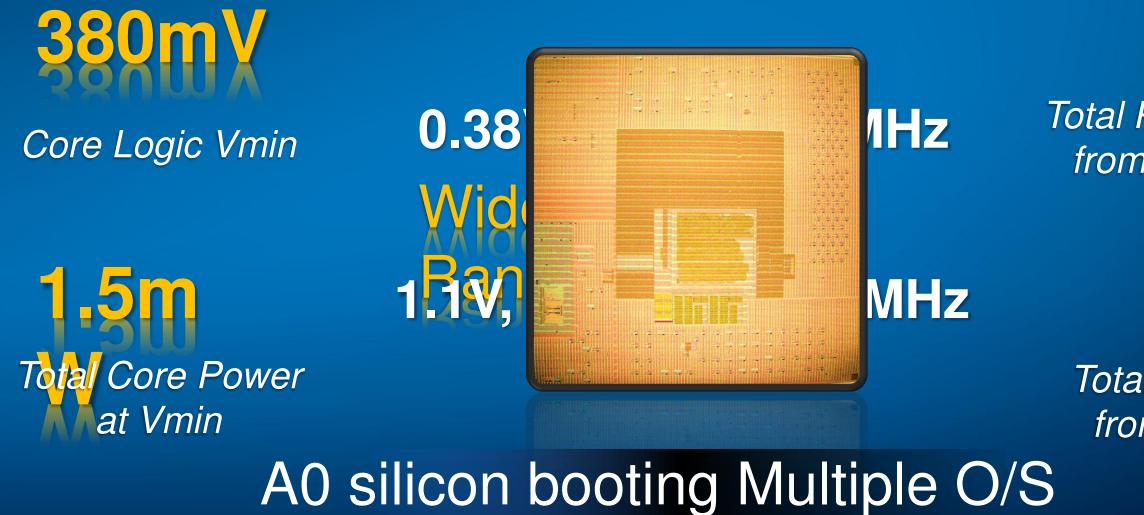

|                          | Floating-Point Processing using FPGAs<br>An IA-32 Processor with Wide Voltage Operating R<br>Reducing Transistor Variability For High Performan |                                                                                                                   |                  | ange in 32nm CMOS<br>ce Low Power Chips | Michael Parker, <b>Altera</b><br>Gregory Ruhl, <b>Intel</b><br>Robert Rogenmoser, <b>SuVolta</b>                                        |  |  |

| 10:15- 10:45am Break     |                                                                                                                                                 | Break                                                                                                             | eak              |                                         | Student poster presentations                                                                                                            |  |  |

| 10:45 – 12:15pm          |                                                                                                                                                 | Session 7                                                                                                         |                  | SOC                                     |                                                                                                                                         |  |  |

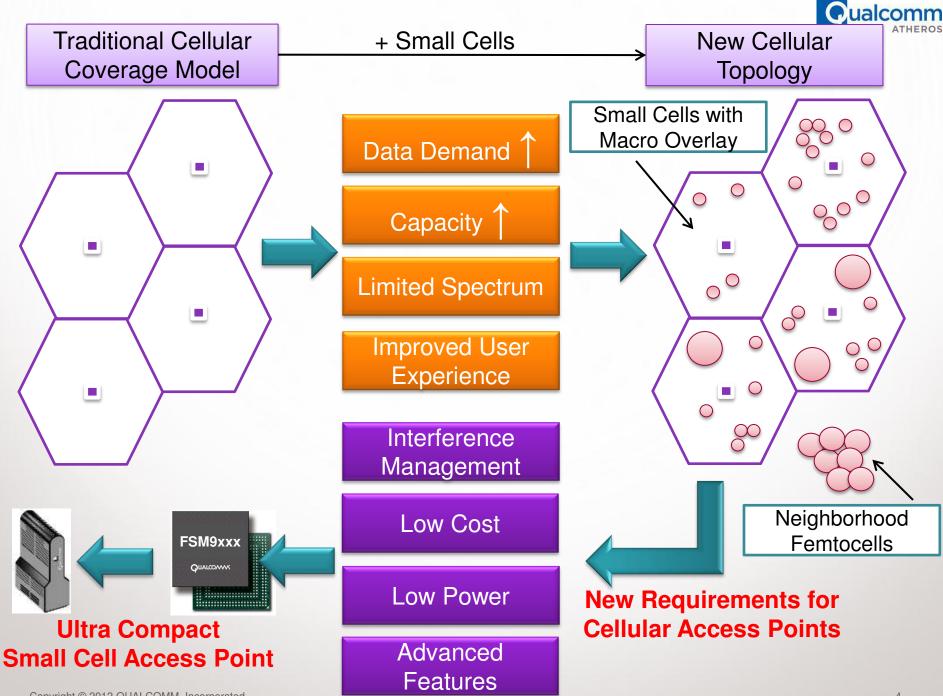

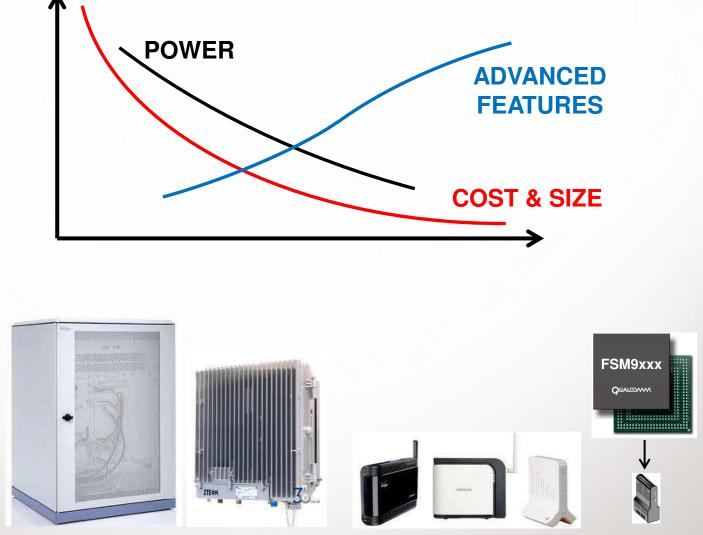

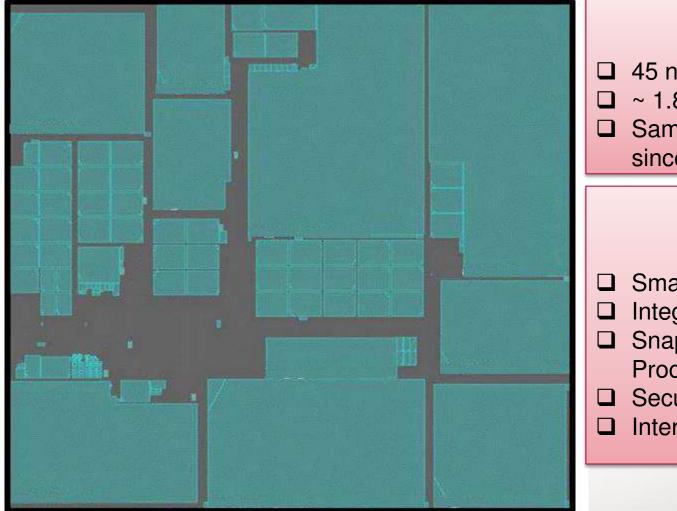

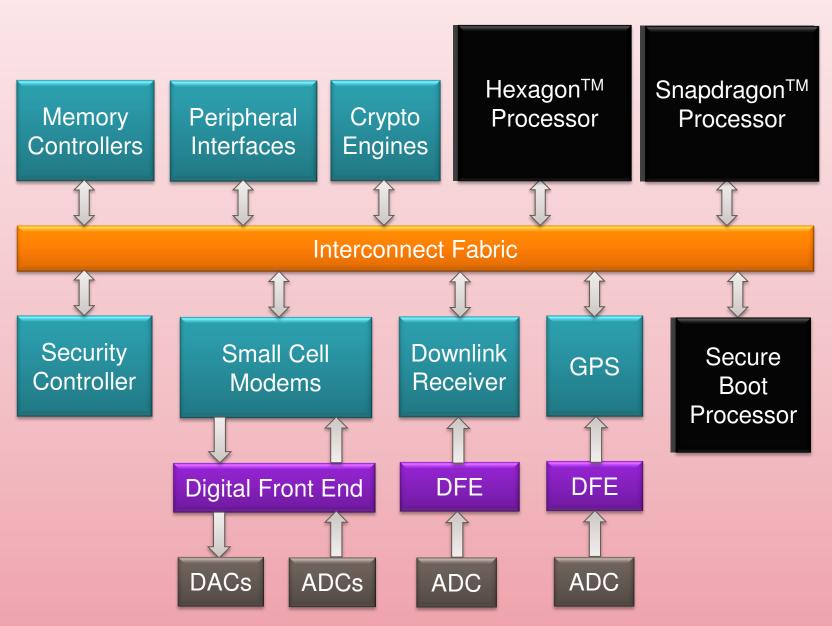

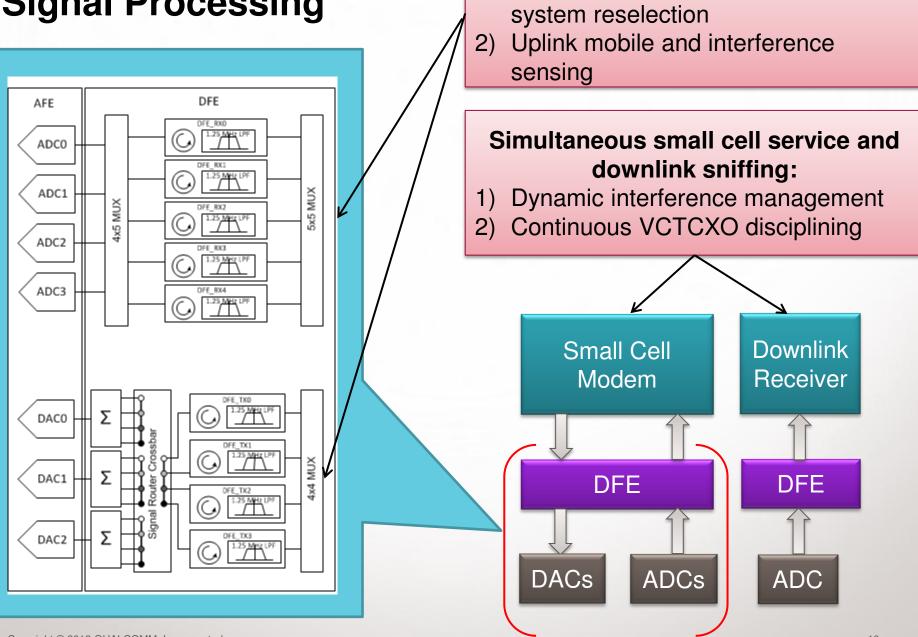

|                          | FSM <sup>™</sup> (Femtocell driven, chipset solu                                                                                                | and efficient single-chip s<br>Station Modem) – A high<br>ution for the small cell ma<br>one SOC – Intel's ATOM 2 | ly integ<br>rket | rated, performance                      | Kin-Yip Liu <b>, Cavium</b><br>Luca Blessent, <b>Qualcomm</b><br>Rumi Zahir, <b>Intel</b>                                               |  |  |

| 12:15                    | – 1:30pm                                                                                                                                        | Lunch                                                                                                             |                  |                                         |                                                                                                                                         |  |  |

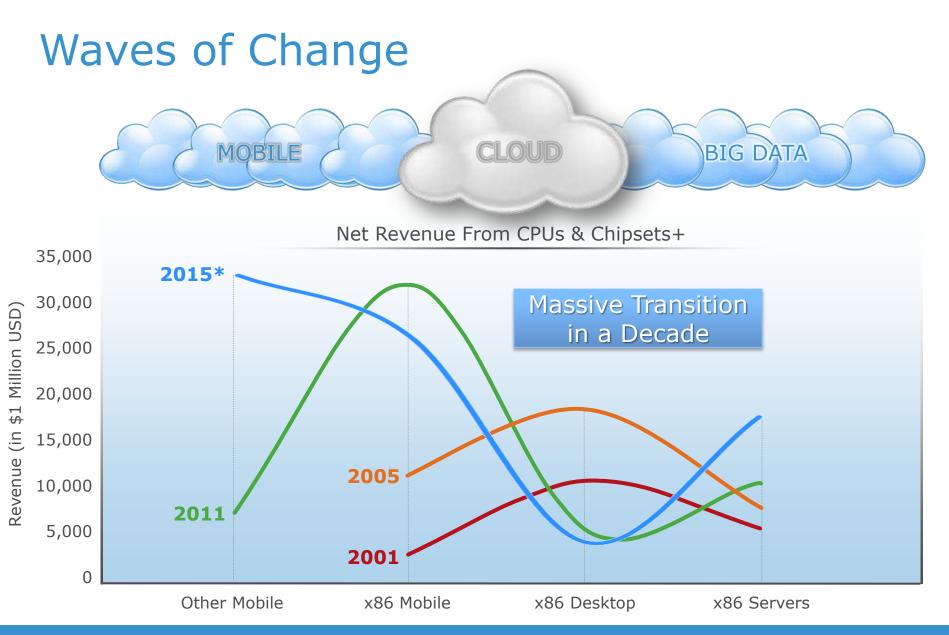

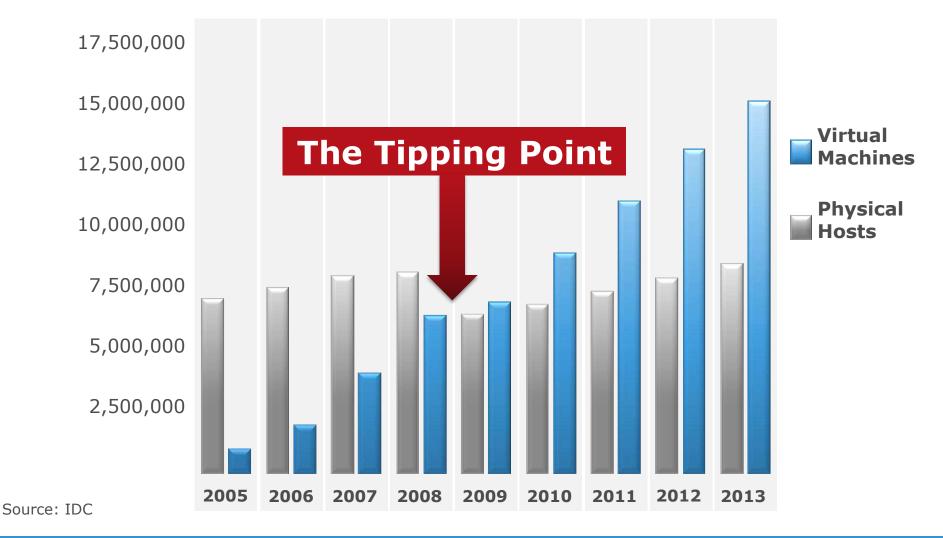

| 1:30                     | 1:30 – 2:30pm Keynote 3 Cloud                                                                                                                   |                                                                                                                   |                  | d Transforms IT, B                      | ig Data Transforms Business                                                                                                             |  |  |

|                          | Pat Gelsinger, COO Infrastructure Products, EMC [now CEO, VMWare]                                                                               |                                                                                                                   |                  |                                         |                                                                                                                                         |  |  |

| 2:30 – 2:50pm Break      |                                                                                                                                                 |                                                                                                                   |                  | Student poster presentations            |                                                                                                                                         |  |  |

| 2:50 – 4:20pm            |                                                                                                                                                 | Session 8                                                                                                         |                  | Data Center Chips                       |                                                                                                                                         |  |  |

|                          | POWER7+™: IBM's Next Generation POWER Mice<br>The Intel® Xeon® Processor E5 Family Architectur<br>and Performance                               |                                                                                                                   |                  |                                         | Scott Taylor, <b>IBM</b><br>Jeff Gilbert, Mark Rowland, <b>Intel</b>                                                                    |  |  |

|                          | X-Gene™: 64-bit /                                                                                                                               | ARM CPU and SoC                                                                                                   |                  |                                         | Gaurav Singh, Greg Favor, AMCC                                                                                                          |  |  |

| 4:20 -                   | 20 – 4:50pm Break                                                                                                                               |                                                                                                                   |                  | Student poster presentations            |                                                                                                                                         |  |  |

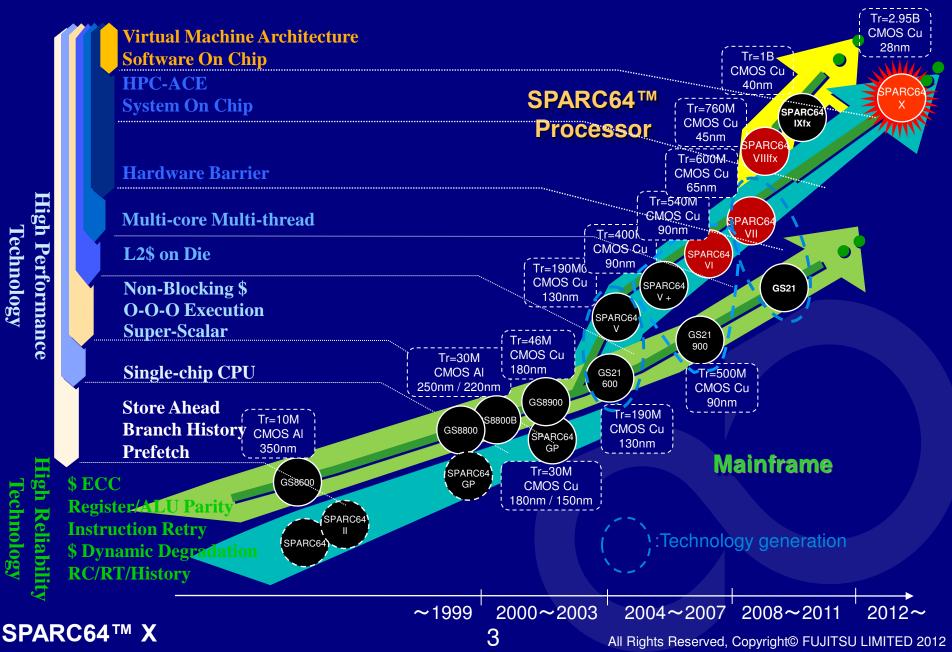

| 4:50 – 6:20pm            |                                                                                                                                                 | Session 9                                                                                                         |                  | Big Iron                                |                                                                                                                                         |  |  |

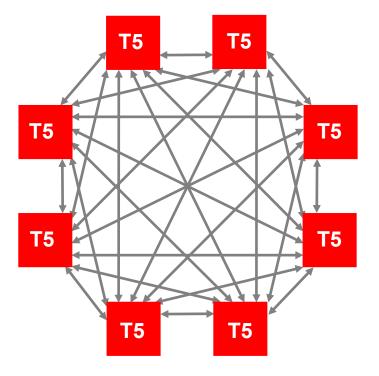

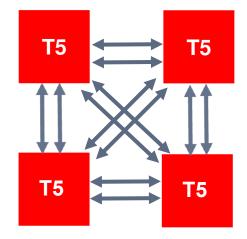

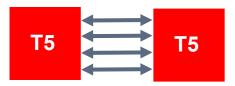

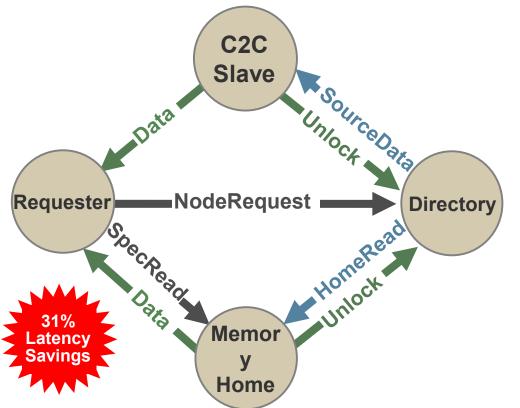

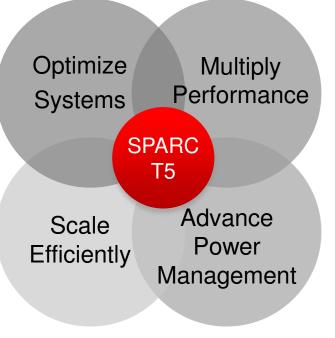

|                          | generation UNIX se<br>SPARC T5: 16-cor<br>Glueless 1-Hop Sc                                                                                     | e CMT Processor with                                                                                              | ·                |                                         | Takumi Maruyama, <b>Fujitsu</b><br>Sebastian Turullols, Ram<br>Sivaramakrishnan, <b>Oracle</b><br>Chung-Lung (Kevin) Shum, , <b>IBM</b> |  |  |

| 6:20 -                   | 6:20 – 6:30pm Closing Remarks                                                                                                                   |                                                                                                                   |                  |                                         | •                                                                                                                                       |  |  |

|                          |                                                                                                                                                 |                                                                                                                   |                  |                                         |                                                                                                                                         |  |  |

Copyright © HOT CHIPS, 2012. All rights reserved. All trademarks property of their respective owners.

|                                                                                                                         | POSTERS<br>On exhibit during Breaks                                                                                                                                                |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

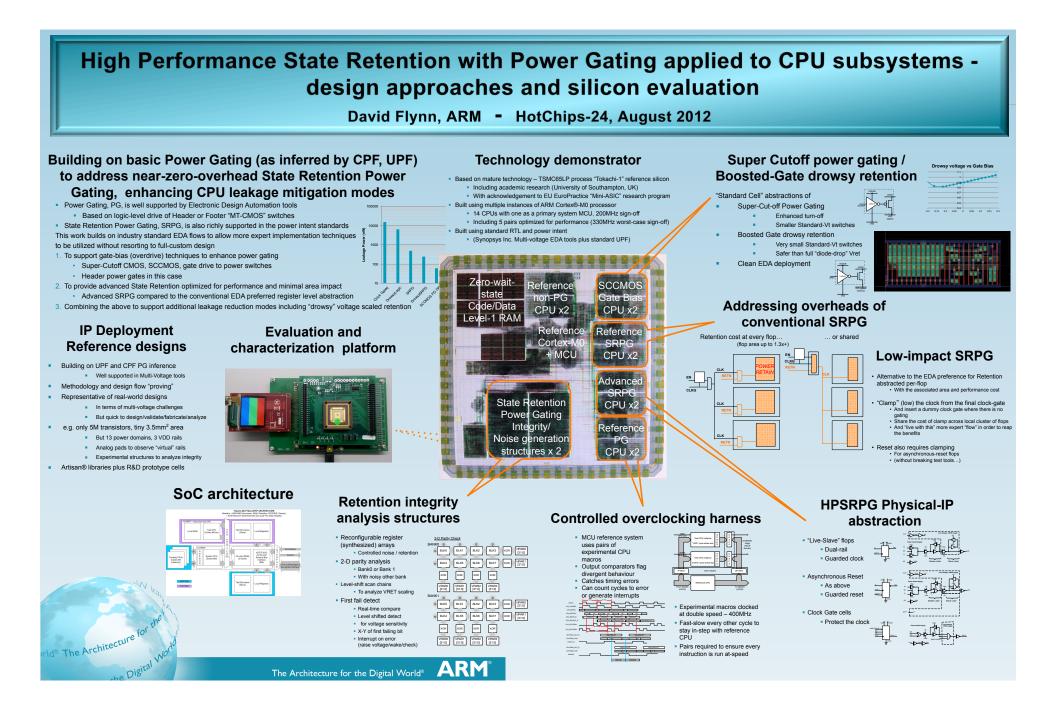

| High Performance State Retention with Power Gating applied to CPU subsystems – design approaches and silicon evaluation | David Flynn, Fellow, R&D <b>ARM Ltd</b> , Cambridge, UK                                                                                                                            |  |  |

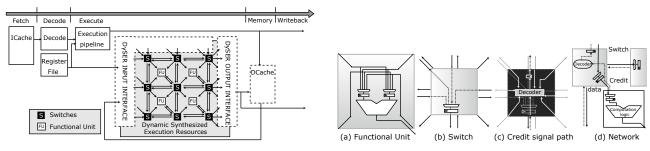

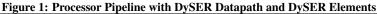

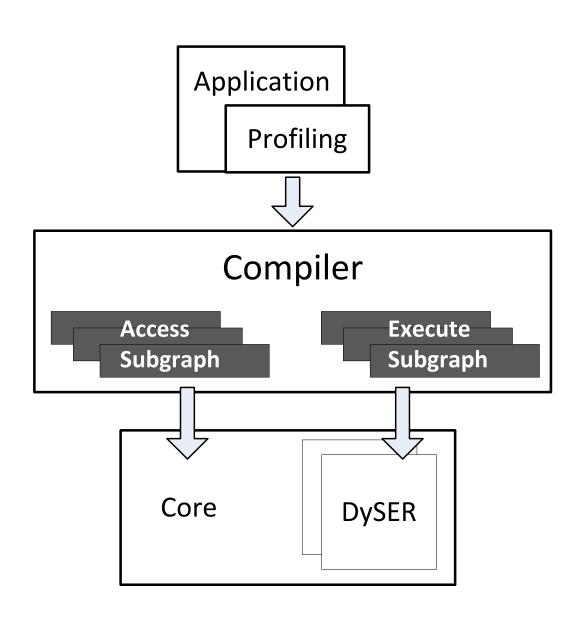

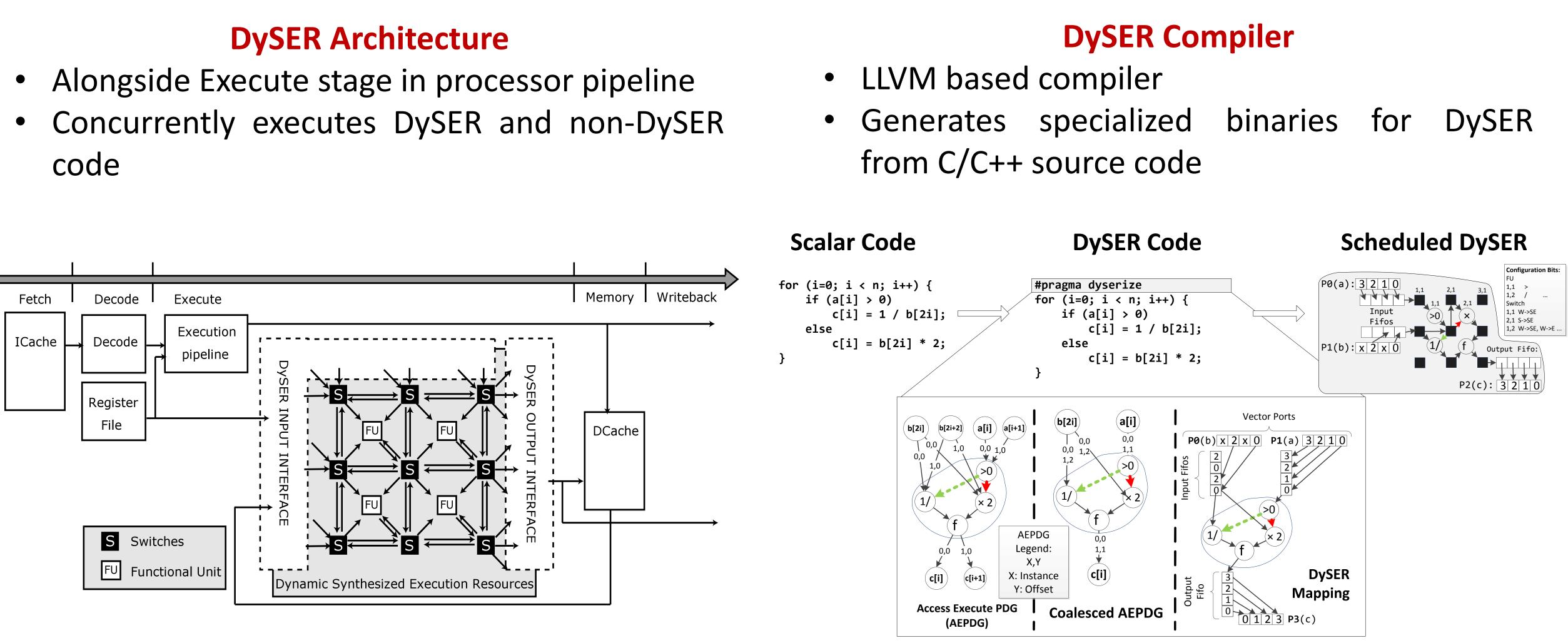

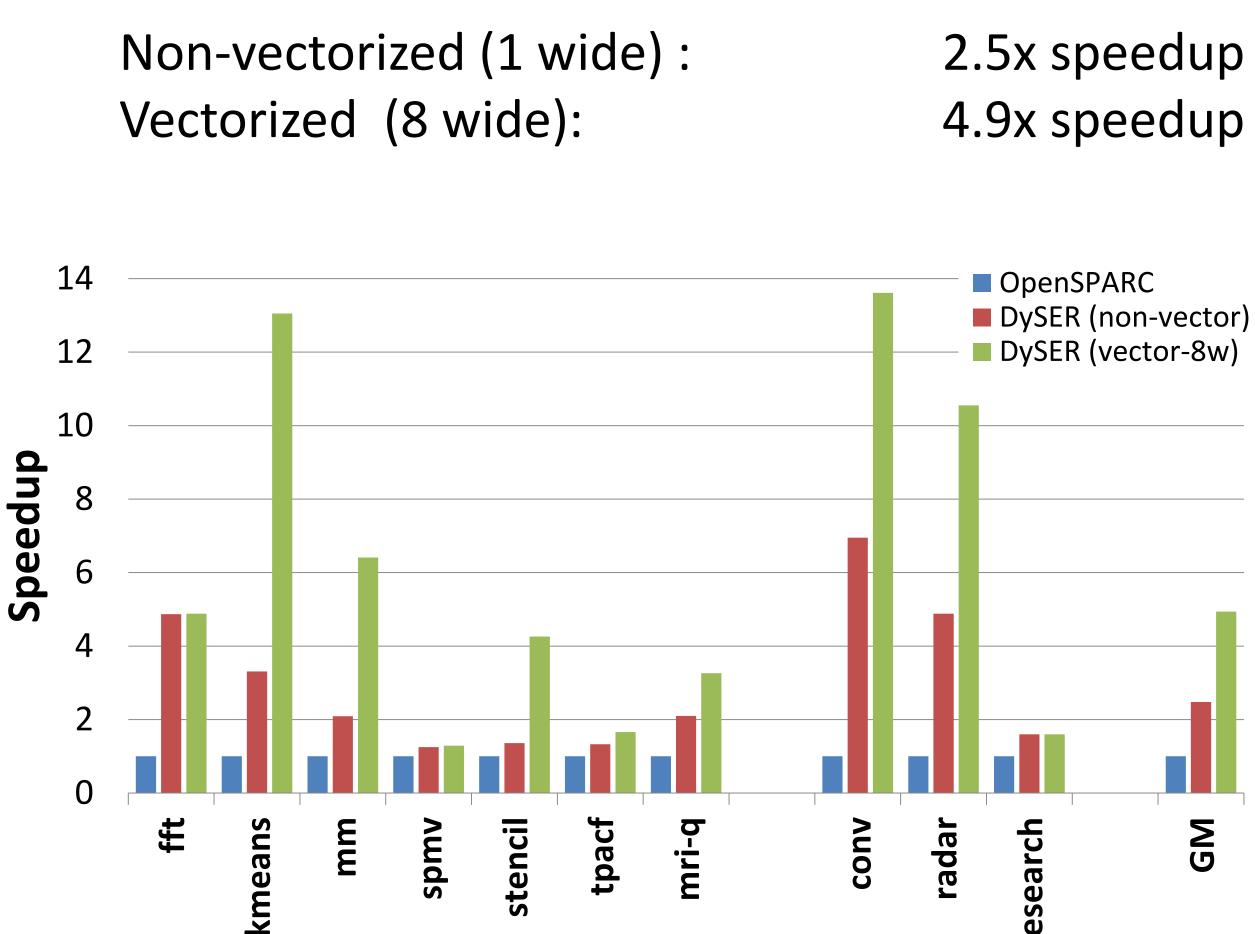

| Prototyping the DySER Specialization<br>Architecture with OpenSPARC                                                     | Jesse Benson, Ryan Cofell, Chris Frericks, Venkatraman<br>Govindaraju, Chen-Han Ho, Zachary Marzec, Tony<br>Nowatzki, Karu Sankaralingam<br><b>University of Wisconsin-Madison</b> |  |  |

| Low Power and High Performance 3-D Multimedia<br>Platform                                                               | Po-Han Huang, Chi-Hung Lin, Hsien-Ching Hsieh,<br>Huang-Lun Lin and Shing-Wu Tung<br>Information and Communications Research Lab.<br>Industrial Technology Research Institute      |  |  |

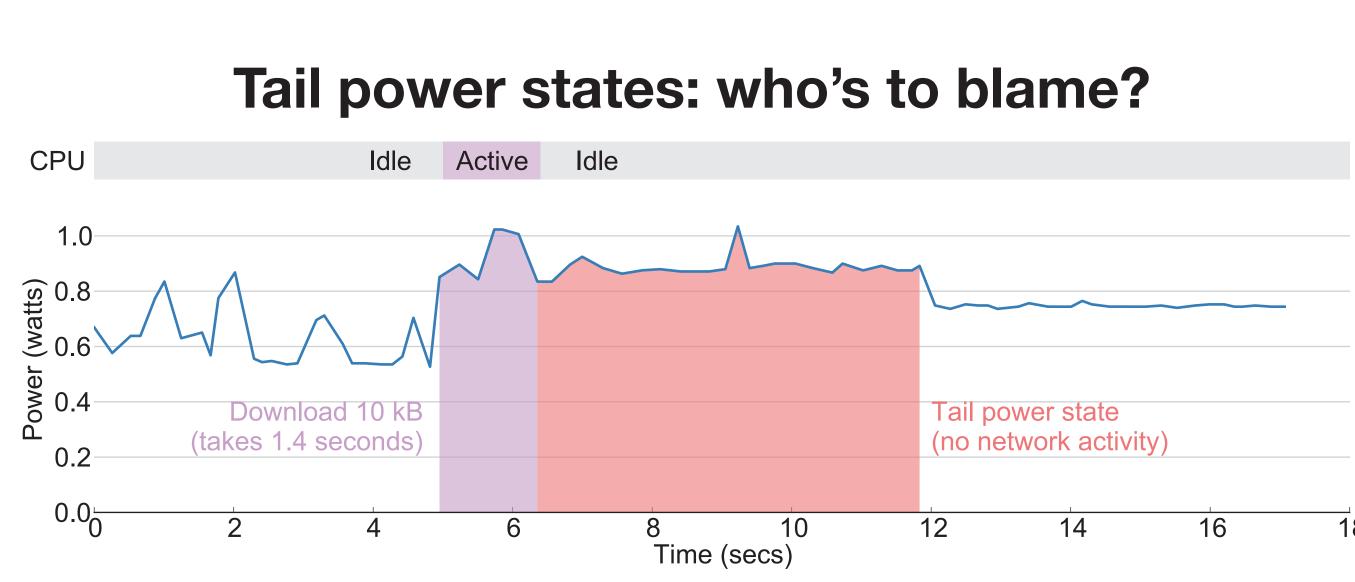

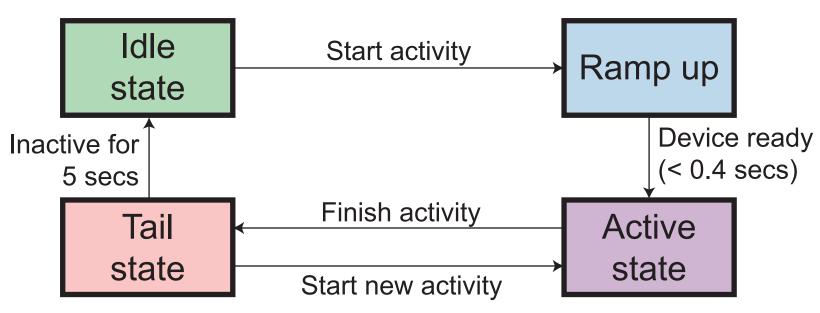

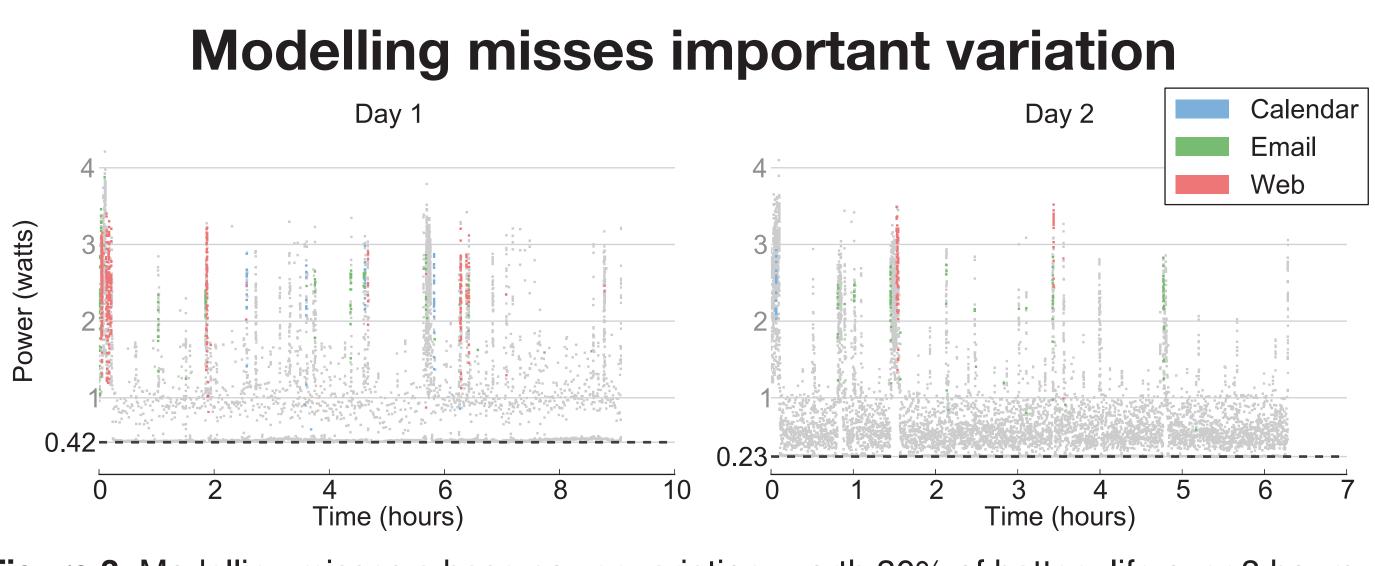

| The Model Is Not Enough: Understanding Energy<br>Consumption in Mobile Devices                                          | James Bornholt, Australian National University, Todd<br>Mytkowicz, Microsoft Research, Kathryn S. McKinley,<br>Microsoft Research                                                  |  |  |

| Efficient, Precise-Restartable Program Execution on Future Multicores                                                   | Gagan Gupta, Srinath Sridharan, and Gurindar S. Sohi,<br><b>University of Wisconsin-Madison</b>                                                                                    |  |  |

Copyright © HOT CHIPS, 2012. All rights reserved. All trademarks property of their respective owners.

August 27 - 29, 2012 Flint Center, Cupertino, CA

**A Symposium on High Performance Chips**

# Welcome to Hot Chips 24

Christos Kozyrakis & Rumi Zahir Program Committee Co-Chairs

### **Program Committee**

- Forest Baskett, NEA

- Pradeep Dubey, Intel

- Bob Felderman, Google

- Krisztian Flautner, ARM

- Anwar Ghuloum NVIDIA

- Christos Kozyrakis, Stanford

- Chuck Moore, AMD

- Sameer Nanavati, Qualcomm

- Don Newell

- Kunle Olukotun, Stanford

- Mitsuo Saito, Toshiba

- Alan Smith, UC Berkeley

- Guri Sohi, U. of Wisconsin

- Dean Tullsen, UCSD

- Rich Uhlig, Intel

- Fred Weber

- Rumi Zahir, Intel

### **Program Statistics**

- 54 submissions

- Each submission was reviewed by all PC members

- 25 accepted talks

- High-end & low-power cores, many core, graphics, server chips, multimedia SoCs, networking, ...

- 5 posters

- Poster session during morning & afternoon breaks

### Keynotes

- Marc Papermaster, CTO, AMD

- The Surround Computing Era

- Tuesday 8/28<sup>th</sup>, 1.30pm

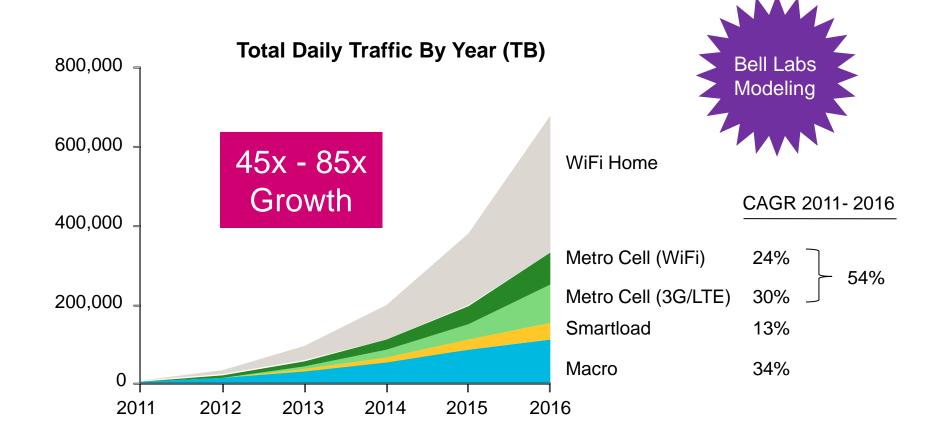

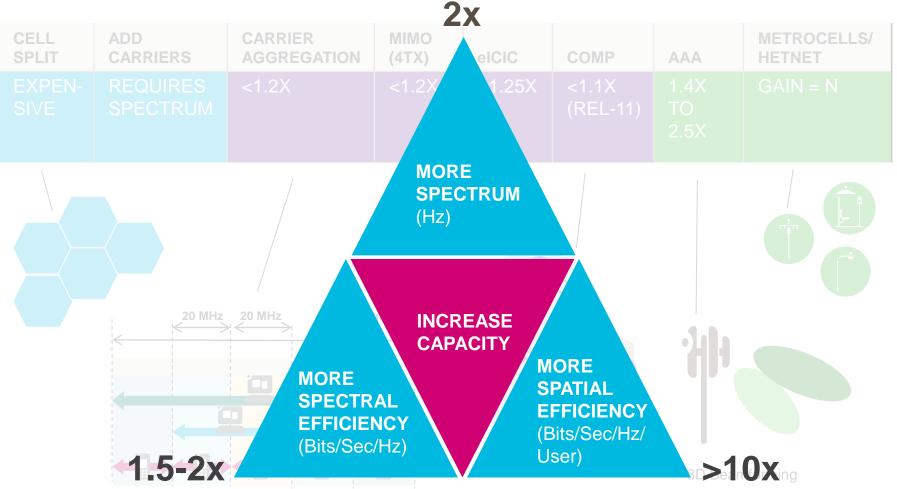

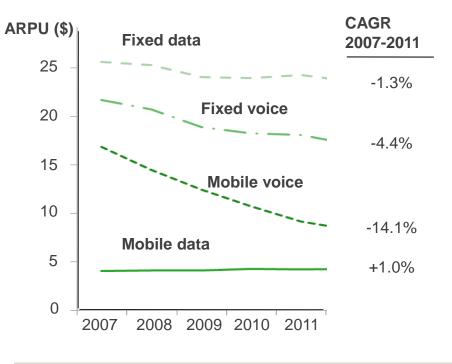

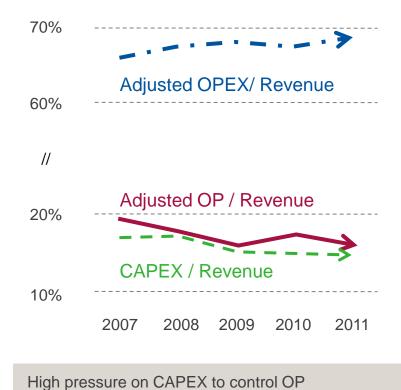

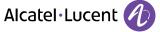

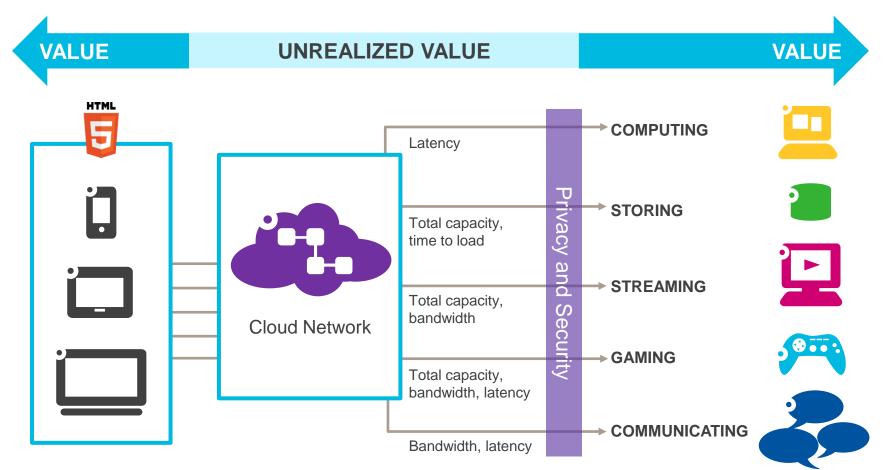

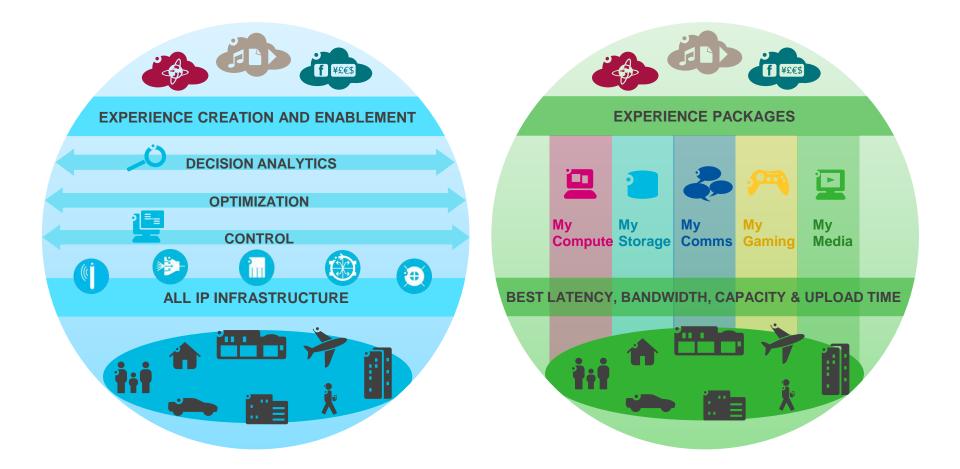

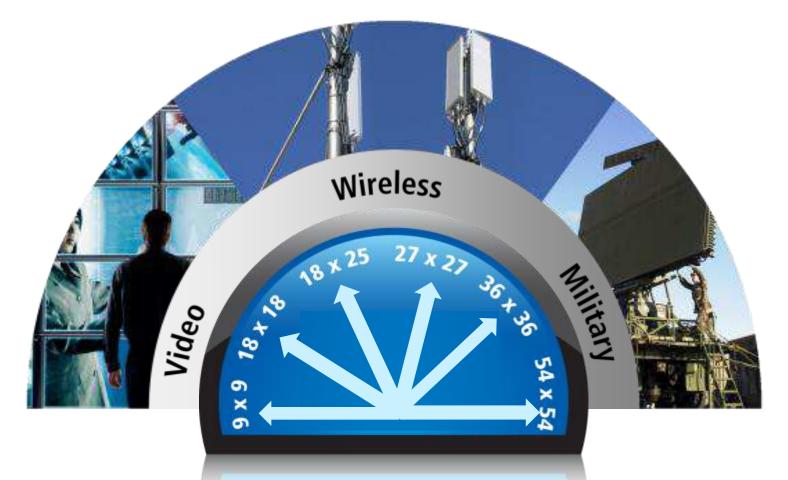

- Marcus Weldon, CTO, Alcatel-Lucent

- The Future of Wireless Networking

- Tuesday 8/28<sup>th</sup>, 8pm

- Pat Gelsinger, COO, EMC

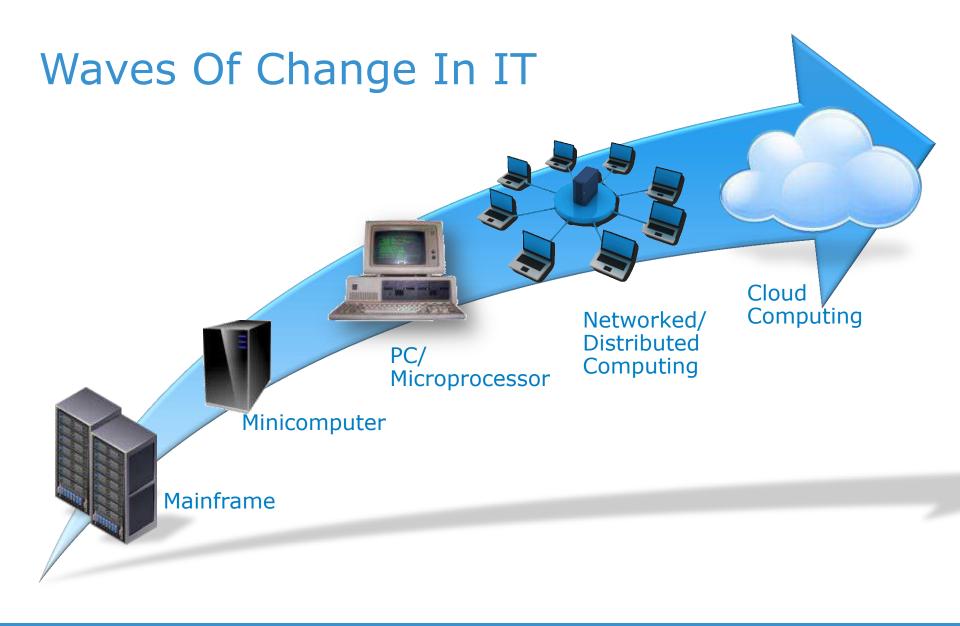

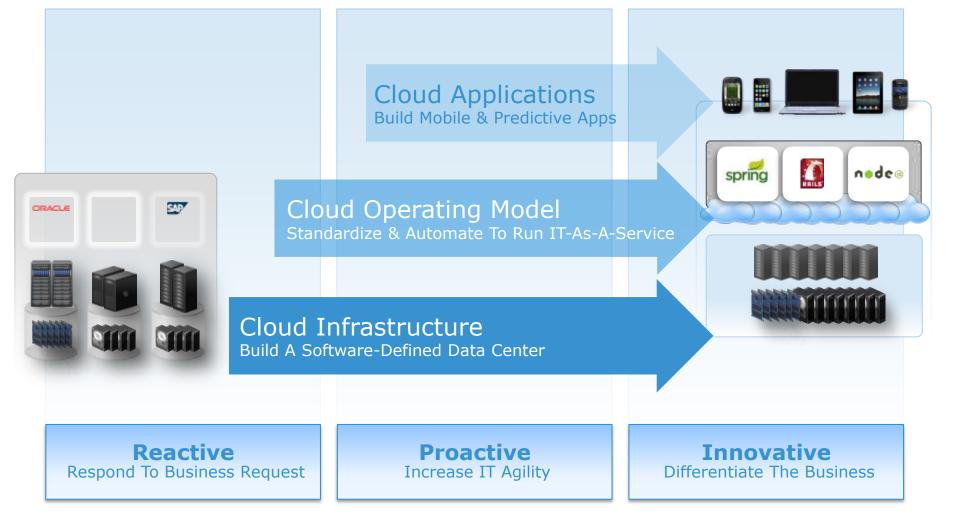

- Cloud Transforms IT, Big Data Transforms Business

- Wednesday 8/29<sup>th</sup>, 1.30pm

### **Tutorials**

- The Evolution of Mobile SoC Programming

- Organized by Niel Trevett

- Khronos, ArcSoft, eyeSight, Metaio, Sensor Platforms, the 11ers

- Die Stacking

- Organized by Liam Madden

- AMD, Amkor, Qualcomm, UMC, Xilinx

### Proceedings

- For registered attendees

- Talks, posters, and tutorials available on USB key

- Also available online for tablet users (http://hc24.local)

- Updated talks available online after the conference

- Including keynote talks and videos of talks

- Conference archives available online

- http://www.hotchips.org

## **Conference Etiquette**

• Silence your cellphones during sessions

- Question on technical talks

- Wait until the end of the talk

- Come to the microphone & start with name and affiliation

- Stick to technical questions please

- If there is a line, ask a single question

- For speakers: during the break before your talk

- Introduce yourself to your session chair

- Test your slides

### In Remembrance

#### **Chuck Moore**

#### John Nickolls

### **Enjoy Hot Chips 24**

On behalf of the Program Committee, we are pleased to welcome you to the 24<sup>th</sup> Annual Hot Chips Symposium.

We received fifty-four (54) submissions this year that covered nearly all areas of the semiconductor and computing systems industry. The seventeen-member committee carefully reviewed all submissions and selected the top twenty-five (25) that best represent the breadth and depth of our field. We also selected five (5) posters that represent emerging trends and important work in related technical areas. As usual, the conference features the latest processor designs for server and portable systems, multimedia and graphics, networking and telecommunications chips, and FPGA devices. The diverse program covers designs optimized for sub-threshold voltage operation all the way to designs exceeding 5GHz clock frequency. We are also happy to feature two excellent talks and four posters from academic projects.

Multi-core architectures and design for power efficiency remain the two most pervasive trends in the program. Nevertheless, specialization and heterogeneity are also emerging as important developments. Ten of the twenty-five talks in the program describe chips with multiple types of processing engines, programmable and fixed function. Heterogeneity is also the focus of the first tutorial that addresses the critical problem of software development for the heterogeneous multi-core chips in mobile devices. The second tutorial covers how die-stacking technology can improve latency, bandwidth, and system size, while preserving the benefits of heterogeneous manufacturing processes. Another exciting development this year is the appearance of chips that take established instruction sets beyond their traditional application domains. The program features talks on a smartphone chip based on the x86 ISA and a server chip based on ARM, in addition to talks on the latest designs based on the Power, SPARC, and MIPS instruction sets.

For the keynotes, we selected three exciting talks from leading figures in our industry. In the first keynote, Mark Papermaster will cover AMD's strategy towards heterogeneous systems and accelerated computing. In the second keynote, Marcus Weldon will discuss the future of wireless telecommunications and its implications to the semiconductor industry. The final keynote by Pat Gelsinger will discuss how cloud computing and big data are transforming the whole IT industry.

The high quality of this year's program is the direct result of the effort of the members of the program committee, all of whom worked hard to solicit, select, and improve presentations. We would also like to thank Liam Madden, Niel Trevett, Ralph Wittig, and Anwar Ghuloum for putting together the tutorials. The members of the organizing committee worked equally hard to provide the best possible setup for a successful symposium, overcoming several difficulties associated with the new location. An incredible amount of effort has gone into organizing tasks that we all take for granted such as high quality proceedings, online registration, and meals. Finally, we acknowledge the effort of all speakers, without whom there would be no conference.

Finally, we would like to recognize the contributions of Chuck Moore and John Nickolls that passed away recently. In addition to being leading visionaries and innovators in our field, Chuck and John were exemplary members of the Hot Chips community that contributed greatly through multiple roles. They will be missed.

Christos Kozyrakis and Rumi Zahir Program Co-Chairs Hot Chips 24 August 2012

#### Power Management of the Third Generation Intel Core Micro Architecture formerly codenamed Ivy Bridge

Sanjeev Jahagirdar Varghese George, Inder Sodhi, Ryan Wells

# Contents

> Ivy Bridge Overview > Power Scaling & Efficiency > Idle power Management Configurable TDP > Clocking > Additional Information

# Contents

Ivy Bridge Overview > Power Scaling & Efficiency > Idle power Management > Configurable TDP > Clocking > Additional Information

#### Intel's Tick-Tock Philosophy

#### Tock Processors

- Provide substantial microarchitecture improvement...

- ...on existing manufacturing process

#### Tick Processors

- Retain existing microarchitecture, ...

- ...but utilize next generation fabrication technology to drive high volume and low product cost

#### □ The Tock: *Sandy Bridge*

- Brought new ring/LLC microarchitecture

- Integrated Graphics on ring

- Integrated North Bridge ("System Agent"), including memory controller

#### □ The Tick: Ivy Bridge

- Process lead vehicle: Intel's 22nm process node

- The Caveat:

- Some Ivy Bridge areas have substantial (tock-like) change (Graphics)

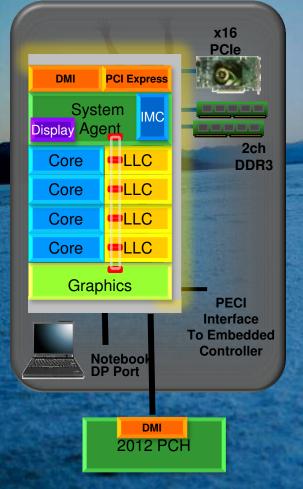

### Ivy Bridge – the 1<sup>st</sup> 22 nm Core Product

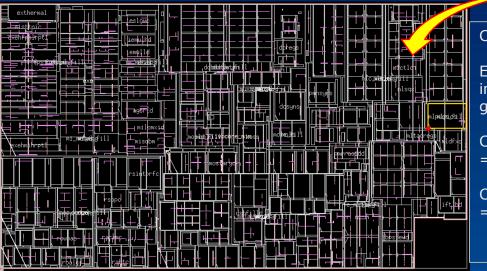

#### Ivy Bridge Microarchitecture

<u>омі</u> 2012 РСН

eap ahead

#### Leveraged from Sandy Bridge:

- Continue the 2-chip platform partition (CPU + PCH)

- Fully integrated on silicon:

- 2-4 IA Cores

- Processor Graphics, Media, Display Engine

- Integrated Memory Controller

- PCIe Controllers

- Modular On-Die Ring Interconnect

- Shared LLC between IA Cores and Graphics

- Same socket, similar packages

- Similar SKUs (TDP, die configurations)

- IVB backwards compatible with SNB

### Ivy Bridge – Key New Things

#### Entire chip moves to 22nm

- Higher performance/Lower power

- Instruction Set Architecture Enhancements

- Float16 / Fast FS/GS support / REP MOVSB / RDRAND

- Security Enhancements

- DRNG / SMEP

- Power Improvements

- Scalability features: ConfigTDP

- Average Power features: DDR power gates / PAIR

- □ IO/Memory

- DDR3L support

- Improved overclocking support

Performance Improvements (Instructions/clock)

# Contents

> Ivy Bridge Overview > Power Scaling & Efficiency > Idle power Management > Configurable TDP > Clocking > Additional Information

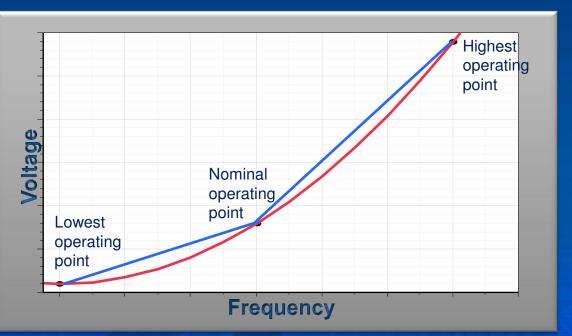

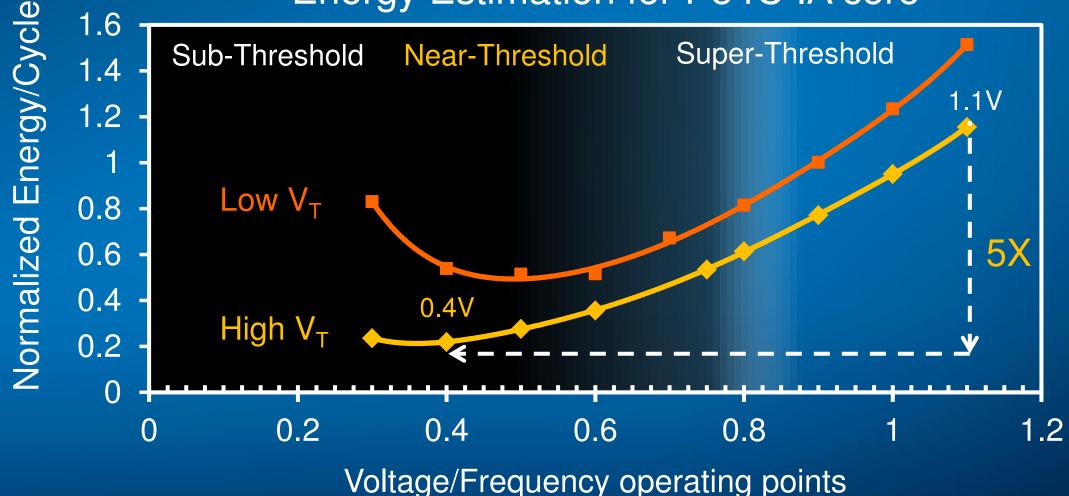

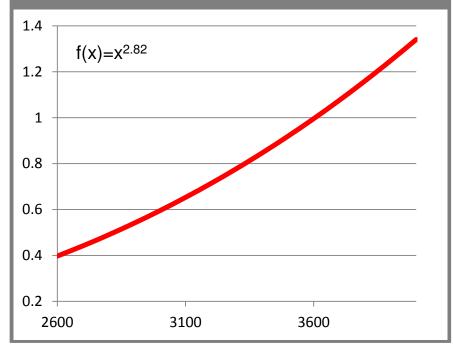

#### Power efficiency via scaling & testing

- Power Scaling in 22nm process extracted in two ways

- Higher performance in IA & Graphics within a power envelope

- Lower operating Voltage in System Agent and Memory controller

- Power loss from discrete test points and interpolation (blue line)

- Ivy Bridge builds a quadratic model of the VF based on enhanced testing (red line)

- Optimal voltage at all operating points

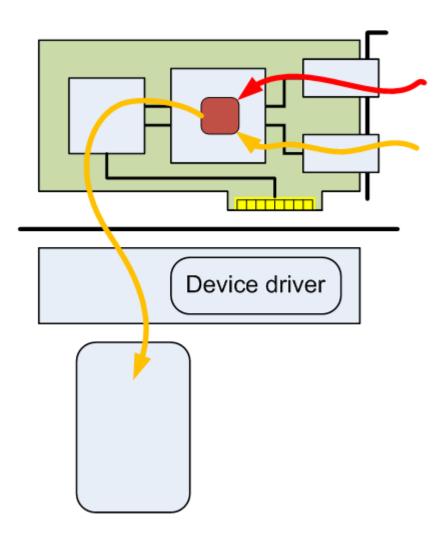

### Power efficiency via interrupt routing

#### PAIR algorithm lowers power or performance impact of re-routable interrupts

- Compares power-state of all cores eligible to service interrupt

- Chooses "best core" based on optimization mode (Power vs. Performance)

- "Best Core" based on the following

- Core C-states

- P-state request (turbo vs. non-turbo)

#### Example: 1 core in C6 & 1 in C0

- Power bias will direct the interrupt to core in C0

- Performance bias will wake the C6 core

#### **Temperature effects**

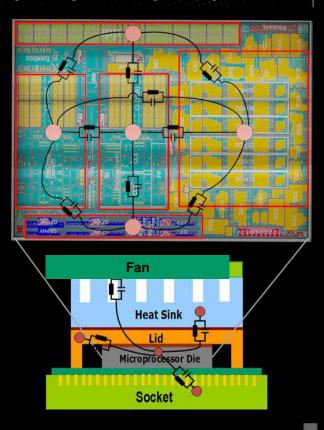

- Thermal sensors are located in the hot spots in the IA core and GPU core

- Inverse temperature dependence (ITD) effects more pronounced in the 22nm node

- No sensors at the cold spots

- IVB estimates the coldest point on the die to based on thermal sensors compensate for the effect

- Manufacturing test voltages at hot and cold temperatures

- PCU interpolates linearly at run time to determine the voltage

- Temperature moves slowly enough for the PCU and voltage regulator to keep up

# Contents

> Ivy Bridge Overview > Power Scaling & Efficiency Idle power Management > Configurable TDP > Clocking > Additional Information

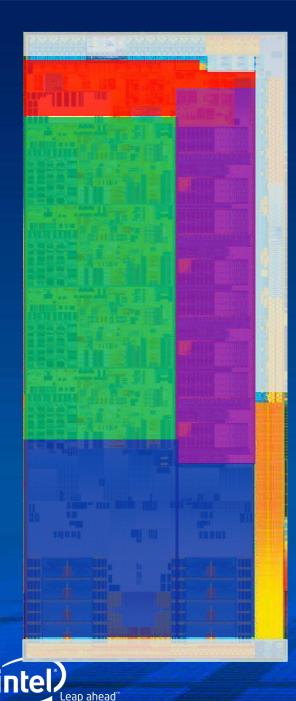

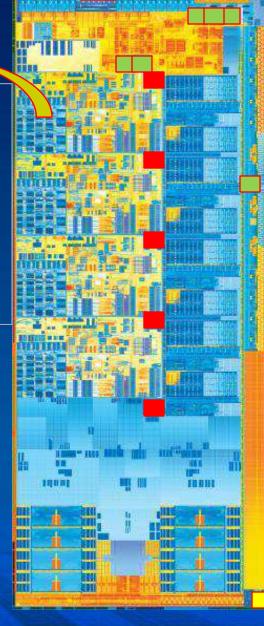

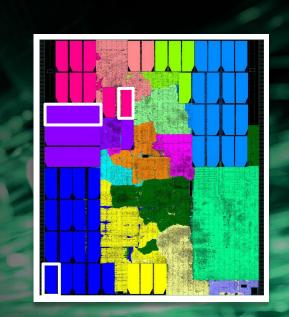

#### **Ivy Bridge Power Planes**

#### Key Power planes

- Core (Gated Green)

- LLC (Ungated Purple)

- SA/Display Red

- GT Blue

- Others (like IO, PLL etc) Gray

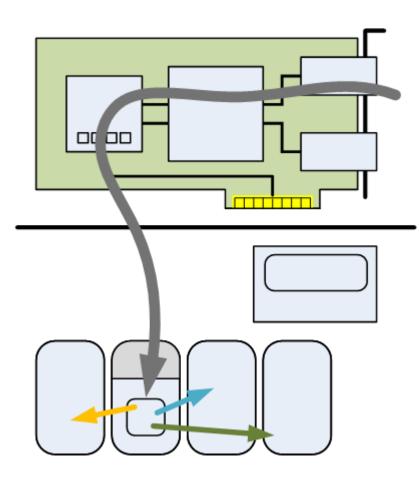

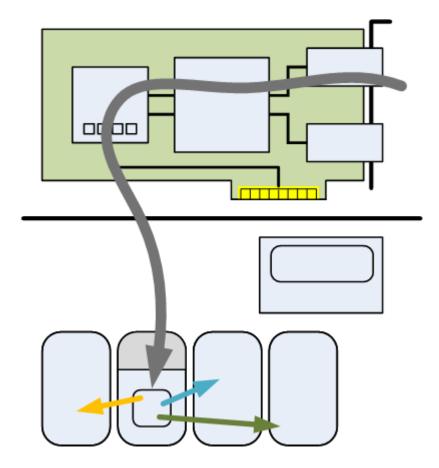

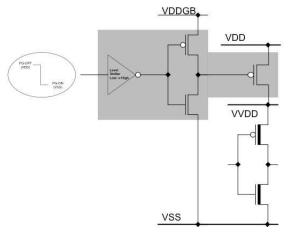

### **IVB Embedded Power Gate**

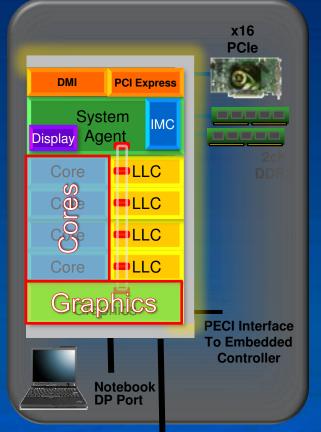

Ivy Bridge has 3 on-die power gating areas

- Cores (Green)

- Independent Gating per Core

- Unified Cache

- PCIE controller(Red)

- Gating static only when no connection

- DDR (Purple)

- Gating of digital logic in the buffer applied during self-refresh mode

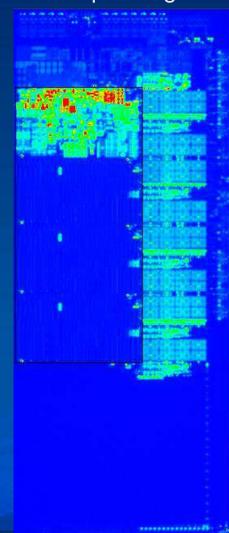

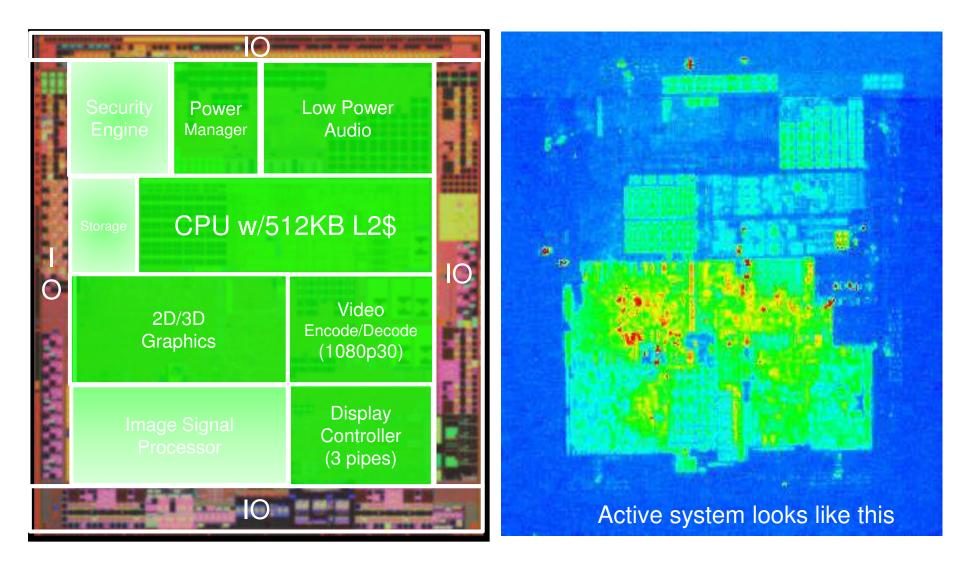

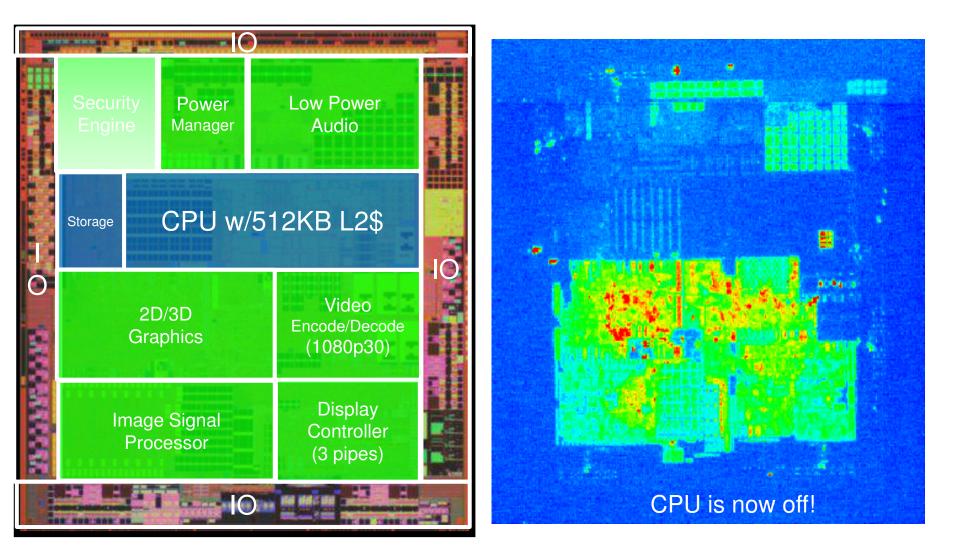

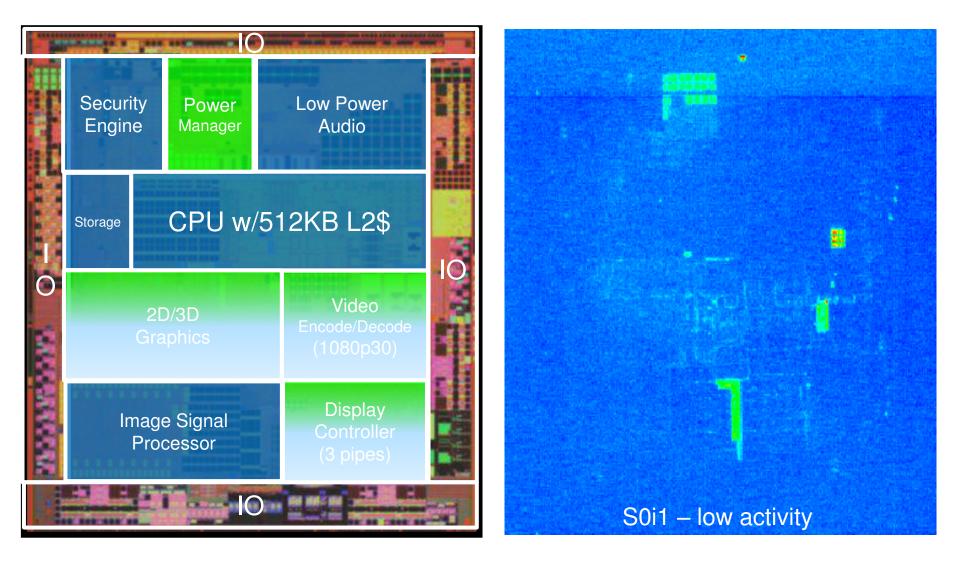

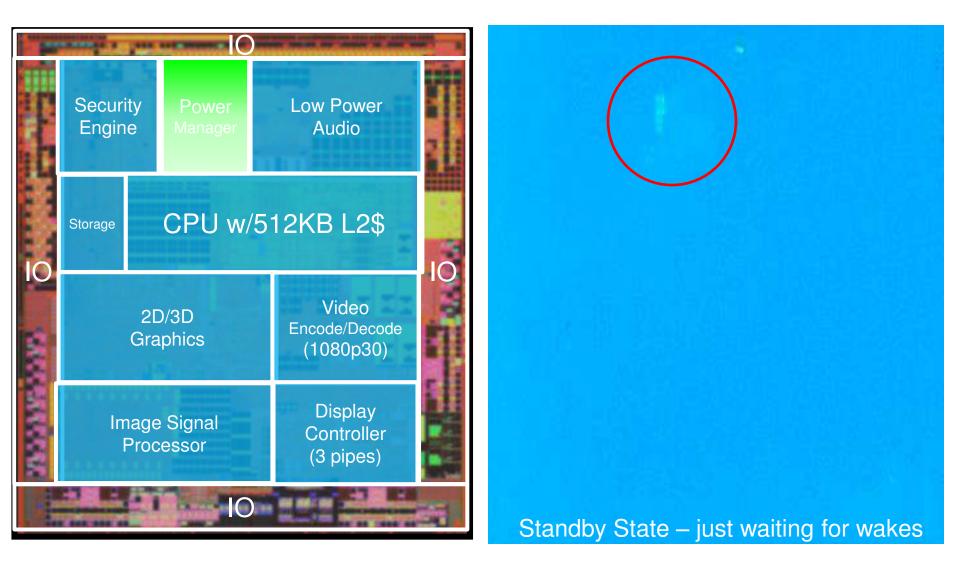

#### **IREM** images

1 core in turbo, other 3 cores power gated

\_eap ahead"

Typical Usage of Cores and Graphics Cores and Graphics gated

#### **DDR I/O Power Gating**

# Ivy Bridge implements on-die Embedded Power Gating (EPG) on DDR I/O Latency & Tradeoffs

Latency considerations

- Enabled on entry into Package C3 and deeper (memory in Self Refresh) to deal with latency of power gate

- Additional latency of <5uS for device access to memory during exit

- Conditional enabling only if devices can tolerate the latency

- No Impact to exit latency for interrupts

- Design tradeoffs

- To get around saving and restoring context, the DDR state is put on an ungated power island

For Idle/MM07-OP, Intel expects DDR IO to be gated ~90% of the time

### Low Voltage optimizations

- Small Signal arrays and register files limit the lowest operating voltage and retention voltage

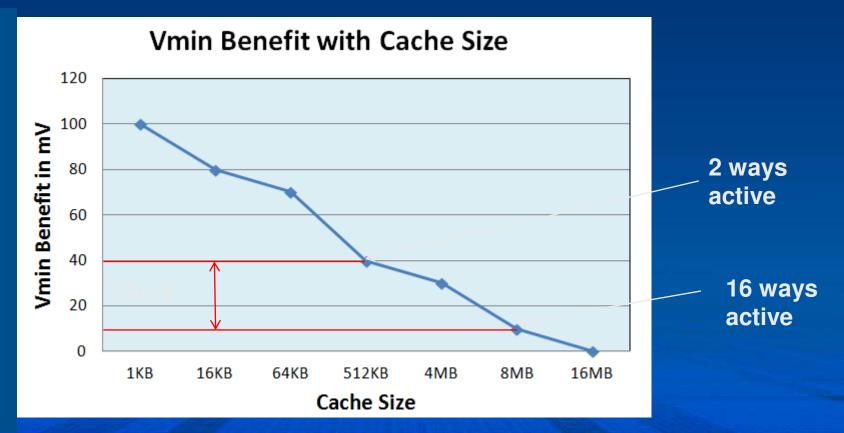

- 1. Dynamic cache sizing to achieve a lower cache Vmin

- Cache Vmin is limited by 'bad cells' or defects distributed across the cache

- A smaller size cache has a lower Vmin due to fewer defects

- 2. PCU Firmware based register file reinitialization on exit from standby states

- Allows reduction of retention voltage below the retention level of the register file

Max(Vmin1,2,3)

#### LLC - Dynamic Cache Shrink Feature

- Reduce LLC cache size dynamically from 8MB to 512KB to gain 30mV Vmin benefit

- LLC Expand/Shrink algorithm is developed for this purpose Entry/exit points were defined based on the work loads &

- perfórmance

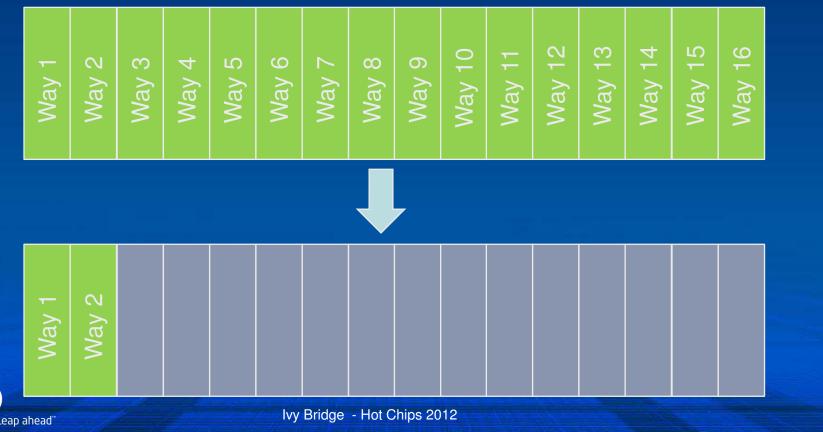

#### LLC - Dynamic Cache Shrink Feature

- LLC organized in 16 ways.

When PCU detects low activity workload

Flushes 14 ways of the cache and puts ways to sleep

Shrinks active ways from 16 to 2 to improve VccMin

When PCU detects high activity

- - Expands active ways back to 16 to improve cache hit rate.

Active

Sleep

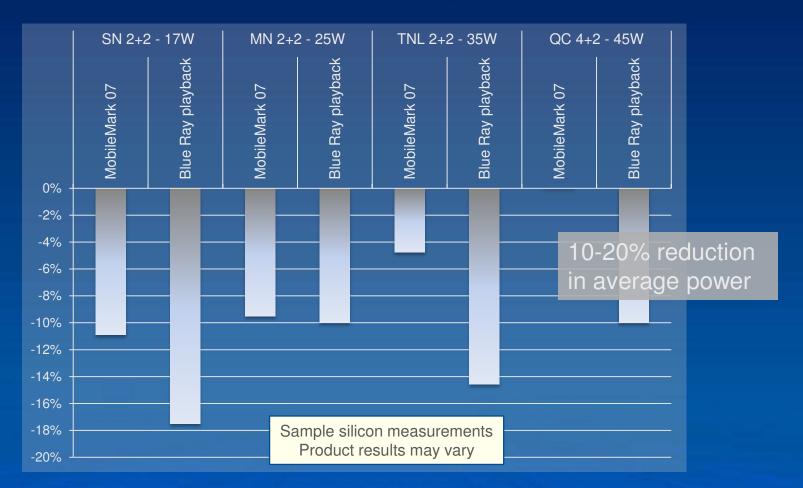

#### Ivy Bridge average power reduction (relative to SNB)

Power reduction via new PM features and process scaling benefits Benefits on other SKUs varies

Ivy Bridge - Hot Chips 2012

eap ahead

# Contents

> Ivy Bridge Overview > Power Scaling & Efficiency > Idle power Management Configurable TDP > Clocking > Additional Information

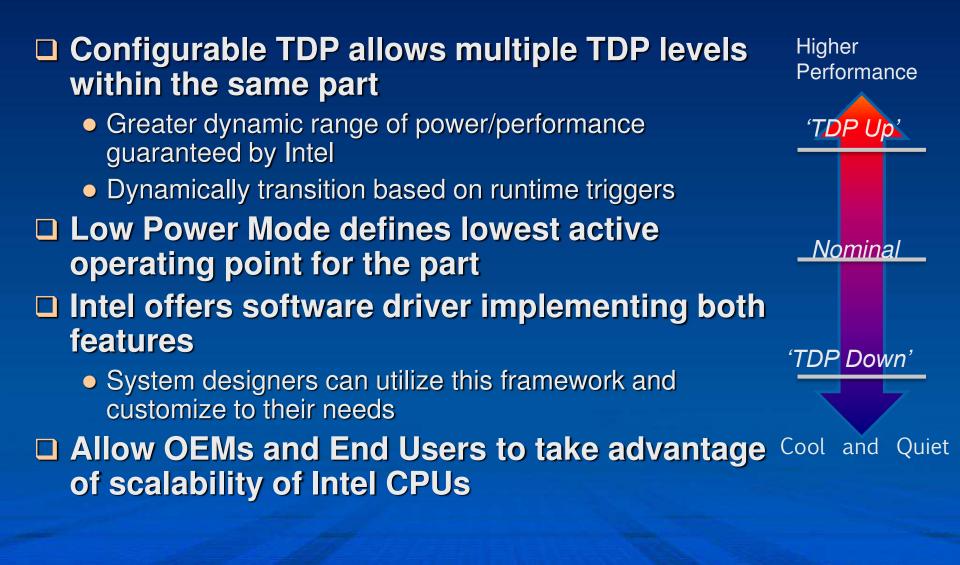

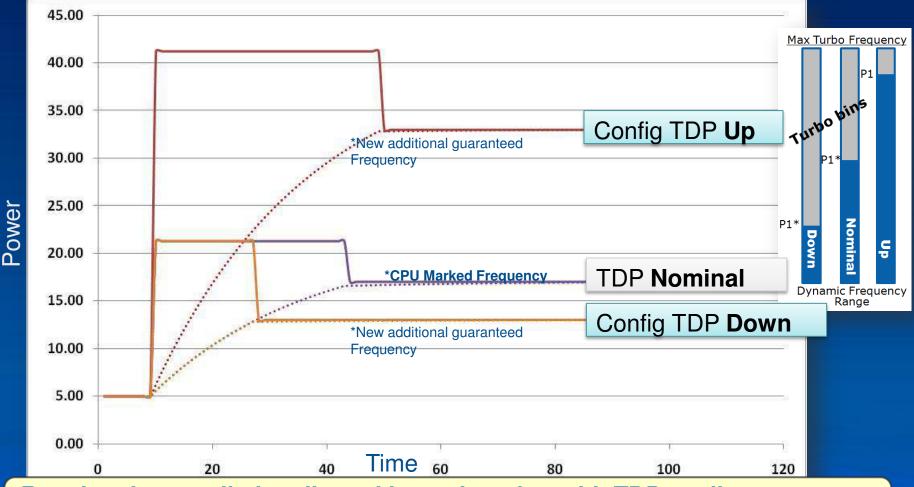

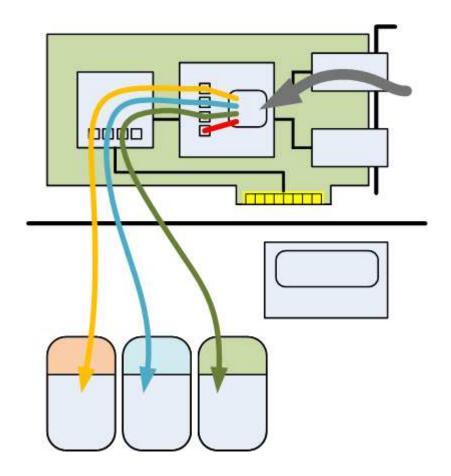

### **Configurable TDP & Low Power Mode**

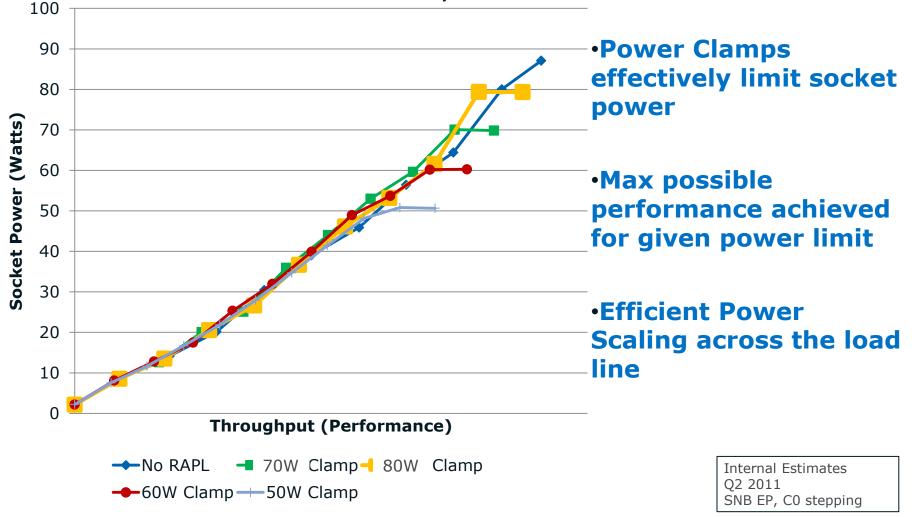

## **cTDP Power Control**

Regulated power limit adjusted in conjunction with TDP to allow guaranteed frequency (performance) at a specific power level

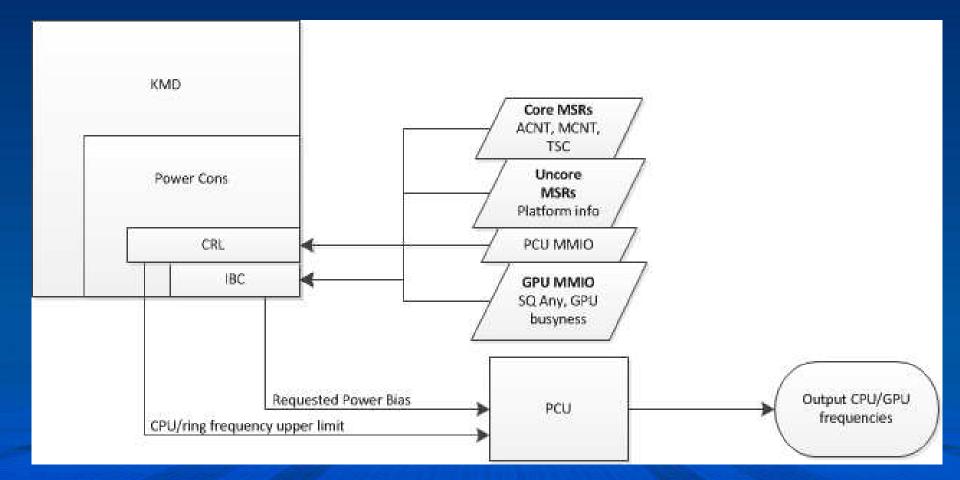

## IA/GPU Power sharing

OEMs can configure the cooling limits to <17W</li>

Static biasing (X% to GPU and 100-X% to IA) results in sub optimal performance

Solution: Distribute power based on workload demand

- Determine target CPU/ring frequency based on workload

- If actual CPU/ring freq < (target frequency guard band)</li>

*Move bias toward CPU Else Move bias toward GPU* With hysteresis

## **Intelligent Bias Control Architecture**

## **Platform Power management**

## Power delivery management

- How do we deal with the platform need to divert current from the CPU to other components dynamically?

- IVB PCU will manage the current draw and will honor dynamic max current updates

- Platform debug and tuning hooks

- IVB provides feedback to platform designers if power delivery, & cooling is limiting performance

# Contents

> Ivy Bridge Overview > Power Scaling & Efficiency > Idle power Management Configurable TDP > Clocking > Additional Information

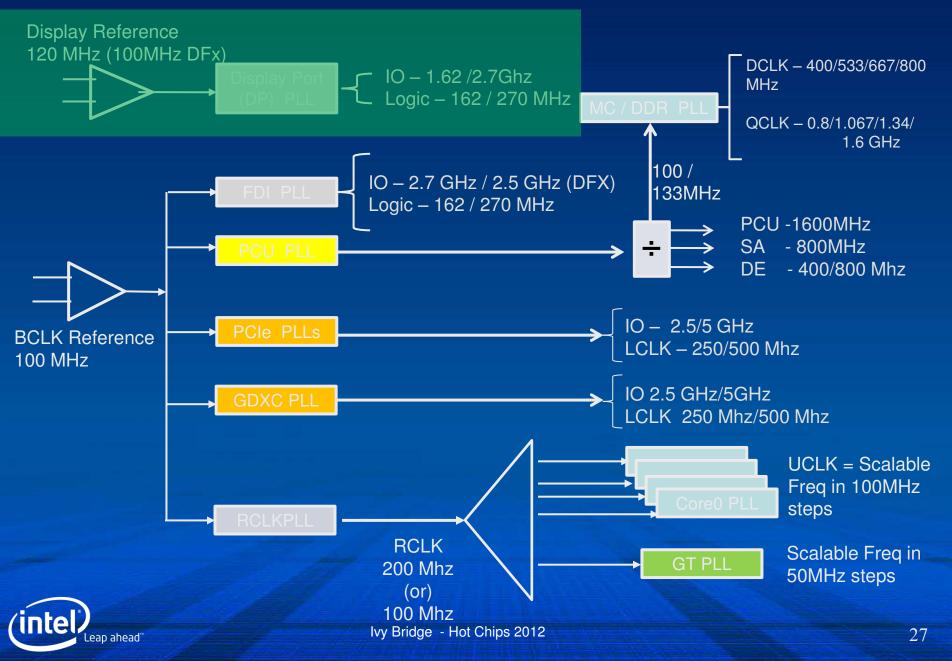

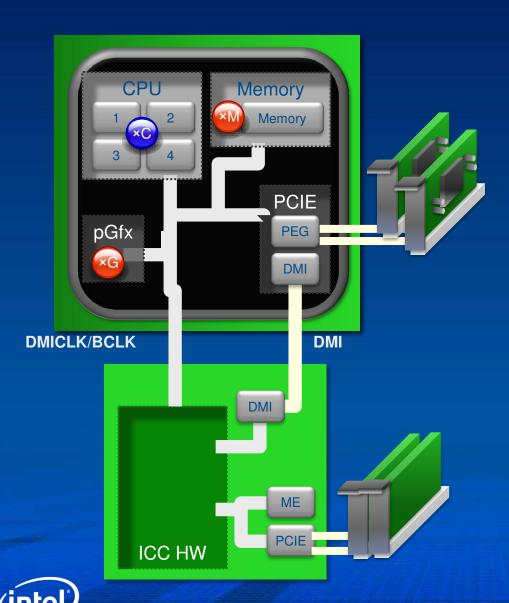

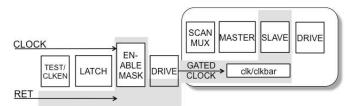

## **IVB Clock Domains**

# **PLL/Clocking**

| Clock | Isla | ands | in | Core |

|-------|------|------|----|------|

|-------|------|------|----|------|

Each Island can be independently clock gated.

Clock Islands in Core =180

Clock Islands in LLC = 48

Wide Range SB PLL

Single Ratio SB PLL

PCIE LC PLL

| 1 |                          |           |        |           |

|---|--------------------------|-----------|--------|-----------|

|   | Slice Clocking Cdyn      | CORE (pF) | L3(pF) | TOTAL(pF) |

|   | Total (including RT)     | 179       | 77     | 256       |

|   |                          |           |        |           |

|   | Global Drivers + Islands | 109       | 46     | 155       |

|   | Clock Source + Spines    | 70        | 31     | 101       |

|   |                          |           |        |           |

|   | Silicon Measurement      | 181       | 81     | 262       |

| 1 |                          |           |        |           |

### **Overclocking Enhancements**

eap ahead

Core Frequency

- Unlocked turbo limits

- Unlocked core ratios up to 63 in 100MHz increments<sup>†</sup>

- Programmable voltage offset

- Graphics Frequency

- Unlocked graphics turbo limits

- Unlocked graphics ratios up to 60 in 50MHz increments

- Programmable voltage offset

- Memory Ratio

- 0

- Unlocked memory controller

- Granularity options for 200 and 266MHz

- Logical support up to 2666MHz

- DMICLK (aka BCLK)

- Unlocked PCH clock controller (1MHz increments)

- PEG and DMI

- Fixed ratios

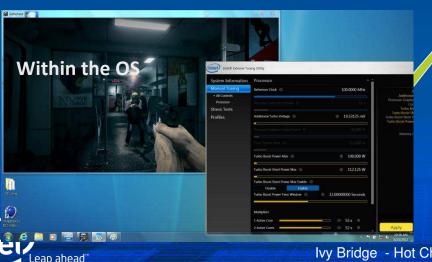

## **Real-Time Overclocking**

intel

Profiles

- PCU samples OC parameters continuously and updates power limits

- OC without reboot:

- Maximum Core Ratio

- Processor Graphics Ratio

- BCLK (small increments)

- Power Limits: PL1, PL2, Tau

- Additional Turbo Voltage for CPU and pGfx

#### Intel® Extreme Tuning Utility System Information Processor Manual Tuning Reference Clock ① 100.0000 MHz All Controls Processor Stress Tests Additional Turbo Voltage 🕧 19.53125 mV Turbo Boost Power Max 0 100.000 W Turbo Boost Short Power Max 0 8 112.125 W Turbo Boost Short Power Max Enable ① Disable Fnable Turbo Boost Power Time Window 🕕 32.00000000 Seconds Multipliers 53 x 🛞 1 Active Core 2 Active Cores 52 x ⊗ 3 Active Cores 51 x ⊗ 50 x ⊗ **4** Active Cores

Changes effective immediately

## Acknowledgements

Authors would like to thank the entire lvy Bridge team for their dedicated work.

# Contents

> Ivy Bridge Overview > Power Scaling & Efficiency > Idle power Management > Configurable TDP > Clocking >Additional Information

## Ivy Bridge ISA & Security enhancements

## **Float16 Data Conversion Instructions**

New instructions for supporting conversion between a 16-bit floating point memory format and 32-bit single precision

- VCVTPH2PS, VCVTPS2PH

- Both 128 (SSE) and 256 bit (AVX) wide vector flavors supported

- Only supported in the VEX prefix context

- Facilitates use of single-precision floating point computations from a more compressed memory format

- 1-bit sign, 5-bit exponent, 10-bit significand (+ implicit integer bit)

- Enables higher dynamic range compared to fixed point within the same storage footprint

- Image processing, video decode, audio processing

- 50% reduction in storage v. single-precision FP (w/ loss of fidelity)

- Enumerated via new CPUID feature flag

- CPUID.1.ECX[29]

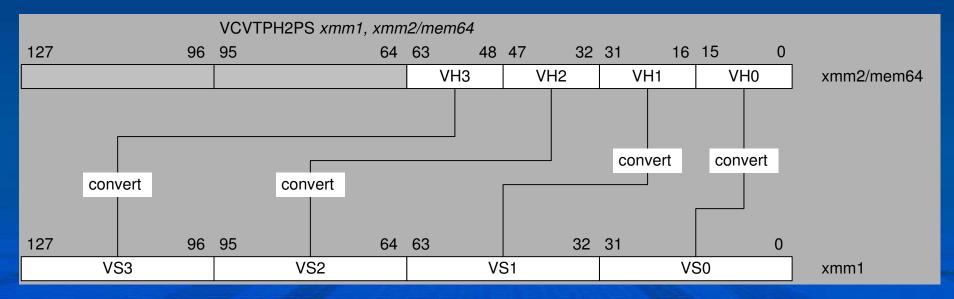

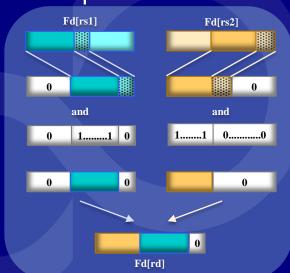

## VCVTPH2PS – Convert 16-bit float to SP

## VCVTPH2PS *ymm1*, *xmm2/mem128* VCVTPH2PS *xmm1*, *xmm2/mem64*

### - 256 bit vector - 128 bit vector

Converts four packed 16-bit floating-point values in the low 64 bits of XMM2 or 64-bit memory location to four single-precision floating-point values and writes the results in the destination (XMM1 register).

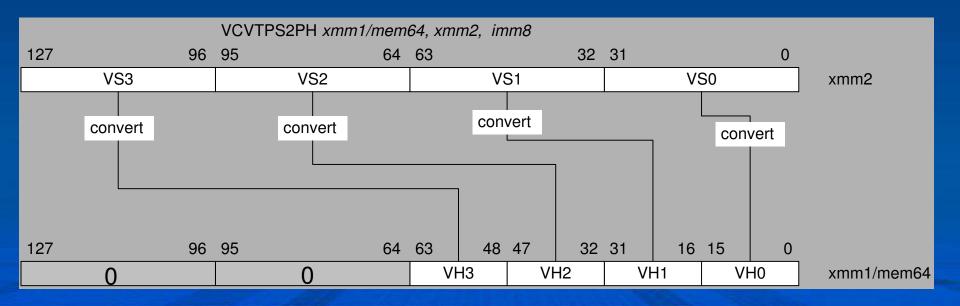

## VCVTPS2PH – Convert SP to 16-bit float

VCVTPS2PH xmm1/mem64, xmm2, imm8 VCVTPS2PH xmm1/mem128, ymm2, imm8 - 256 bit vector

- 128 bit vector

Converts four packed single-precision floating-point values in XMM2 to four 16bit floating-point values and writes the results in the destination (XMM1 register or memory location).

## Write/Read FS/GS Base Instructions

- New ring-3 instructions for read/write of the FS & GS segment base registers

- To be used by user level code for thread local storage

- Enumerated via new CPUID feature flag

- CPUID.7.0.EBX[0] indicates availability (leaf 7, subleaf 0)

- Requires enabling by OS to permit FS/GS segment base access

- CR4.RDWRGSFS (bit 16) = 0 (default)

- Motivation:

- Improve scalability and programming ease for user threads

## **REP MOVSB/STOSB improvements**

- Historically optimizing block copy/fill operations tends to be microarchitecture specific

- Lack of a "one size fits all" solution implies CPU model specific algorithms for best performance

# IVB address this through more optimized REP MOVSB and REP STOSB instructions

- Expect this to replace the need for manual tuning solutions

- Limitation: If block size is known at compile time and size <=64 bytes, then scalar loads & stores are still considered faster

### Enhancement availability indicated by CPUID.7.0.EBX[9] (ENFSTRG)

This bit can be used by run time SW (Libraries, JIT) for tuning to a specific implementation

Ivy Bridge - Hot Chips 2012

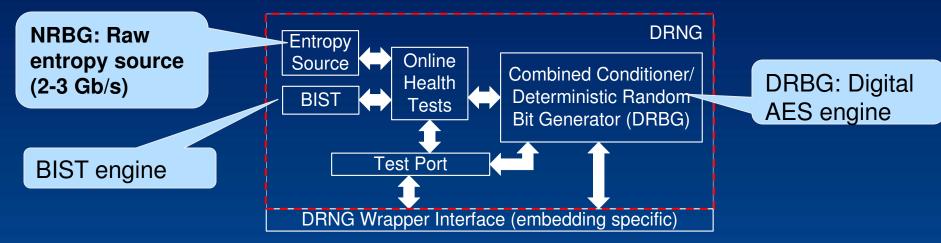

# **Digital Random Number Generator (DRNG)**

#### Background:

- Entropy is valuable in a variety of uses Example: "keying material" in cryptography

- Historically, computing platforms did not have a good source of a high quality/high performance "entropy source"

- Typical sources used today are slow (bit rate in Kb/s) (key strokes, mouse clicks etc)

- IVB introduces high quality/high performance DRNG

- The DRNG is designed to be Standards compliant

- ANSI X9.82,NIST SP 800-90 and NIST FIPS 140-2/3 Level 2 certifiable entropy source

- New instruction: RDRAND Available at all privilege levels/operating modes

- Instruction will return a random number (16, 32 or 64-bit) to the destination register

- New CPUID feature flag for RDRAND enumeration

CPUID.1.ECX[30]

eap ahead

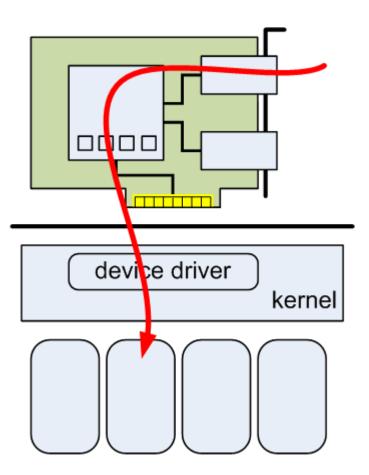

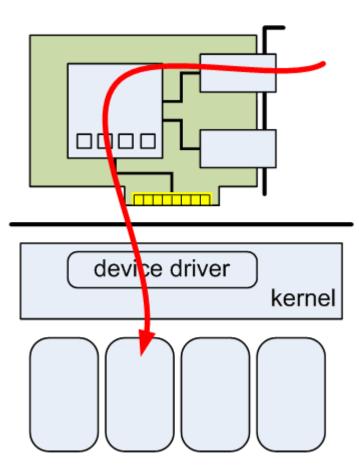

## **Supervisory Mode Execute Protection (SMEP)**

### Background:

0xF..FFF

System call

0x0..000

eap ahead

Kernel

Memory

NULL

pointer vulnerability

App

memory

Attack code Jump-or-call

- Privilege Escalation Attack causes CPL 0 access to user mode pages

- Example:

- Step 1: Compromise user mode app or trick user into installing attack app

- Step 2: Exploit OS vulnerability to force control transfer to user mode attack code while CPU remains in supervisory mode => privilege escalation

IVB introduces SMEP to help prevent such attacks

- Prevents execution of user mode pages while in supervisor mode

- If CR4.SMEP set to 1 and in supervisor mode (CPL<3), instructions may not be executed from a linear address for which the user mode flag is 1

• Available in both 32- and 64-bit operating modes

• SMEP is enumerated via CPUID.7.0.EBX[7] Ivy Bridge - Hot Chips 2012

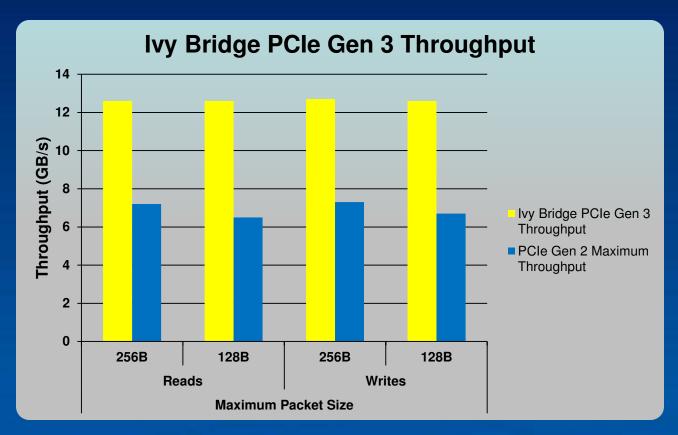

# **PCI Express Gen 3**

## Ivy Bridge PCI Express Gen 3

## □ Third generation of the PCI Express I/O interface

- Delivers nearly twice the I/O bandwidth v. Gen 2

- Improves performance for applications sensitive to I/O bandwidth

- Enables smaller form factors via narrower, faster physical links

### Bandwidth realized through:

eap ahead

- Faster signaling speed: 8 GT/s

- More efficient lane encoding: 128/130

### Utilizes Gen 2 I/O channel characteristics

- Enables compatibility with previous Gen components

- Enables drop-in upgrade for Sandy Bridge-based platforms

Supports PCIe bandwidth management & ASPM states

Dynamic Link Width Configuration, L0s (Rx & Tx), L1

## Ivy Bridge PCIe Performance\*

Ivy Bridge delivers nearly 2x Gen 2 bandwidth

At similar latencies

~300ns typical for upstream read request

Ivy Bridge - Hot Chips 2012

Results have been estimated based on internal Intel analysis and are provided for informational purposes only. Any difference in system hardware or software design or configuration may affect actual performance.

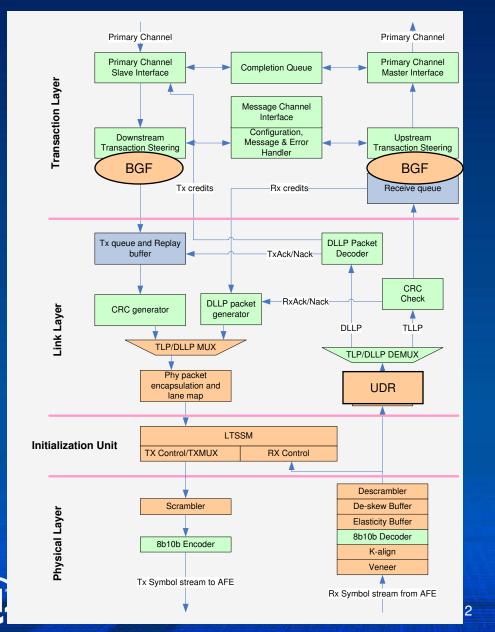

## Ivy Bridge PCIe Logic Changes

- Sandy Bridge PCIe uArch unchanged

- No change to primary channel hub/TL interface

No change to controller/PHY lanes interface

Gen 3 changes layered on top of Gen 2 functionality (additional states, arcs)

Parallel flows implemented where feasible

43

# **IPC Improvements**

## Most Significant IVB IPC Improvements

## Pipeline MOV elimination

Eliminates Move related micro-operations from the processor execution pipeline

## Pipelined divider

• Improves throughput of divide related computations

## Next page prefetcher

• Enables prefetching to span across a 4K page boundary

## Shift/Rotate performance

- Addresses glass jaw concern with crypto and hashing algorithms

- Addresses clumsiness of partial flag handling

- 6 additional split load registers

- Improves performance for loads splitting cache lines

- Especially critical for AVX or SSE

## **Uncore IPC Features**

#### AFP – Adaptive Fill Policy

Cache heuristics to identify and segregate streaming applications

### QLRU – Quad-Age LRU algorithm

- Allows fine-grain "age assignment" on cache allocation

- E.g.: prefetched requests are allocated at "middle age"

#### DPT – Dynamic Prefetch Throttling

- Real-time memory bandwidth monitor

- Directs core prefetchers to reduce prefetch aggressiveness during high memory load scenarios

Channel Hashing -- DRAM channel selection mechanism

- Allows channel selection to be made based on multiple address bits

- Historically, it had been "A[6]"

- Allows more even distribution of memory accesses across channels

# **Legal Notices and Disclaimers**

- INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL® PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

- Intel may make changes to specifications and product descriptions at any time, without notice.

- All products, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

- Intel, processors, chipsets, and desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- Any code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

- Intel product plans in this presentation do not constitute Intel plan of record product roadmaps. Please contact your Intel representative to obtain Intel's current plan of record product roadmaps.

- Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more information go to <u>http://www.intel.com/performance</u>

- Intel, Intel Inside, the Intel logo, Centrino, Intel Core, Intel Atom, Pentium and UltraBook are trademarks of Intel Corporation in the United States and other countries.

- <u>Material in this presentation is intended as product positioning and not approved end user messaging.</u>

- This document contains information on products in the design phase of development.

- \*Other names and brands may be claimed as the property of others.

- Copyright © 2012 Intel Corporation, All Rights Reserved

# Legal Notices and Disclaimers, cont.

- WiMAX connectivity requires a WiMAX enabled device and subscription to a WiMAX broadband service. WiMAX connectivity may require you to purchase additional software or hardware at extra cost. Availability of WiMAX is limited, check with your service provider for details on availability and network limitations. Broadband performance and results may vary due to environment factors and other variables. See <a href="https://www.intel.com/go/wimax">www.intel.com/go/wimax</a> for more information.

- Intel® My WiFi Technology is an optional feature and requires additional software and a Centrino® wireless adapter. Wi-Fi devices must be certified by the Wi-Fi Alliance for 802.11b/g/a in order to connect. See mywifi.intel.com for more details.

- Hyper-Threading Technology requires a computer system with a processor supporting HT Technology and an HT Technology-enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. For more information including details on which processors support HT Technology, see <u>here</u>

- Intel® Turbo Boost Technology requires a PC with a processor with Intel Turbo Boost Technology capability. Intel Turbo Boost Technology performance varies depending on hardware, software and overall system configuration. Check with your PC manufacturer on whether your system delivers Intel Turbo Boost Technology. For more information, see <u>http://www.intel.com/technology/turboboost</u>

- Requires an Intel® Wireless Display enabled PC, TV Adapter, and compatible television. Available on select Intel® Core processors. Does not support Blu-Ray or other protected content playback. Consult your PC manufacturer. For more information, see <u>www.intel.com/go/wirelessdisplay</u>

- (Built-in Visuals) Available on the 2nd gen Intel® Core<sup>™</sup> processor family. Includes Intel® HD Graphics, Intel® Quick Sync Video, Intel® Clear Video HD Technology, Intel® InTru<sup>™</sup> 3D Technology, and Intel® Advanced Vector Extensions. Also optionally includes Intel® Wireless Display depending on whether enabled on a given system or not. Whether you will receive the benefits of built-in visuals depends upon the particular design of the PC you choose. Consult your PC manufacturer whether built-in visuals are enabled on your system. Learn more about built-in visuals at http://www.intel.com/technology/visualtechnology/index.htm.

- Intel® Insider™ is a hardware-based content protection mechanism. Requires a 2nd generation Intel® Core™ processor-based PC with built-in visuals enabled, an Internet connection, and content purchase or rental from qualified providers. Consult your PC manufacturer. For more information, visit <u>www.intel.com/go/intelinsider</u>.

- Viewing Stereo 3D content requires 3D glasses and a 3D capable display. Physical risk factors may be present when viewing 3D material

# Legal Notices and Disclaimers, cont.

- Security features enabled by Intel® AMT require an enabled chipset, network hardware and software and a corporate network connection. Intel AMT may not be available or certain capabilities may be limited over a host OS-based VPN or when connecting wirelessly, on battery power, sleeping, hibernating or powered off. Setup requires configuration and may require scripting with the management console or further integration into existing security frameworks, and modifications or implementation of new business processes. For more information, see <a href="http://www.intel.com/technology/manage/iamt">http://www.intel.com/technology/manage/iamt</a>.

- No system can provide absolute security under all conditions. Requires an enabled chipset, BIOS, firmware and software and a subscription with a capable Service Provider. Consult your system manufacturer and Service Provider for availability and functionality. Intel assumes no liability for lost or stolen data and/or systems or any other damages resulting thereof. For more information, visit <u>http://www.intel.com/go/anti-theft</u>

- Requires an Execute Disable Bit enabled system. Check with your PC manufacturer to determine whether your system delivers this functionality. For more information, visit <u>http://www.intel.com/technology/xdbit/index.htm</u>

- Intel® vPro<sup>™</sup> Technology is sophisticated and requires setup and activation. Availability of features and results will depend upon the setup and configuration of your hardware, software and IT environment. To learn more visit: <u>http://www.intel.com/technology/vpro</u>

- The original equipment manufacturer must provide TPM functionality, which requires a TPM-supported BIOS. TPM functionality must be initialized and may not be available in all countries.

- Intel® AES-NI requires a computer system with an AES-NI enabled processor, as well as non-Intel software to execute the instructions in the correct sequence. AES-NI is available on select Intel® processors. For availability, consult your reseller or system manufacturer. For more information, see <a href="http://software.intel.com/enus/articles/intel-advanced-encryption-standard-instructions-aes-ni/">http://software.intel.com/enus/articles/intel-advanced-encryption-standard-instructions-aes-ni/</a>

- No system can provide absolute security under all conditions. Requires an Intel IPT enabled system, including a 2nd generation Intel Core processor, enabled chipset, firmware, and software. Available only on participating websites. Consult your system manufacturer. Intel assumes no liability for lost or stolen data and/or systems or any resulting damages. For more information, visit <u>http://www.ipt.intel.com</u>

#### "JAGUAR" AMD's Next Generation Low Power x86 Core

Jeff Rupley, AMD Fellow Chief Architect / Jaguar Core August 28, 2012

TWO X86 CORES TUNED FOR TARGET MARKETS

> "Bulldozer Family" Performance & Scalability

"Cat Family" Flexible, Low Power & Small

AMD

#### "JAGUAR" DESIGN GOALS

- Improve on "Bobcat": performance in a given power envelope

- More IPC

- Better Frequency at given Voltage

- Improve power efficiency thru clock gating and unit redesign

- Update the ISA/Feature Set

- Increase Process Portability

#### ISA/FEATURE SET

ISA: "Bobcat" baseline of AMD64 x86 ISA w/ SSE1-SSSE3, SSE4A

"Jaguar" added:

- SSE4.1, SSE4.2

- AES, CLMUL

- MOVBE

- AVX, XSAVE/XSAVEOPT

- F16C, BMI1

- 40 bit physical address capable

- Improved virtualization

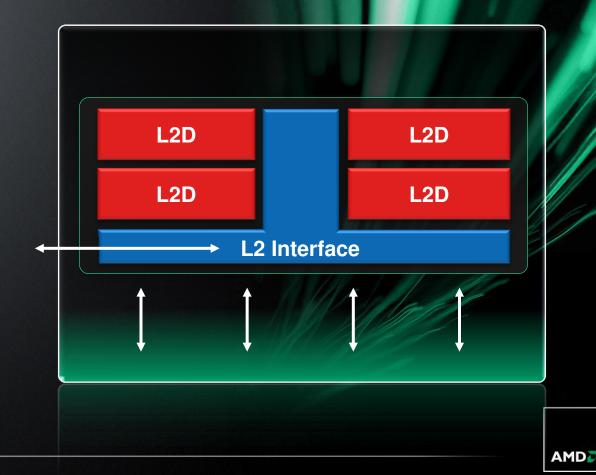

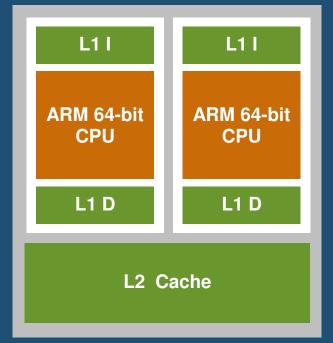

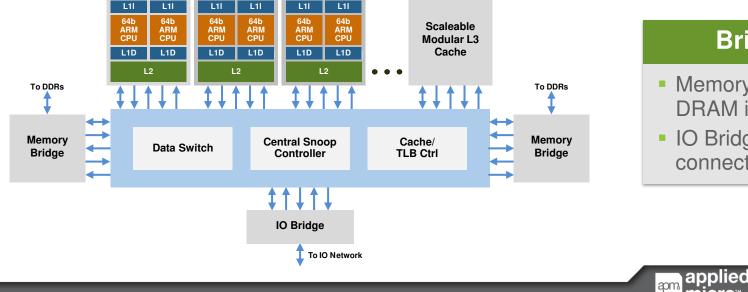

"JAGUAR" COMPUTE UNIT (CU)

4 Independent "Jaguar" coresShared Cache Unit (SCU)

- 4 L2 Data Banks (total 2MB)

- L2 Interface Tile

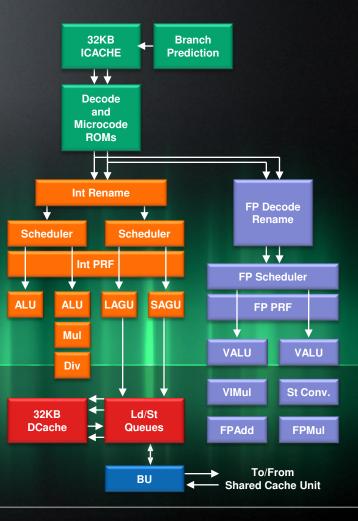

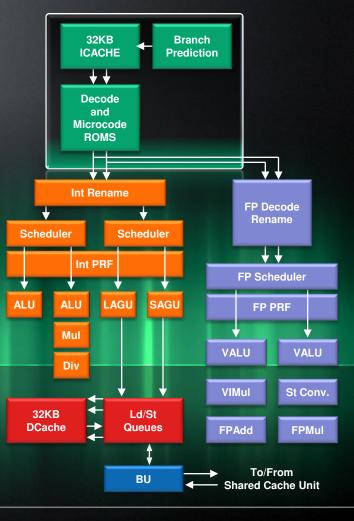

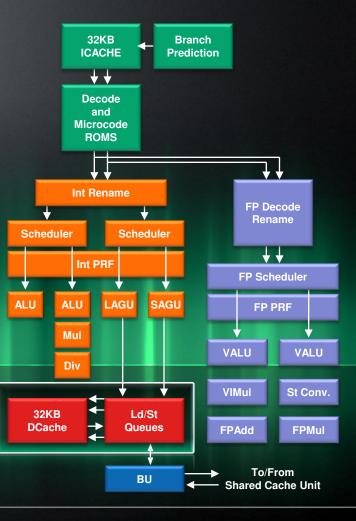

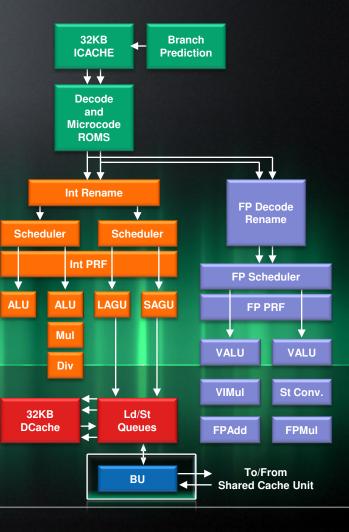

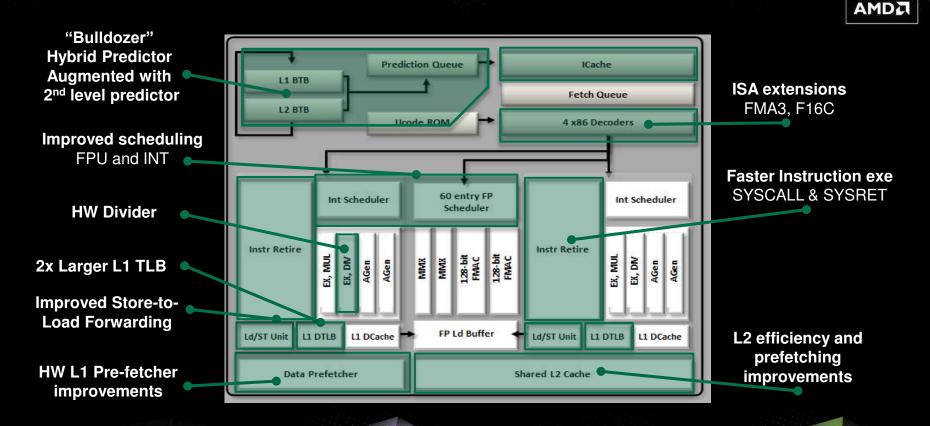

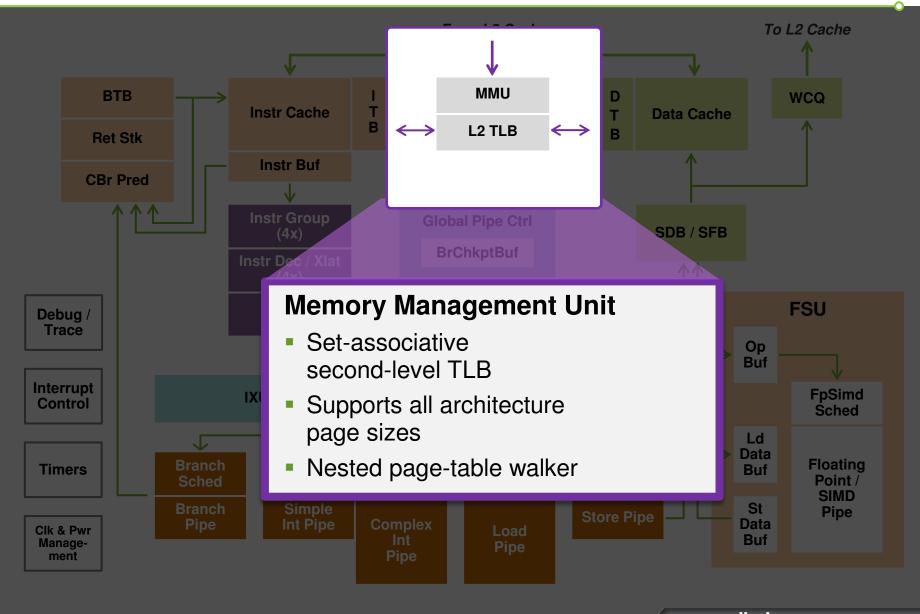

#### "JAGUAR" CORE Micro-Architecture

#### "JAGUAR" CORE Frontend

Like "Bobcat":

- IC: 32KB, 2way

- Itlb: 512 4KB pages

- Layered branch predictor w/ state of the art conditional predictor

- 32B fetch

- 2-instruction decode

#### "Jaguar" Enhancements:

- 4x32B IC loop buffer for power

- Improved IC prefetcher for IPC

- Grew IB for improved fetch/decode decoupling

- Added decode stage for frequency

AMD

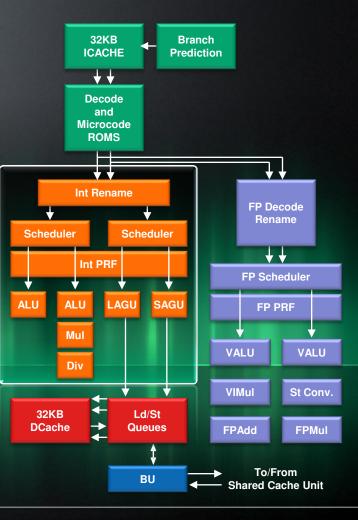

#### "JAGUAR" CORE Integer Execution

Like "Bobcat": Schedulers can issue

- 2 ALU

- 1 LD AGU

- 1 ST AGU

"Jaguar" Enhancements:

- New hardware divider (leveraged from Llano)

- New/improved cops: CRC32/SSE4.2, BMI1, POPCNT, LZCNT

- More OOO resources Larger schedulers, ROB

AMD

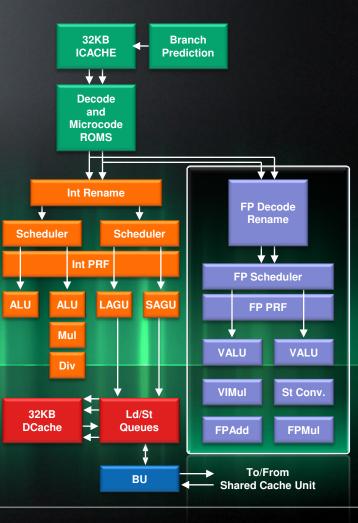

#### "JAGUAR" CORE Floating Point Unit

Like "Bobcat":

- 2 wide FP decode

- OOO scheduler

- 2 execution pipes

"Jaguar" Enhancements:

- 128b native hardware

- 4 SP muls + 4 SP adds

- 1 DP mul + 2 DP adds

- ISA: many new COPs

- 256b AVX supported by double pumping 128b hardware

AMD

New Zero Optimizations

Second FPRF stage for frequency

#### "JAGUAR" CORE Load/Store, Data Cache

Like "Bobcat":

- DC: 32KB, 8way

- L2DTLB: 512 4KB pages

- 8-stream DC prefetcher

• 000 LS

"Jaguar" Enhancements:

- Ld/St Queues redesign:

- Improved OOO picker

- Improved STLF

- Less store data shuffling

AMD

- More OOO resources

- Enhanced Tablewalks

- 128b data path to FPU

#### "JAGUAR" CORE Bus Unit

Like "Bobcat":

BU interfaces between Core (I\$,D\$) and L2\$/NB

#### "Jaguar" Supports:

- 8 DC miss/prefetch

- 3 IC miss/prefetch

- Improved Write Combining with 4 WCB data buffers

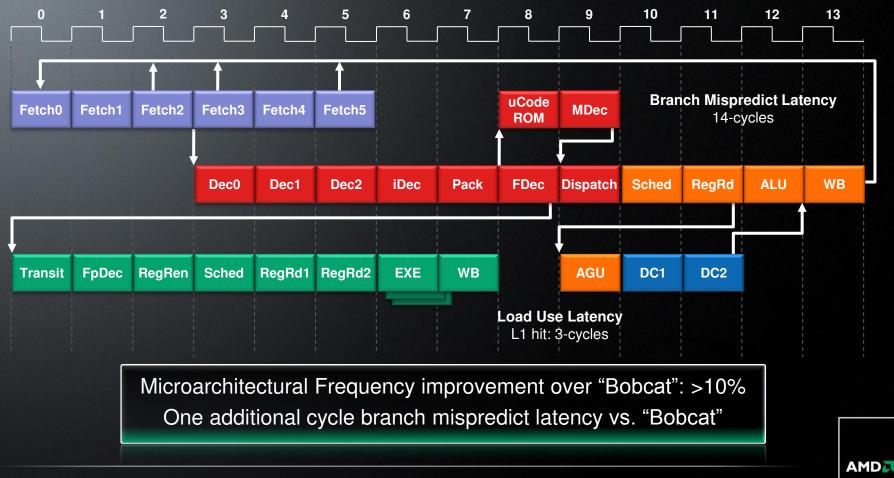

#### "JAGUAR" CORE PIPELINE

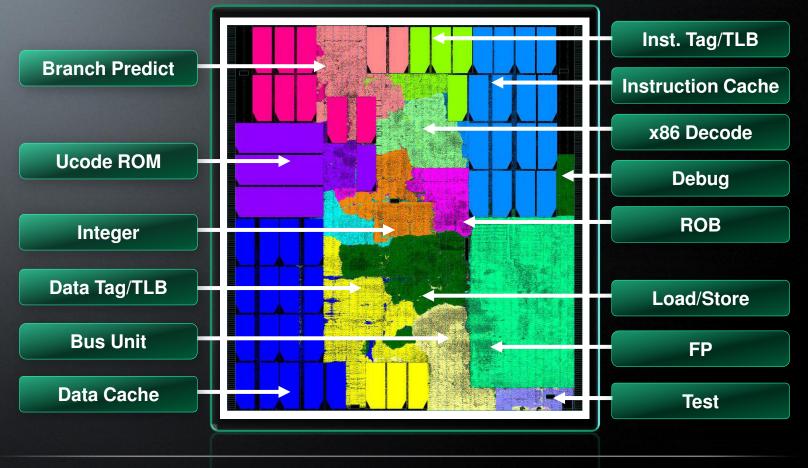

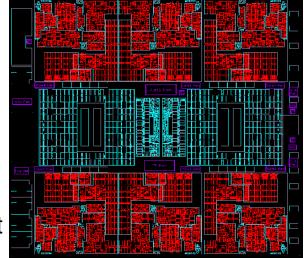

#### "JAGUAR" CORE FLOOR PLAN

#### CORE FLOOR PLAN COMPARISON

"Bobcat" core in 40nm = 4.9 mm<sup>2</sup> 7 core macros, 2 L2 macros, 3 clock macros

"Jaguar" core in 28nm = 3.1 mm<sup>2</sup> 3 core macros, 1 L2 macro, 1 clock macro

14 | "Jaguar " | HotChips 2012

#### "JAGUAR" SHARED CACHE UNIT

Shared Cache is major design addition in "Jaguar"

- Supports 4 cores

- Total shared 2MB, 16-way

- Supported by 4 L2D banks of 512KB each

L2 cache is inclusive – allows using L2 tags as probe filter

Any line in a Core L1 instruction or data cache must be in the L2

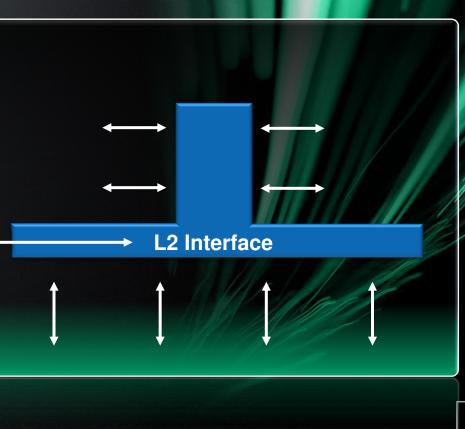

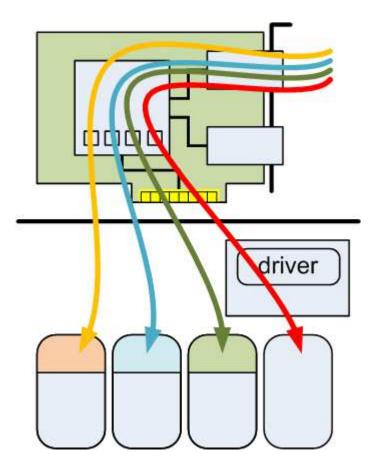

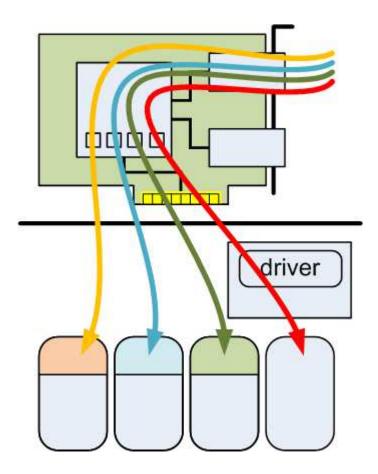

#### "JAGUAR" L2 INTERFACE

- All connections routed thru L2 interface

- L2 tags reside in interface block

- Divided into 4 banks

- L2D bank lookup only after L2 tag hit

- L2 Interface block runs at core clock

- L2D's run at half clock for power, only clocked when required

- New L2 stream prefetcher per core

- Allows improved bandwidths & IPC

- Up to a total of 24 paired read + write transactions in flight

- 16 additional L2 snoop queue entries

- Allows for handling coherent probes at high bandwidth

#### "JAGUAR" C6

- Any Core can independently go into CC6 power gating

- Optimized microcode routines and hardware allow for fast CC6 entry/exit

- Shared L2 leaves more cache for the remaining active cores (IPC)

Last core in the compute unit to be power gated flushes shared L2 in preparation for full C6. Hardware engines added to improve L2 flush times.

# **Relative C6 Latencies Under Normalized Conditions** "Jaguar" CC6 "Bobcat" C6 "Jaguar" C6

AMD

#### "JAGUAR" POWER

Many blocks redesigned for improved power efficiency

– IC Loop Buffer, Store Queue, L2 clocks, etc.

Clock power usage scrubbed, including improved dynamic clock gating:

|                | "Bobcat"<br>IPC | "Jaguar"<br>IPC | "Bobcat" Core<br>Gater Efficiency | "Jaguar" Core<br>Gater Efficiency |

|----------------|-----------------|-----------------|-----------------------------------|-----------------------------------|

| Halt           | 0.00            | 0.00            | 91.8                              | 98.8                              |

| Apps           | 0.95            | 1.10            | 89.7                              | 92.3                              |

| "Bobcat" Virus | 1.74            | 1.78            | 84.6                              | 87.1                              |

| "Jaguar" Virus | 0.81            | 1.86            | 85.7                              | 85.0                              |

Increased frequency capability allows choices:

- Higher frequency -> higher performance

- Same frequency at lower voltage -> lower power

#### SUMMARY

- ISA enhancements

- Increased process portability

- Estimated typical IPC improvement: >15%\*

- Frequency improvement: >10%\*

- Dynamic power efficiency improvements

\*Based on internal AMD modeling using benchmark simulations

#### **DISCLAIMER & ATTRIBUTION**

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions and typographical errors.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. There is no obligation to update or otherwise correct or revise this information. However, we reserve the right to revise this information and to make changes from time to time to the content hereof without obligation to notify any person of such revisions or changes.

NO REPRESENTATIONS OR WARRANTIES ARE MADE WITH RESPECT TO THE CONTENTS HEREOF AND NO RESPONSIBILITY IS ASSUMED FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

ALL IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE ARE EXPRESSLY DISCLAIMED. IN NO EVENT WILL ANY LIABILITY TO ANY PERSON BE INCURRED FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **Trademark Attribution**

©2012 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, Phenom, Radeon, and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Microsoft and DirectX are registered trademarks, of Microsoft Corporation in the United States and/or other jurisdictions. Other names used in this presentation are for identification purposes only and may be trademarks of their respective owners.

# proAptiv: *Efficient Performance* on a Fully-Synthesizable Core

28 August 2012

Ranganathan "Suds" Sudhakar Chief Architect

© 2012 MIPS Technologies, Inc. All rights reserved.

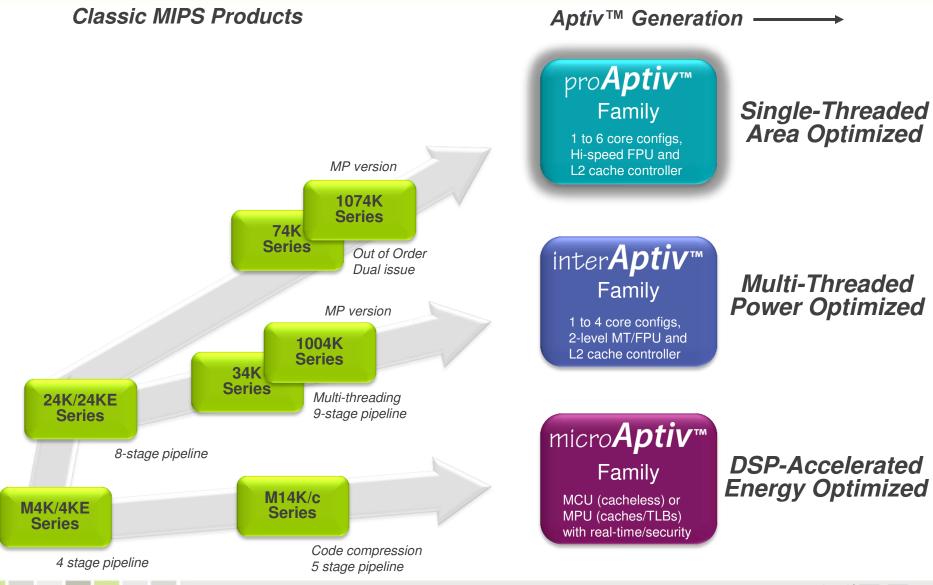

# **Aptiv Family Highlights**

## Three new cores optimized for embedded markets

# **Aptiv Core Portfolio**

# What is a "Soft" Core?

#### Fully synthesizable "package"

- Design data

- RTL

- Configurator MP/MT, FPU, Trace/Debug, cache/TLB/SPRAM/buffer sizes, bus widths

- Physical design support

- Reference floorplans, Synthesis + Place-and-Route scripts

- DFT/Scan, Timing and Power Analysis scripts

- Simulation models

- Bus Functional Models and compliance checkers

- Instruction accurate simulators, Cycle exact simulators

- Verification collateral

- Architectural Verification Test suites, core diagnostics

- Sample testbench, build and run scripts

- Documentation

- ISA manuals, global configuration register tables, memory maps, boot procedures

- Implementer's Guide, Integrator's Guide, Hardware/Software User manuals

#### Available separately

- FPGA development boards

- EJTAG/debug probes

- OS components, libraries, software toolchains (compiler, libraries, JITs, codecs)

# What is a "Hardened" Core?

### Tapeout-ready GDS, built on a generic ASIC flow, using:

- Configured soft core

- Floorplan placement of RAMs, bounding box

- Physical IP for some process technology

- Standard cell library

- e.g. 28nm low-leakage 12-track mixed-Vt with booster flops

- Compiled memories

- e.g. 28nm high-speed LVT single + dual-port bit-writable memories

- Fab conditions

- Process corner (usually worst-case slow-slow, high-temp, low voltage)

- Number of metal layers, DRC/LVS, power grid, IR drop, OCV/AOCV, PLL jitter

### Not to be confused with a "hard core"

- Frequency and power improvements beyond simple hardening:

- Custom std cells, flops, clk-gaters characterized for typical silicon

- e.g. 1.x GHz worst-case SVT  $\rightarrow$  2.x GHz typical with LVT, overdrive, cooling

- Multi-port register files and custom memories for cache arrays

- Hierarchical floorplans, structured placement, mesh clocking

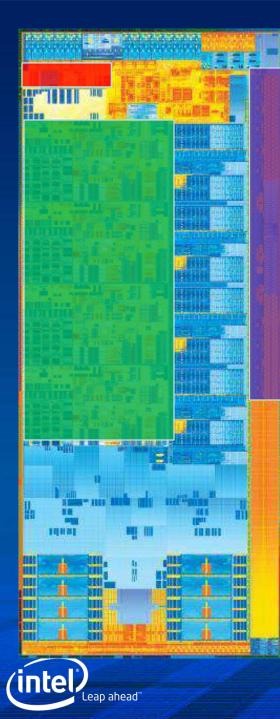

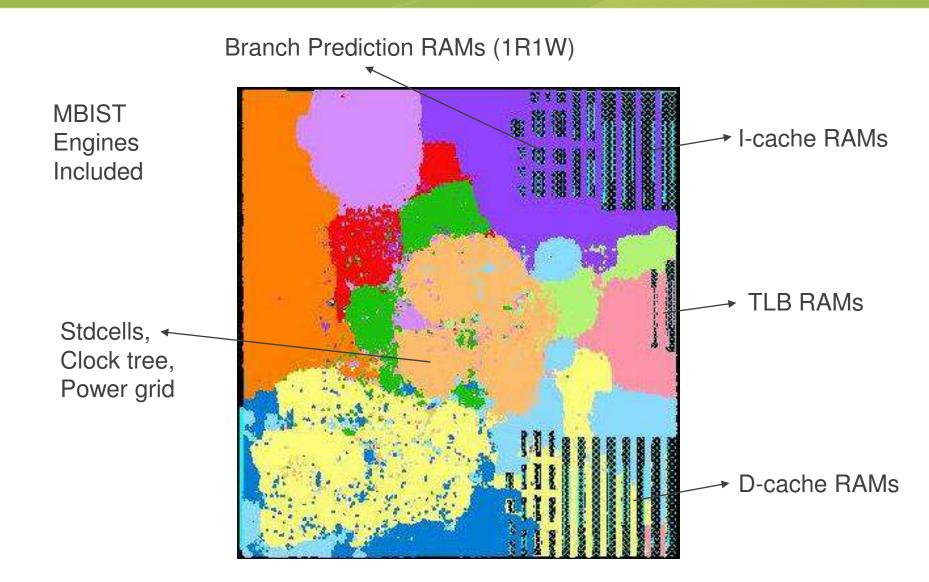

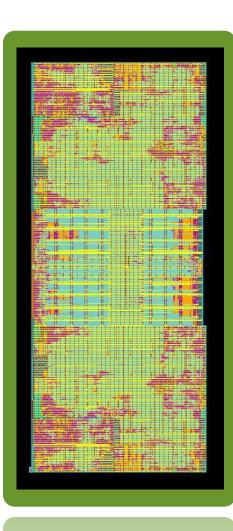

# Hardened proAptiv Layout

# **Soft Core Design Considerations**

### Life revolves around flops (and muxes)

- No CAMs schedulers, TLBs, BTBs all built from flops

- No ROMs div/sqrt lookup tables all built from gates

- No multiports Register files, reorder buffers all built from flops

- Read ports are large muxes ~O(num\_entries)

- Write ports are small muxes ~O(num\_ports)

- Exceptions are:

- 1RW RAMs for use in cache/TLB arrays

- 1R1W RAMs for use in branch prediction arrays

- Used judiciously -- proAptiv is the first MIPS soft core to use these

### Sophisticated techniques cannot be easily employed

- Banking, sum-addressing or one-hot-indexing

- Dynamic circuits, especially negedge-triggered

### More pipestages needed for a given frequency

MIPS's pure RISC ISA helps counteract this

# **Soft Core Timing and Verification Challenges**

### Timing paths not consistent

- Variations in floorplan, configuration, stdcell, memory IP

- Variations in operating point fab, process, Vt mix, overdrive

- Variations in EDA tool margins, flows, vendors and versions

### But good enough!

- Balance logic across pipestages

- Ensure loop paths are minimal and reflected in the microarchitecture

- Ensure floorplan reflects critical unit and pin placement

## Specific considerations for high-frequency pipelines

- Any CAM-RAM structures take at least 2 clock cycles

- Regfile read+bypass takes at least 2 clock cycles

- Need to fix timing paths at all phases of the implementation

- Synthesis, Place, Route, Clocking (No ECOs or manual tuning allowed)

- Verification challenges

- Dozens of configuration variables but still need high code+functional coverage

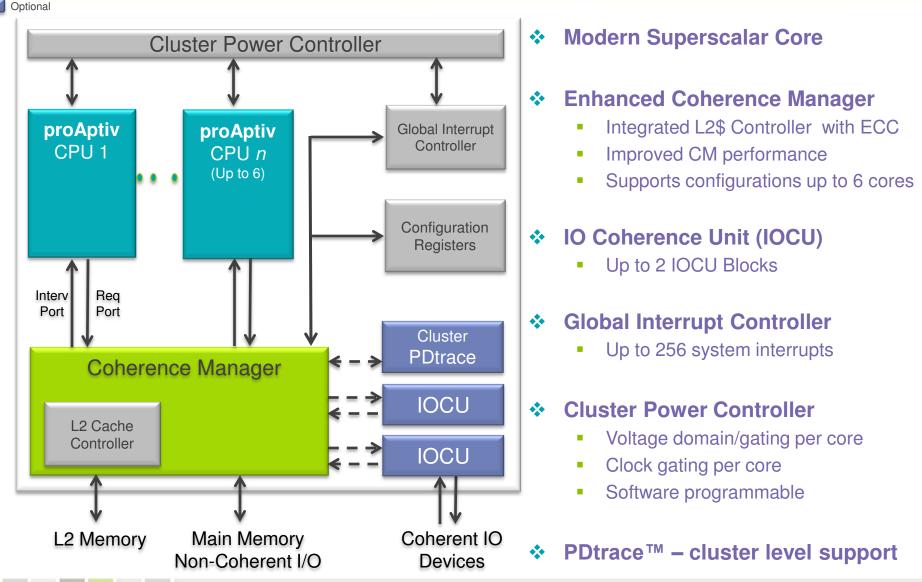

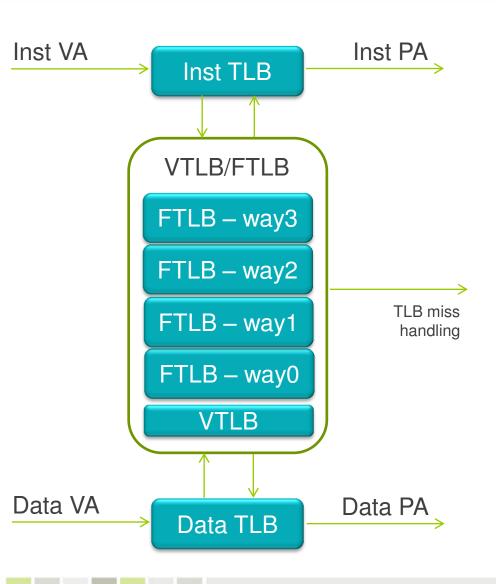

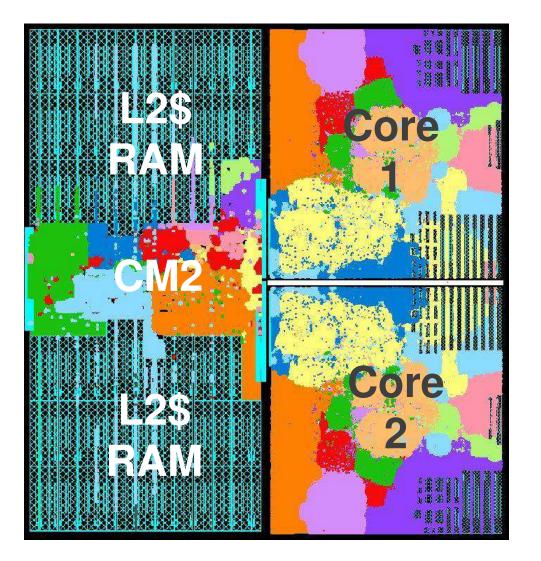

# proAptiv Coherent Processing System (CPS)

# proAptiv Design Goals

#### Fast

- Optimized for mobile computing and networking

- Multi-issue dynamically-scheduled operation

- Deep pipeline to achieve multi-gigahertz operation

- Brand new high-frequency FPU matched to core

#### Efficient

- Elegant balanced microarchitecture, not brute force width and depth

- Minimal area for cost and leakage; fine-grain clock gating

- Reduces the need for costly heterogeneous schemes

#### Scalable

New 6-core Coherence Manager and 256-bit L2 cache controller

#### Robust

- Age-based scheduling, careful tuning of predictors/prefetchers

- Easy to add features and performance, vary microarch parameters

#### Feature set

MIPS32 R3 / MIPS16e, DSP ASE v2, PDtrace v6, Enhanced VA

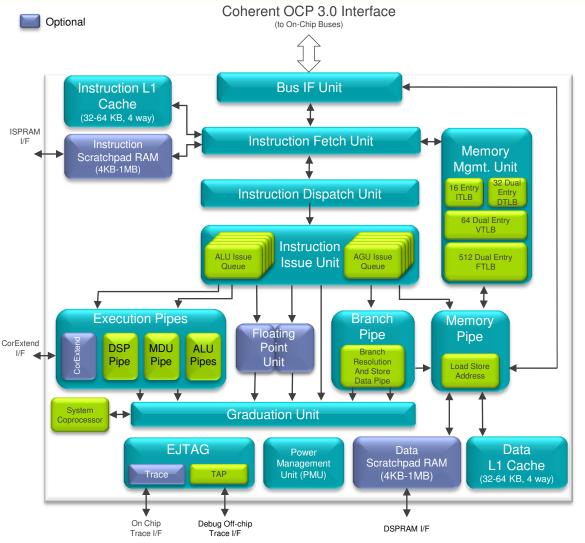

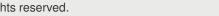

# proAptiv Base Core Architecture

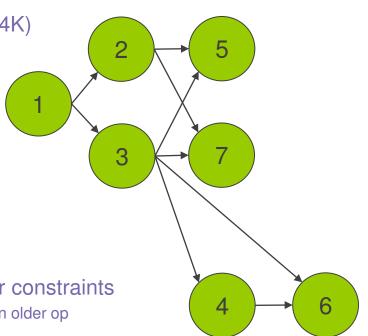

#### ✤ Superscalar OoO CPU – 16 stage

- Quad inst fetch

- Triple bonded dispatch

- Inst peak issue: quad integer; dual FP

- Sophisticated branch prediction and L0/L1/L2 BTBs, RPS, JRC, way predicted instruction cache

- High performance, multi-level TLBs, way predicted data cache

- Instruction Bonding makes six issue pipes look like eight

- Fast integer divide, multiply and multiply-accumulate operations

#### Dual Issue FPU

- Higher speed (1:1 with CPU)

- Lower latency on most operations

- Single-pass double precision

- More parallelism and dedicated schedulers – more ops in flight

# proAptiv Pipeline

# 16 stage integer load pipeline

| Instruction Fetch<br>Branch Prediction | Bonded<br>Dispatch | Issue<br>Regread                                    | Agen<br>Dcache                   | Regwrite<br>Graduate |

|----------------------------------------|--------------------|-----------------------------------------------------|----------------------------------|----------------------|

| 4 cycles                               | 2 cycles           | 4 cycles                                            | 4 cycles                         | 2 cycles             |

|                                        |                    | Floating-Point<br>Decode, Rename,<br>Issue, Regread | FADD<br>FMUL                     | Regwrite<br>Graduate |

|                                        |                    | 4 cycles                                            | 4 cycles                         | 2 cycles             |

|                                        |                    |                                                     | User Defined<br>Instruction Unit | Regwrite<br>Graduate |

|                                        |                    |                                                     | Variable cycles                  | 2 cycles             |

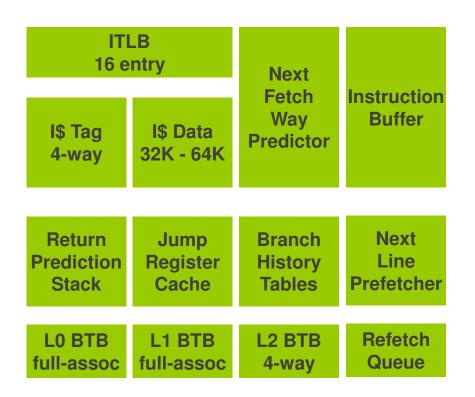

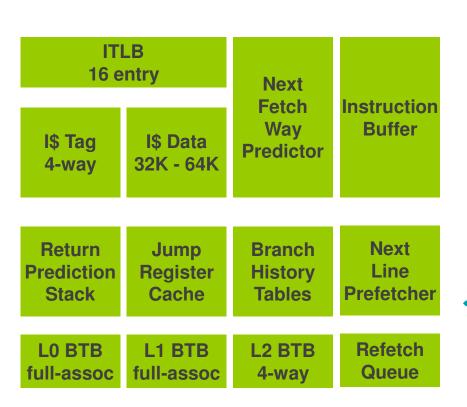

# **proAptiv Instruction Fetch**

- 16-entry ITLB

- ✤ 32 or 64KB I-cache

- ✤ 4-way associative LRU

- ✤ 32-byte line

- Parity protected

- Fetches 16 bytes per cycle

- Aligned fetch reduces power

- Dynamic 8 byte bundle reduces power on branches or MIPS16e

- Next Fetch Way predictor reduces power by reading only one way

- Sequential fetch way from SRAM

- Target way from BTB

- Next Line Prefetcher

- Variable number of lines on a miss

- Direct bypass from refetch queue

- Extra pipestages inserted for MIPS16e fetching and unpacking

- Credit-based instruction buffer

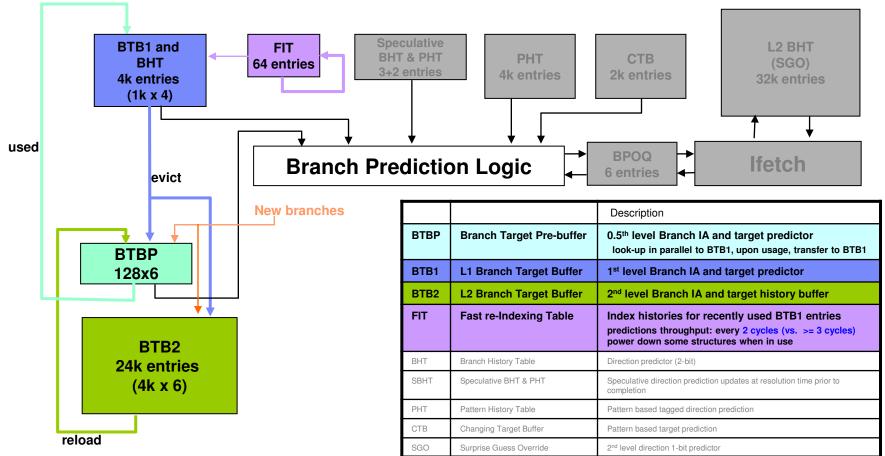

# **proAptiv Branch Prediction**

#### Branch History Tables

- Predicts branch direction

- Novel algorithms deliver class-leading prediction accuracy

- Uses sophisticated global history

- Can predict 2 (MIPS32) or 4 (MIPS16e) branches per cycle

- Multiple SRAM-based tables

- Only 1R1W structures on chip

- Leverages delay slots to minimize storage capacity needed

- In MIPS, unlike some ISAs, the delay slot cannot itself be a branch

#### Branch Target Buffers

- Provides fast target prediction

- Multiple buffers with various latencies and sizes, up to 512 entry 4-way

#### Jump Register Cache

- Predicts indirect jumps

- Multiple targets per jump PC

- Return Prediction Stack

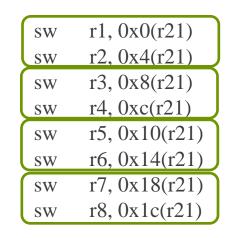

# proAptiv Instruction Dispatch – Bonding

### Combine adjacent instructions into single bonded op

- e.g. consecutive LW or SW instructions

- e.g. branch with certain instructions in delay slot

- Fused compare-branch is already part of MIPS integer ISA

#### Load/Store bonding makes one memory pipe look like two

- 1 DTLB, 1 tag array, single-ported data array saves area

- Single DTLB and cache access saves energy, power

- Occupies only 1 entry in various queues/buffers more ILP

- Carried forward as one operation on L1-miss more MLP

- Speeds memset, bcopy, strcmp, spill-fill, GPU communication

#### Design decisions

- Initially limit to two instructions, aligned addresses and ST

- But designed to scale to four, misaligned accesses and MT

- Therefore, needs a *bonding predictor* in the front-end

- Trained by LSU (memtype must be cacheable or write-combining)

- Indexed by PC and other control flow information

| Mei | nCo | py Loop:      |

|-----|-----|---------------|

|     | lw  | r1, 0x0(r20)  |

|     | lw  | r2, 0x4(r20)  |

|     | lw  | r3, 0x8(r20)  |

|     | lw  | r4, 0xc(r20)  |

|     | lw  | r5, 0x10(r20) |

| ο   | lw  | r6, 0x14(r20) |

|     | lw  | r7, 0x18(r20) |

|     | lw  | r8, 0x1c(r20) |

| addiu | r20, r20, 0x20 |

|-------|----------------|

| addiu | r21, r21, 0x20 |

| bnez  | r23, Loop      |

| sub   | r23, r23, r22  |