### Tutorial Day Monday, August 27, 2012

| 9:30 am         | Tutorial 1                                                     | (The Evolut  | tion of                        | ) Mobile SoC Programming               |  |

|-----------------|----------------------------------------------------------------|--------------|--------------------------------|----------------------------------------|--|

| 9:00 am - 10:40 | Mobile SOCs: Connecting Hardware to Apps                       |              | to                             | Neil Trevett from Khronos              |  |

| 10:40 - 11:10   | BREAK                                                          |              |                                |                                        |  |

| 11:10 – 11:25   | Camera and Video                                               |              |                                | Sean Mao, <b>ArcSoft</b>               |  |

| 11:25 – 11:40   | Vision and Gesture Processing                                  |              |                                | Itay Katz, Eyesight                    |  |

| 11:40 – 11:55   | Augmented Reality                                              |              |                                | Ben Blachnitzky, Metaio                |  |

| 11:55 – 12:10   | Sensor Fusion                                                  |              |                                | Jim Steele, <b>Sensor</b><br>Platforms |  |

| 12:10 – 12:25   | 3D Gaming                                                      |              | Daniel Wexler, the11ers        |                                        |  |

| 12:25 – 1:00 pm | Panel                                                          |              |                                |                                        |  |

| 1:00 – 2:00pm   | Lunch                                                          |              |                                |                                        |  |

| 2:00 pm         | Tutorial 2                                                     | Die Stacking |                                |                                        |  |

| 2:00 – 2:15     | Introduction Li                                                |              | Liam                           | iam Madden, <b>Xilinx</b>              |  |

| 2:15 – 2:40     | Foundry TSV Enablement For 2.5D/3D Chip Stacking               |              | Remi Yu, <b>UMC</b>            |                                        |  |

| 2:40 - 3:05     | Full Processing Interposer Process                             |              | Choo                           | Choon Lee, <b>Amkor</b>                |  |

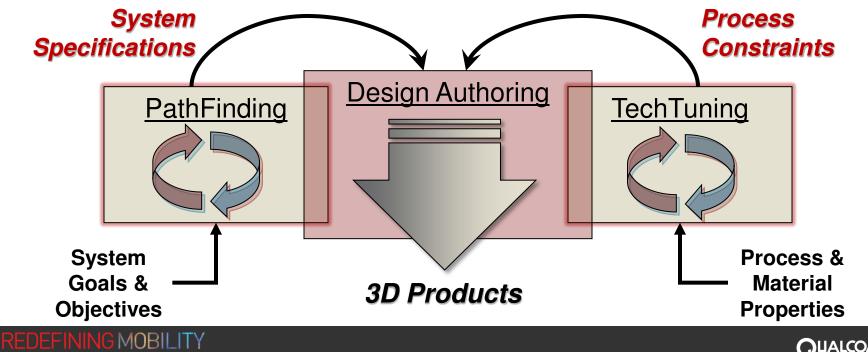

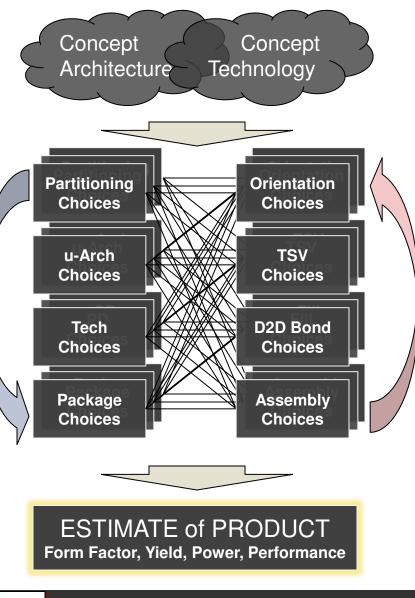

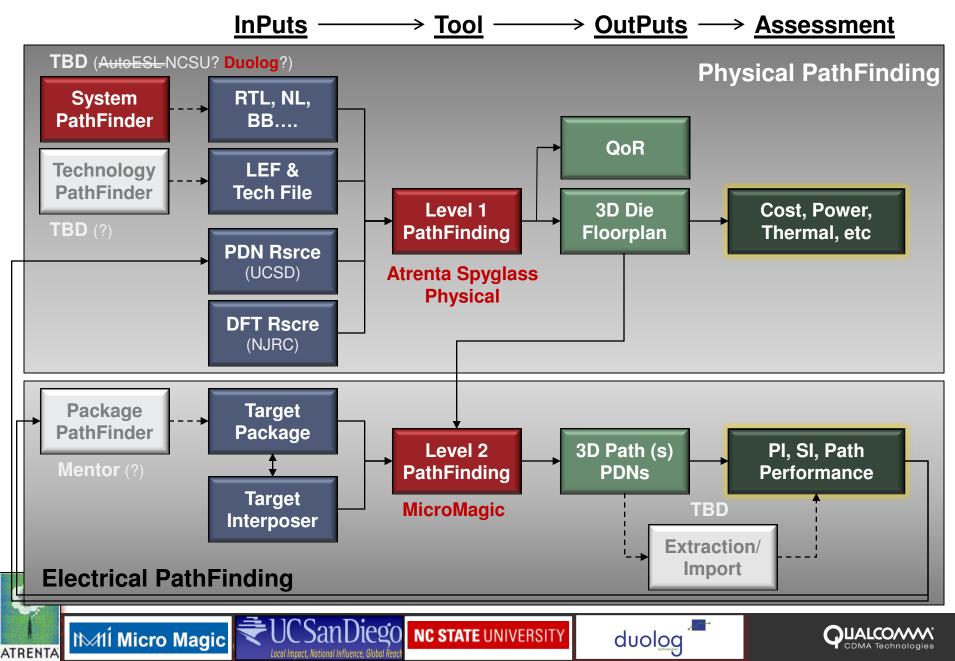

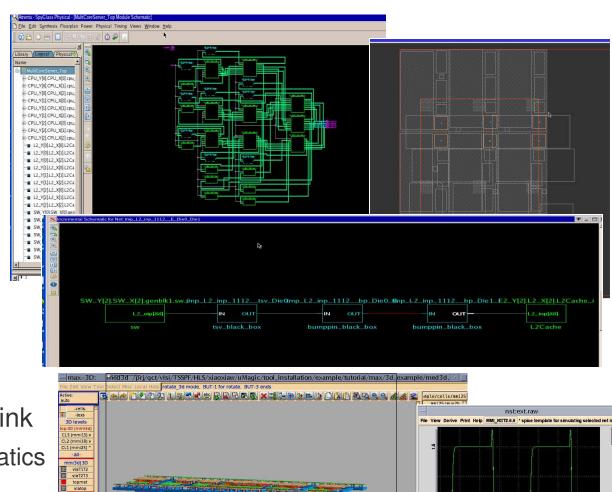

| 3:05 – 3:30     | Roadmap for Design and EDA<br>Infrastructure for 3D Products   |              | Riko Radojcic, <b>Qualcomm</b> |                                        |  |

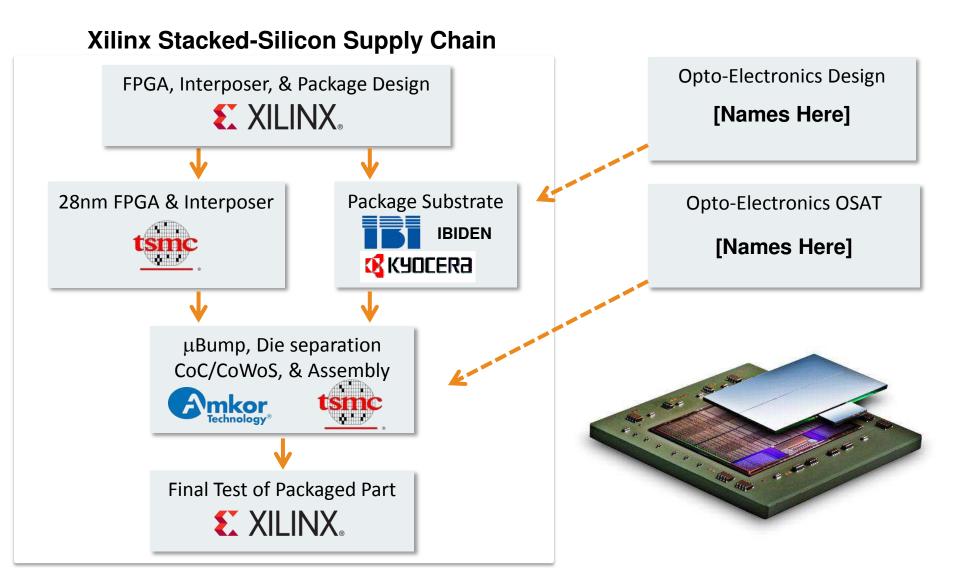

| 3:30 – 3:55     | Xilinx SSI Technology: Concept to Silicon Development Overview |              | Shankar Lakka, <b>Xilinx</b>   |                                        |  |

| 3:55 – 4:10     | BREAK                                                          |              |                                |                                        |  |

| 4:10 – 4:35     | Memory Consideration and<br>Heterogeneous Die                  |              | Bryan Black, <b>AMD</b>        |                                        |  |

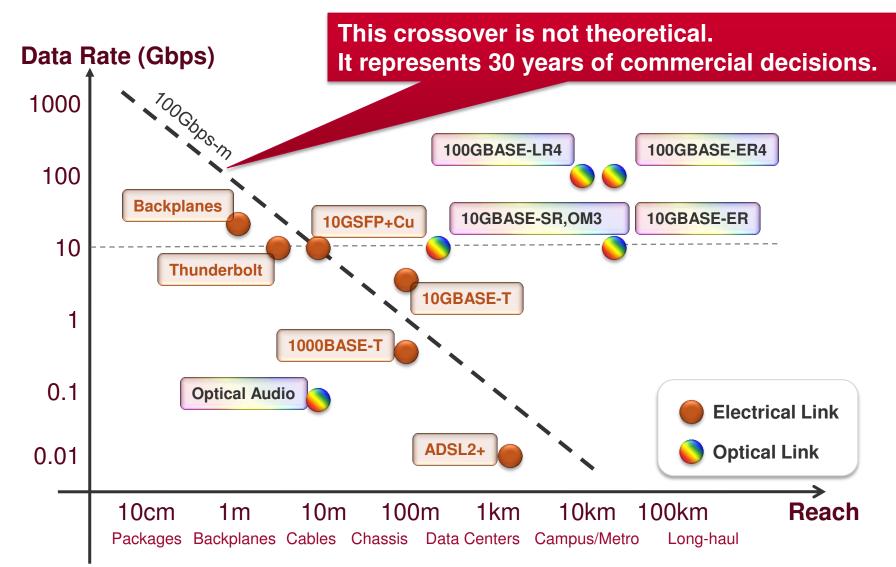

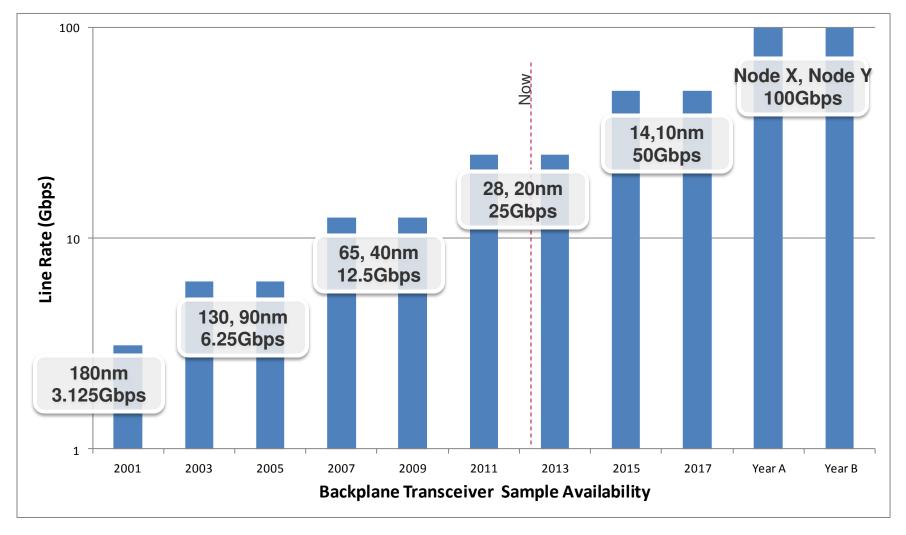

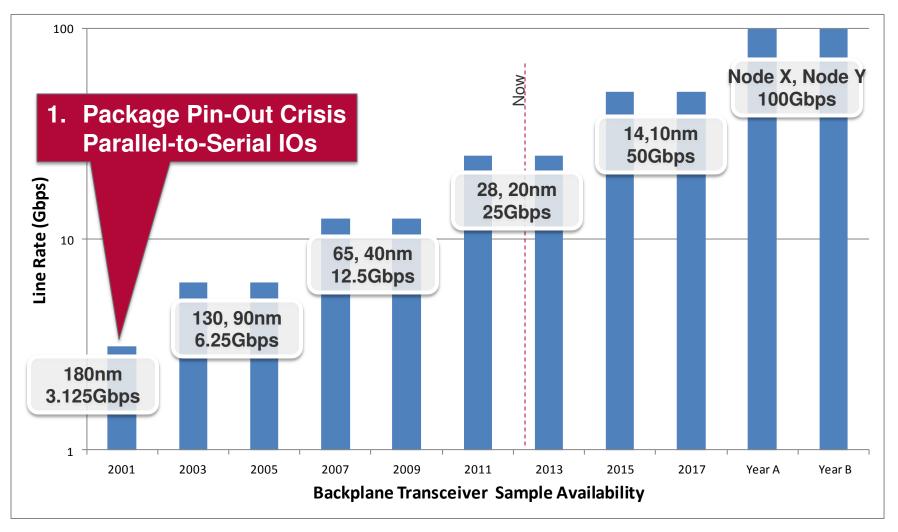

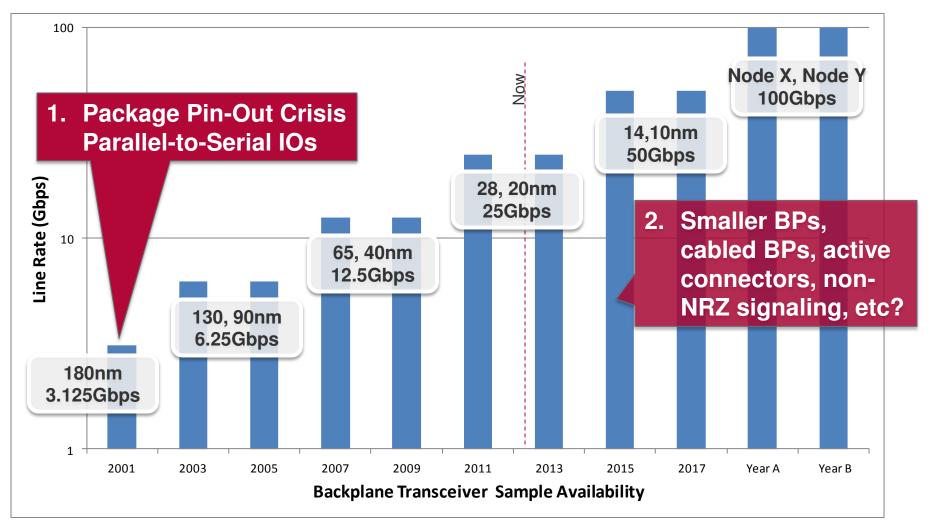

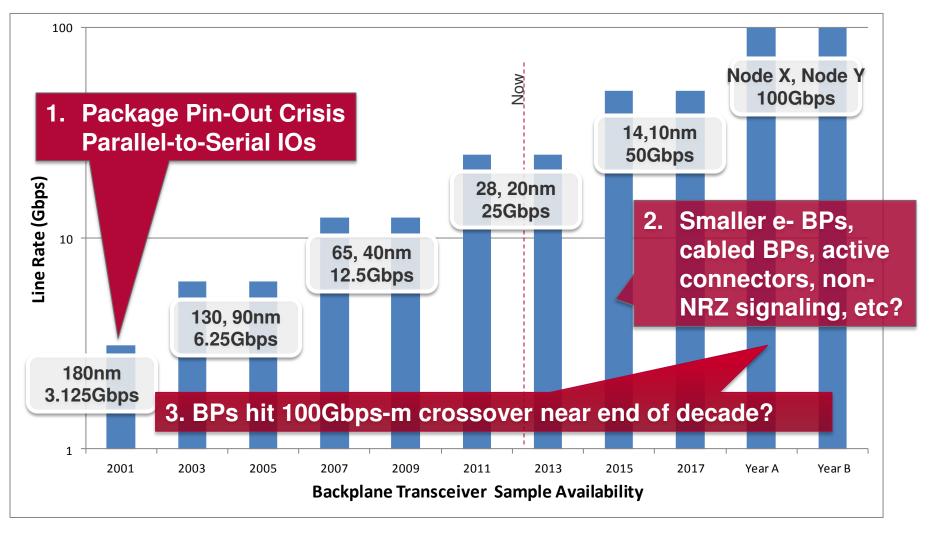

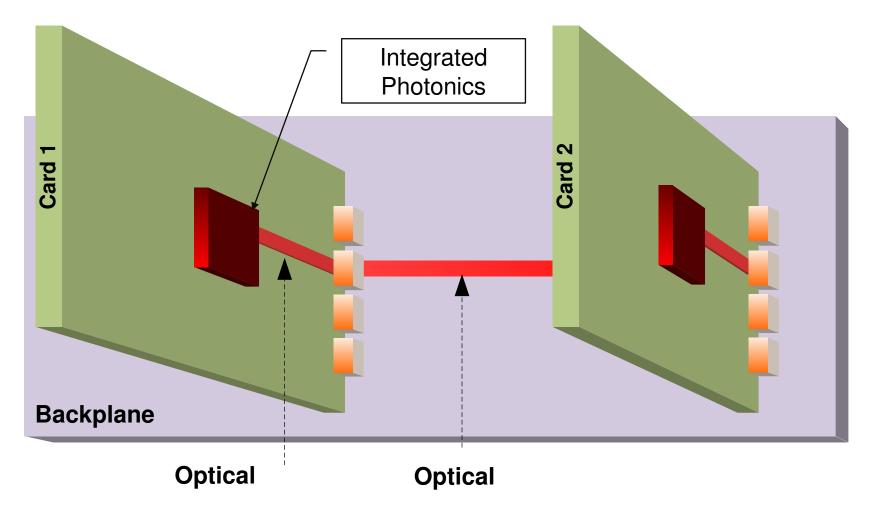

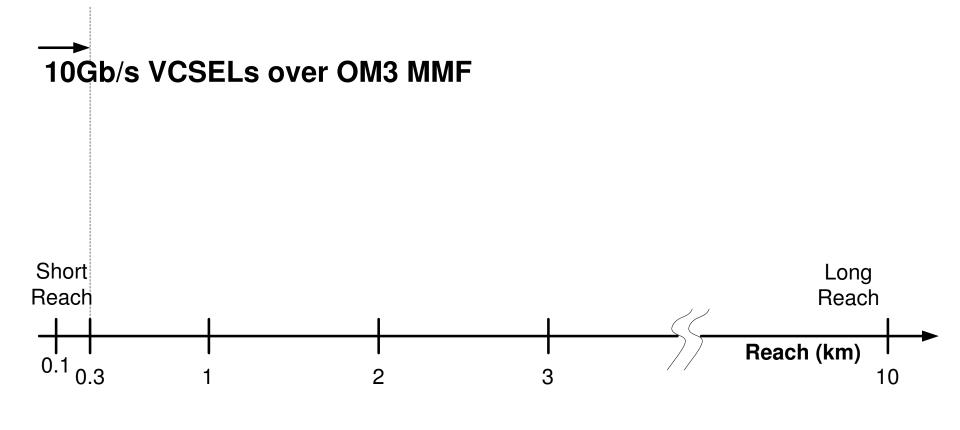

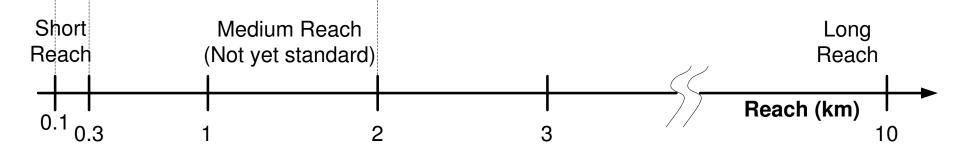

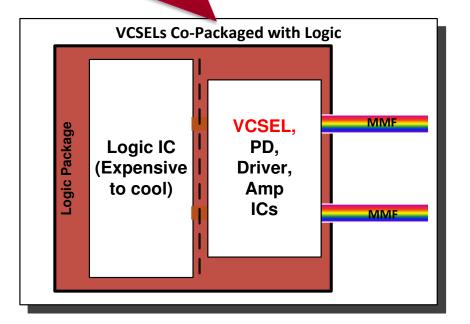

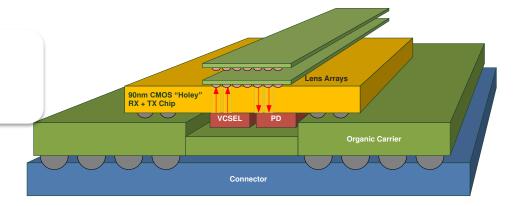

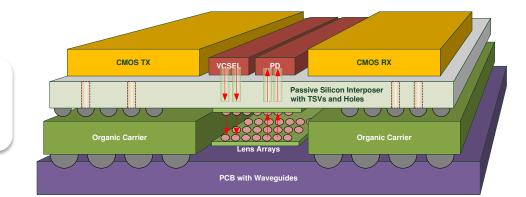

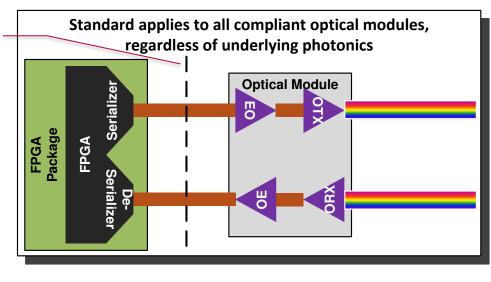

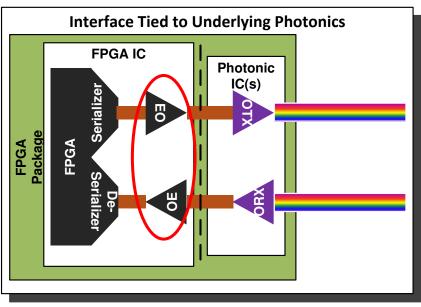

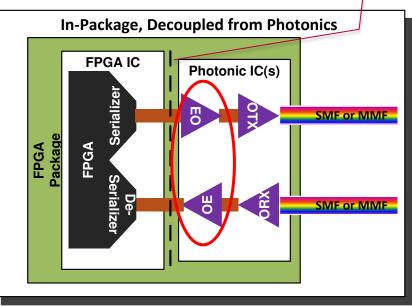

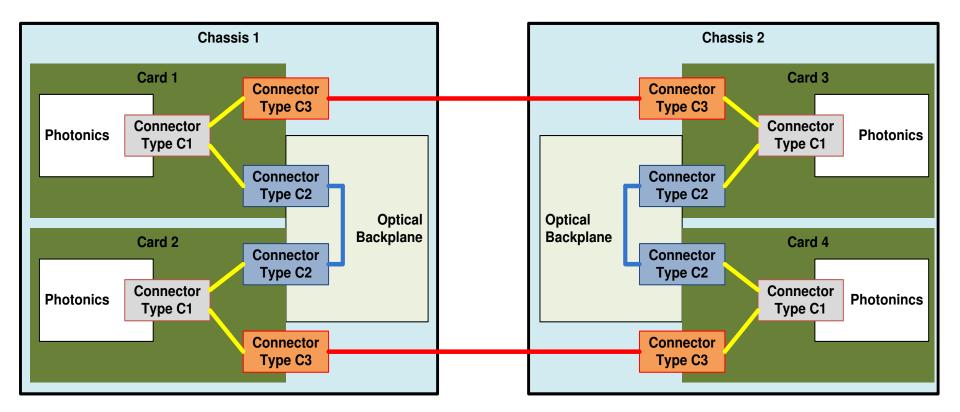

| 4:35 – 5:00     | Optical Backplanes with 3D<br>Integrated Photonics?            |              | Ephrem Wu, Xilinx              |                                        |  |

| 5:00 – 5:30     | Panel                                                          |              |                                |                                        |  |

| 5:30 – 7:00 pm  | Reception                                                      |              | •                              |                                        |  |

# SOC Programming Tutorial Hot Chips 2012 Neil Trevett Khronos President

# Welcome!

### • An exploration of SOC capabilities from the programmer's perspective

- How is mobile silicon connecting to mobile software?

### • Mobile ecosystems and the programming APIs they provide

- Mobile OS and open standards for SOC acceleration

# SOC innovation hotspots

Vision and gesture processing, Augmented Reality, Sensor Fusion Photography and Video Processing, 3D Graphics

# Illustrate the state of the art in mobile programming

- AND highlight the issues and challenges still be to solved

# **Speakers**

| Session                                | Speaker         | Company          | Title                                             |

|----------------------------------------|-----------------|------------------|---------------------------------------------------|

| Connecting Mobile SOC Hardware to Apps | Neil Trevett    | Khronos          | Khronos President and NVIDIA VP of Mobile Content |

| Break                                  |                 | Break            |                                                   |

| Camera and Video                       | Sean Mao        | ArcSoft          | VP Marketing, Advanced Imaging Technologies       |

| Vision and Gesture Processing          | Itay Katz       | Eyesight         | Co-Founder & CTO                                  |

| Augmented Reality                      | Ben Blachnitzky | Metaio           | Director of R&D                                   |

| Sensor Fusion                          | Jim Steele      | Sensor Platforms | VP Engineering                                    |

| 3D Gaming                              | Daniel Wexler   | the11ers         | СХО                                               |

| Panel Session                          |                 | All Speakers     |                                                   |

# **Khronos Connects Software to Silicon**

### Khronos APIs define processor acceleration capabilities

- Graphics, video, audio, compute, vision and sensor processing

# **APIs BY the Industry FOR the Industry**

### Khronos APIs define core device acceleration functionality

- Low-level "Foundation" functionality needed on every platform

- Rigorous conformance tests for cross-vendor consistency

### Khronos standards have strong industry momentum

- 100s of man years invested by industry leading experts

- Shipping on billions of devices and multiple operating systems

# • Khronos is OPEN for any company to join and participate

- Standards are truly open one company, one vote

- Solid legal and Intellectual Property framework for industry cooperation

- Khronos membership fees to cover expenses

### Khronos standards are FREE to use

- Members agree to not request royalties

# • Khro

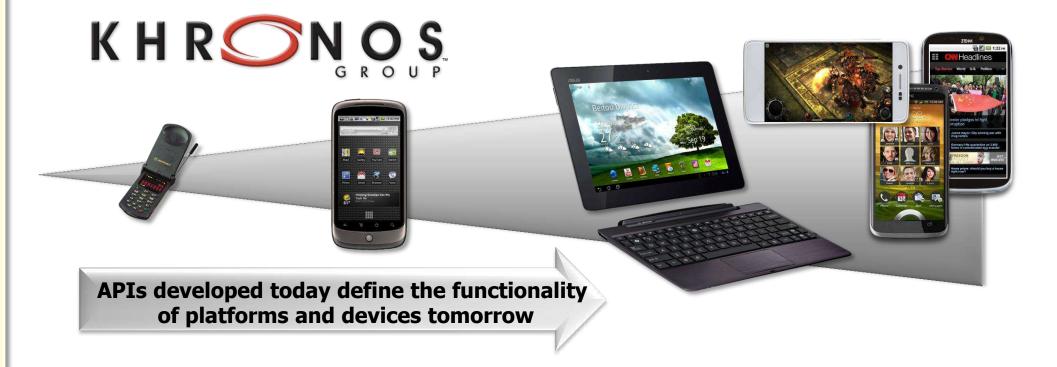

# **API Standards Evolution**

EGI

Diverse platforms – mobile, TV, embedded – means HTML5 will become increasingly important as a universal app platform

S O C N C S O C N

HR

$\mathbf{X}$

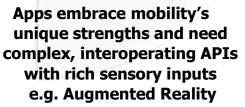

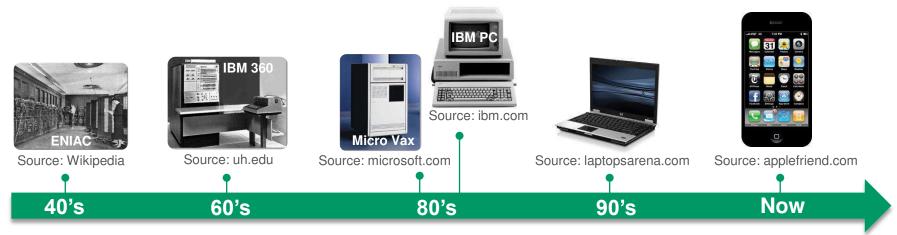

# **A New Era in Computing**

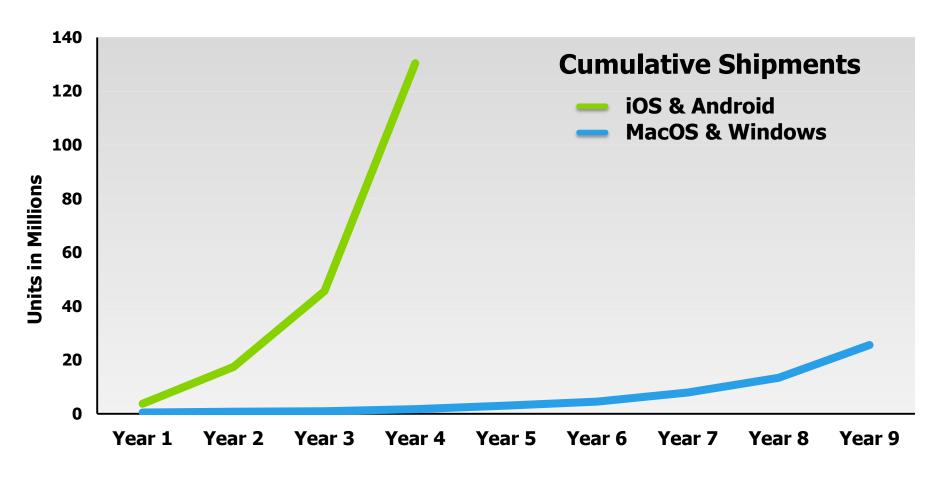

# **20 Years Faster to 100M Per Year**

Source: Gartner, Apple, NVIDIA

K H R O N O S

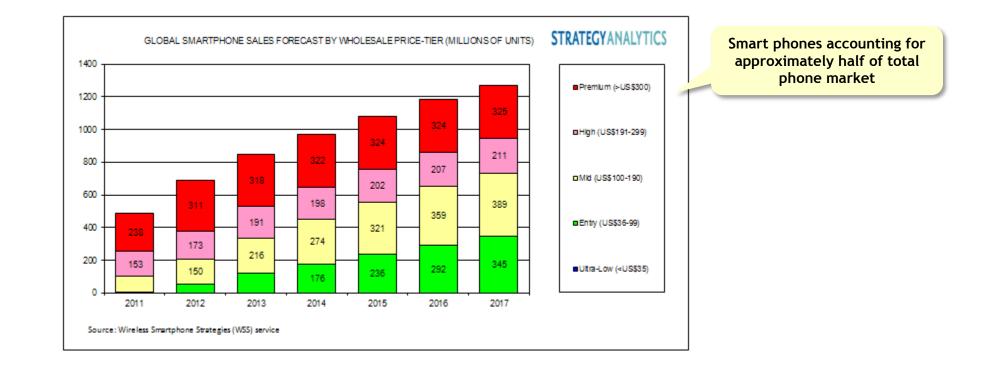

# **The Largest Market Ever**

### • IDC - 1.8 billion mobile phones will ship in 2012

- By the end of 2016, 2.3 billion mobile phones will ship per year

K H R N N S

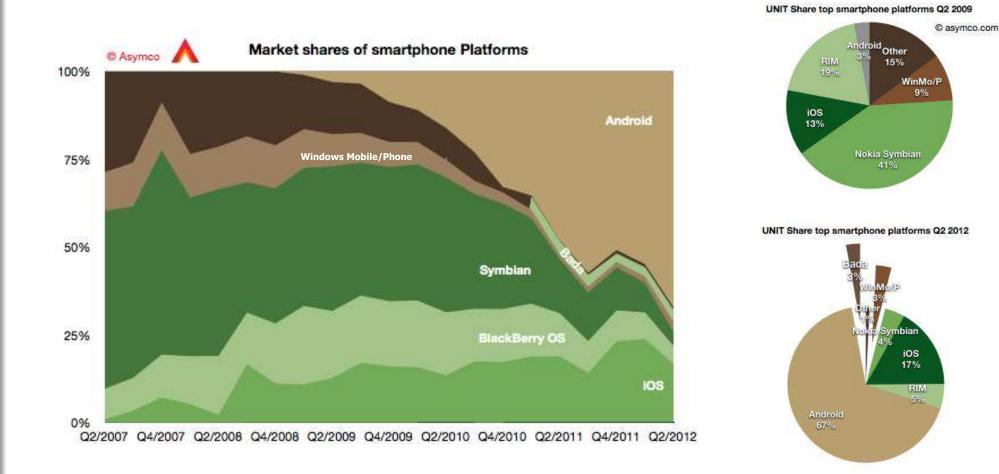

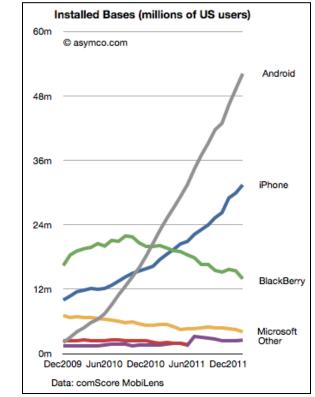

# **Global Smartphone Market Share**

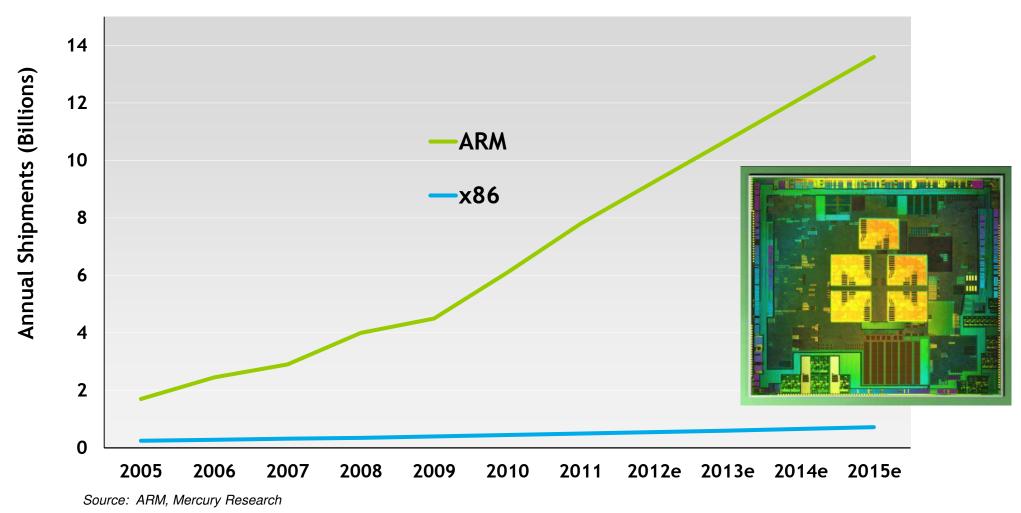

# **ARM is Licensable and Pervasive**

K H R O N O S

HR

$\mathbf{X}$

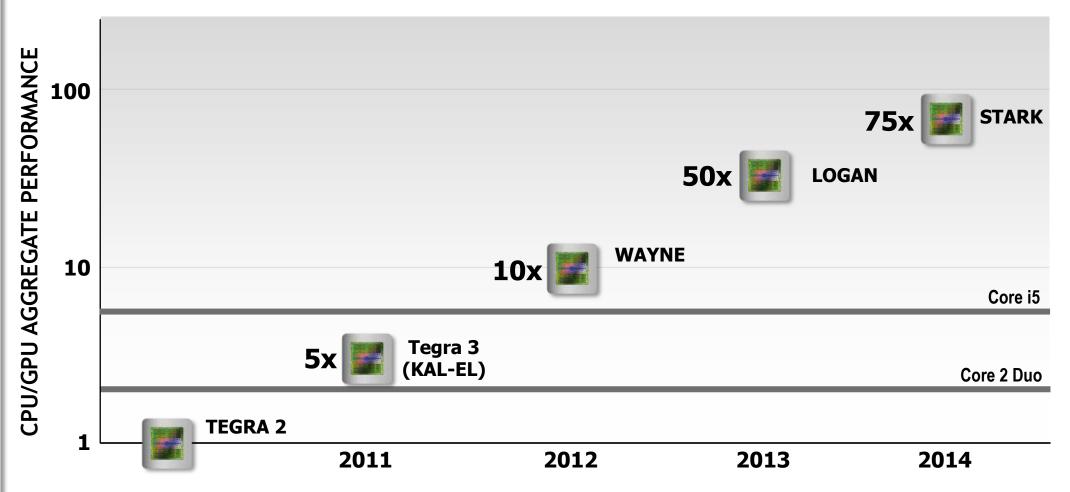

# **Mobile Performance Increases**

# **Power is the New Design Limit**

### The Process Fairy keeps bringing more transistors

- Transistors are getting cheaper

- But the Process Fairy isn't helping as much on power as in the past

- The End of Voltage Scaling

In the Good Old Days

Leakage was not important, and voltage scaled with feature size

$$L' = L/2$$

$V' = V/2$

$E' = CV^2 = E/8$

$f' = 2f$

$D' = 1/L^2 = 4D$

$P' = P$

Halve L and get 4x the transistors and 8x the capability for

the same powe

**The New Reality** Leakage has limited threshold voltage, largely ending voltage scaling

> L' = L/2 V' = ~V  $E' = CV^2 = E/2$  f' = ~2f  $D' = 1/L^2 = 4D$ P' = 4P

Halve L and get 4x the transistors and 8x the capability for Ax the nowerly

K H RONOS

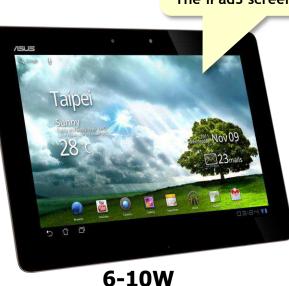

# **Mobile Thermal Design Point**

Resolution makes a difference! The iPad3 screen takes up to 8W

10" Screen takes 1-2W

30-90W

Max power the system can use and not break down Even as battery technology improves - these thermal limits remain

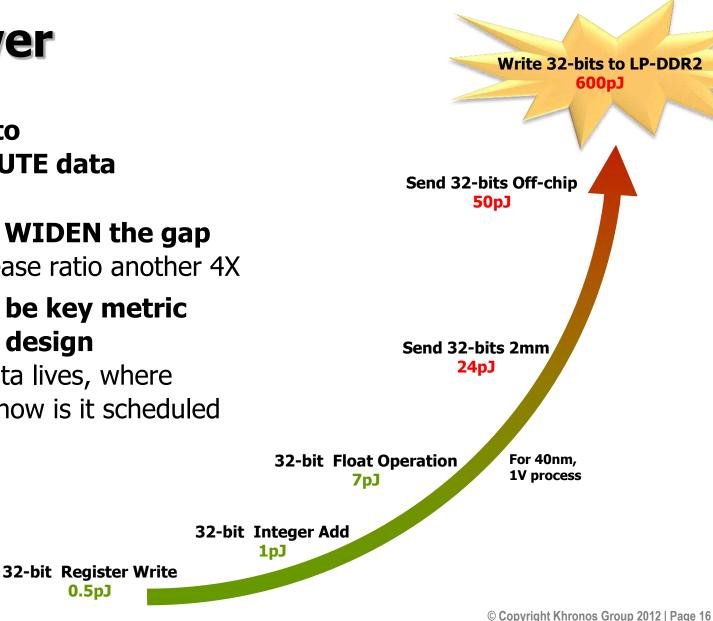

# **Apps and Power**

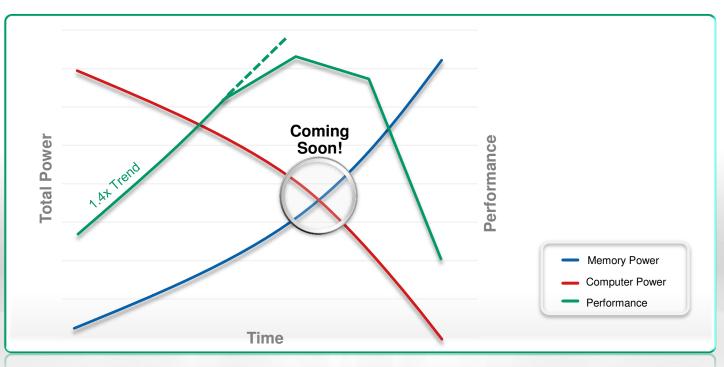

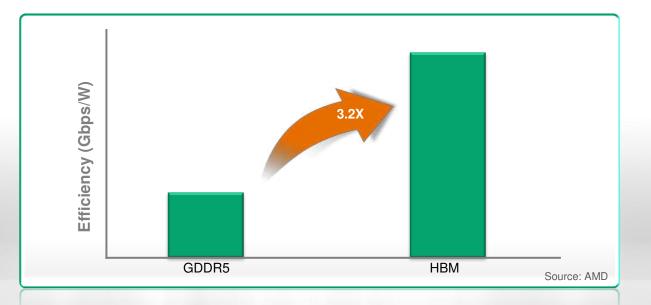

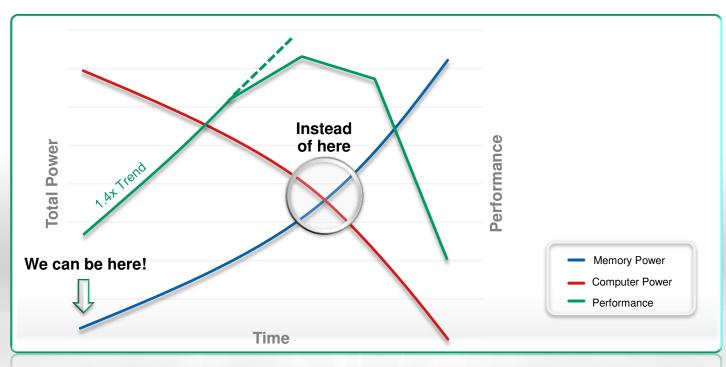

- Much more expensive to **MOVE data than COMPUTE data**

- Process improvements WIDEN the gap

- 10nm process will increase ratio another 4X

- Energy efficiency must be key metric during silicon AND app design

- Awareness of where data lives, where computation happens, how is it scheduled

0.5pJ

S O N N

2

I

# **Energy Optimization Opportunities**

### Dark Silicon

- Lots of space for transistors just can't turn them all on at same time

- Multiple specialized hardware units that are only turned on when needed

- Increase locality and parallelism of computation to save power

# Dynamic and feedback-driven software power optimization

- Instrumentation for energy-aware compilers and profilers

- Most compilers just look at one thread, take a more global view

- Power optimizing compiler back-end / installers

# Smart, holistic use of sensors and peripherals

- Motion sensors, cameras, networking, GPS

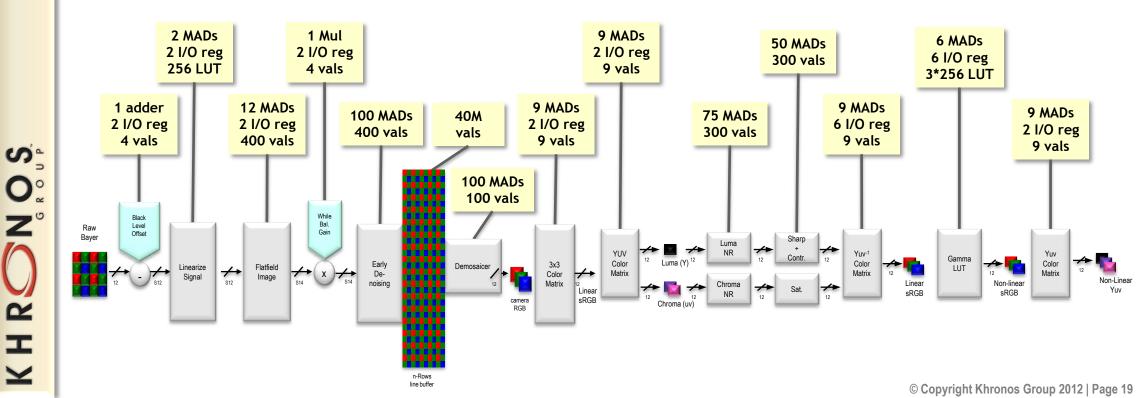

# **Camera Sensor Processing**

# • CPU

- Single processor or Neon SIMD

- Makes heavy use of general memory

### • GPU

- Many way parallelism

- Efficient image caching into general memory

- Programmable and flexible

- Still significant use of cache/memory

### • Camera ISP = Image Signal Processor

- Scan-line-based

- Data flows through compact hardware pipe

- No global memory used to minimize power

- Little or no programmability

# **Typical Camera ISP**

- ~760 math Ops

- ~42K vals = 670Kb

- 300MHz → ~250Gops

ິ

0° 2°

2

I

$\mathbf{\Sigma}$

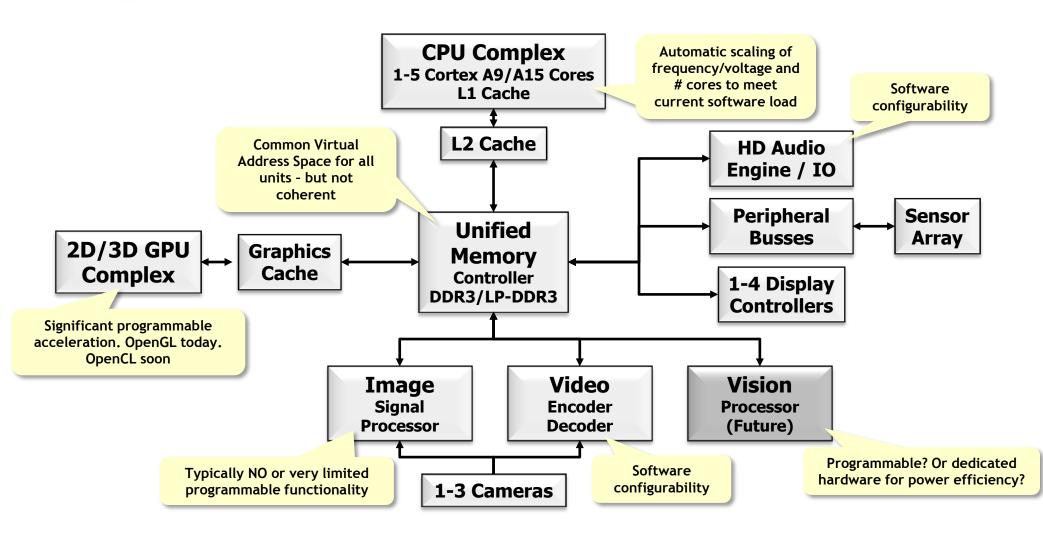

# **Programmers View of a Typical SOC**

ທີ

**O**<sup>°</sup>

Z

2

Т

$\mathbf{\Sigma}$

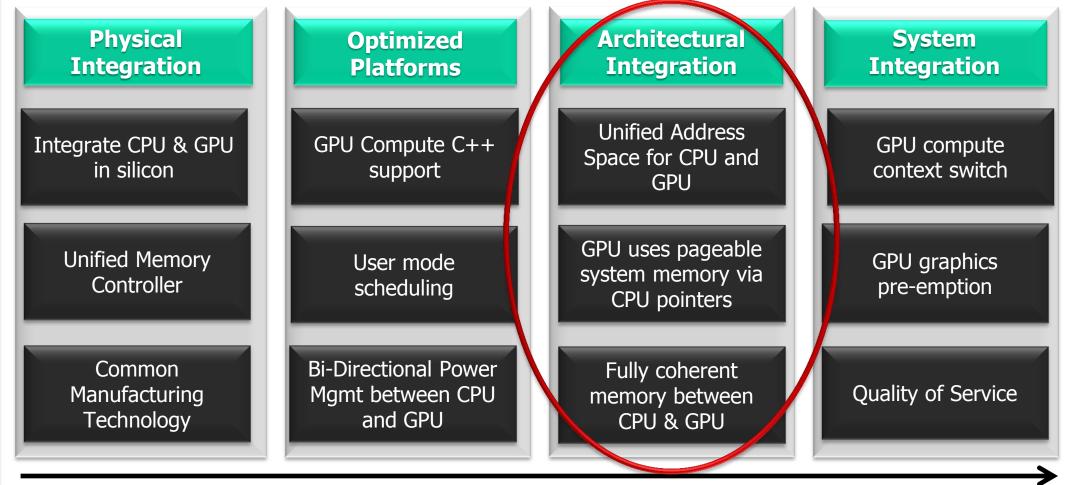

# **HSA Feature Roadmap**

Heterogeneous System Architecture Foundation: AMD, ARM, Imagination, TI, MediaTek

Time

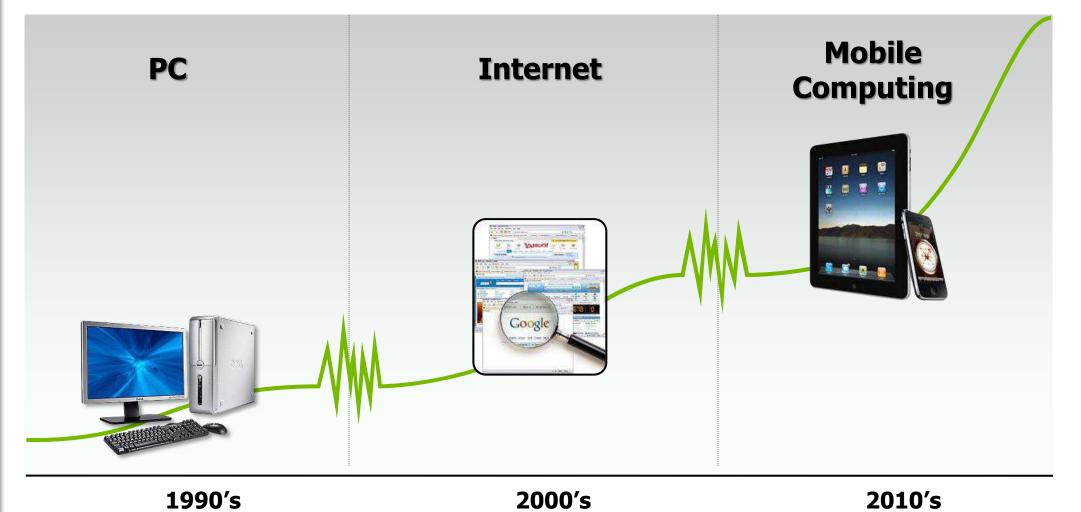

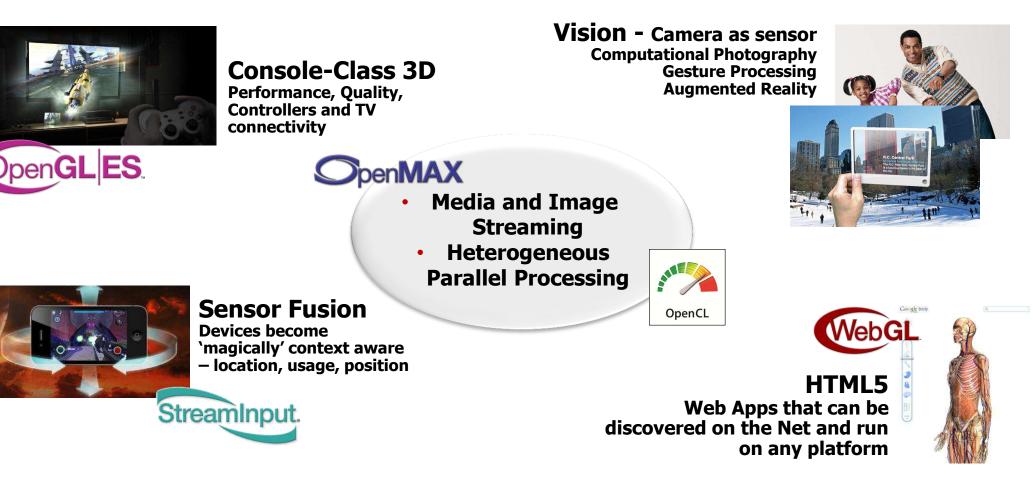

# **Mobile Innovation Hot Spots**

### New platform capabilities being driven by SILICON and APIs

K H R O N O S

$\mathbf{\Sigma}$

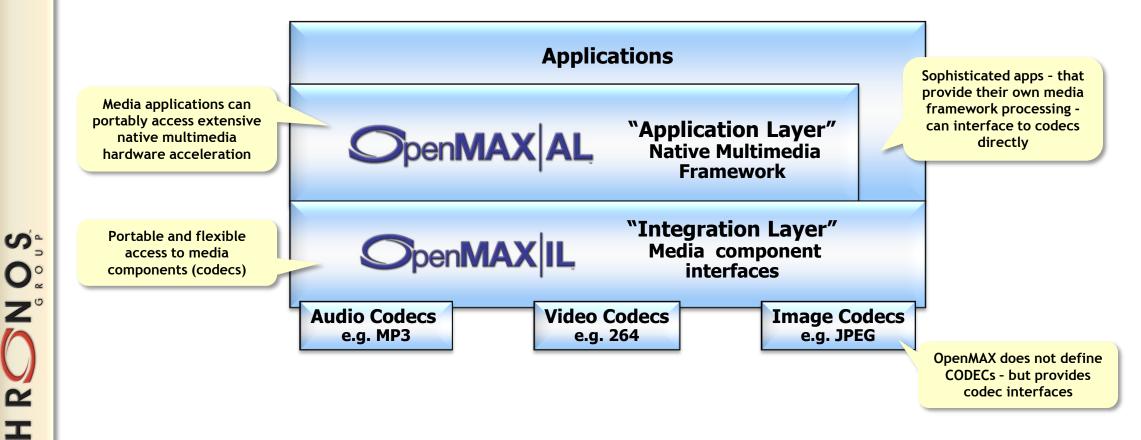

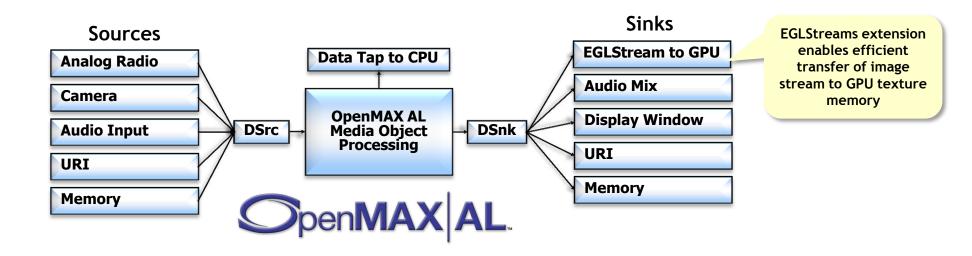

# **OpenMAX - Media Acceleration**

### Royalty-free , cross-platform open standards

# **OpenMAX AL Streaming Media Framework**

### • Enables key video, image stream and camera use cases

- Enables optimal hardware acceleration with app portability

# Create Media Objects to play and process images and video with AV sync

- Connect to variety of input and output objects to PLAY and RECORD media

# • Full range of video effects and controls

- Including playback rate, post processing, and image manipulation

K H R O N O S

DRM

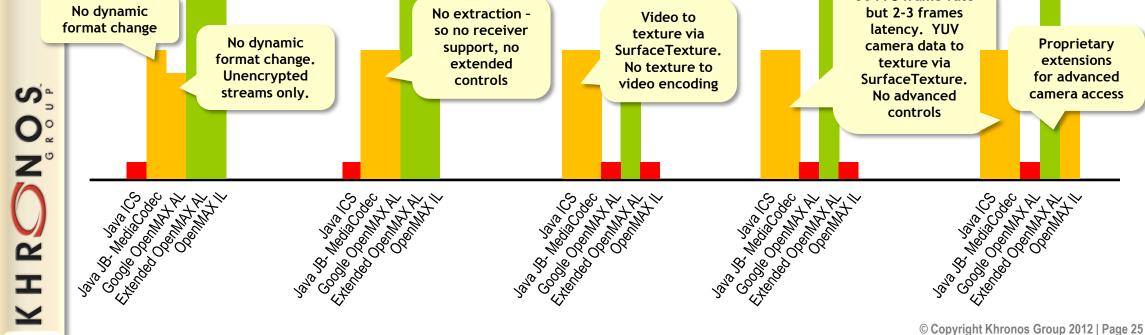

# **Accelerating Streaming Media**

Video

Augmented

**HD Video**

### Movies Teleconferencing Editing Reality Inject encrypted Inject video into decode/render Video decoding High frame-rate, low ٠ elementary streams into Extract video from capture/render to texture latency camera capture decrypt/decode/render · Extended controls (fine-grained Texture to video to app and GPU texture **Dynamic format changes** codec query/config, force key Advanced camera encoding Support for Widevine frames) control over format. ROI 30 FPS frame-rate No extraction -Video to so no receiver texture via No dynamic support, no SurfaceTexture. format change. extended No texture to Unencrypted controls video encoding streams only.

### Computational **Photography**

Fast, low latency camera capture to app and GPU texture Advanced camera control over format. bracketed burst mode with sequenced key/value pairs

Proprietary

extensions

for advanced

camera access

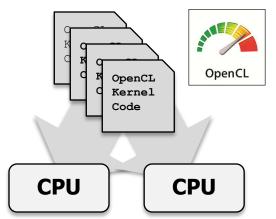

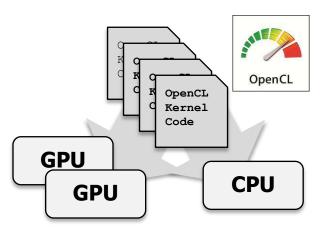

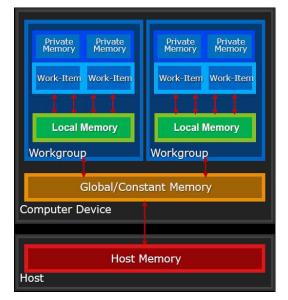

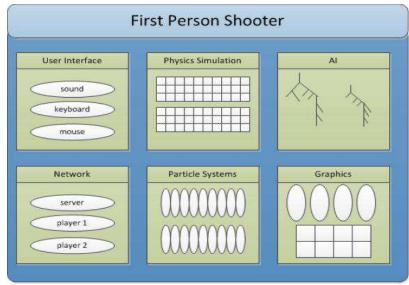

# **OpenCL – Heterogeneous Computing**

- Native framework for programming diverse parallel computing resources

- CPU, GPU, DSP as well as hardware blocks(!)

### Powerful, low-level flexibility

- Foundational access to compute resources for higher-level engines, frameworks and languages

### Embedded profile

- No need for a separate "ES" spec

- Reduces precision requirements

One code tree can be executed on CPUs or GPUs

S O S O S O S O S

2

I

$\mathbf{\Sigma}$

# **OpenCL Overview**

# C Platform Layer API

- Query, select and initialize compute devices

# Kernel Language Specification

- Subset of ISO C99 with language extensions

- Well-defined numerical accuracy IEEE 754 rounding with specified max error

- Rich set of built-in functions: cross, dot, sin, cos, pow, log ...

# • C Runtime API

- Run-time or build-time compilation of kernels

- Execute compute kernels across multiple devices

# Memory management is explicit

- Application must move data from host → global → local and back

- Implementations can optimize data movement in Unified memory systems

# **OpenCL: Execution Model**

### Kernel

- Basic unit of executable code ~ C function

- Data-parallel or task-parallel

### Program

Collection of kernels and functions ~ dynamic library with run-time linking

### Command Queue

- Applications queue kernels & data transfers

- Performed in-order or out-of-order

### • Work-item

An execution of a kernel by a processing element

~ thread

### • Work-group

A collection of related work-items that execute on a single compute unit ~ core

### Example of parallelism types

S S

# **Custom Devices and Built-in Kernels**

- Embedded platforms often contain specialized hardware and firmware

- That cannot support OpenCL C

- Built-in kernels can represent these hardware and firmware capabilities

- Such as video encode/decode, camera ISP

- Hardware can be integrated and controlled from the OpenCL framework

- Can enqueue built-in kernels to custom devices alongside OpenCL kernels

- OpenCL becomes a powerful coordinating framework for diverse resources

- Programmable and non-programmable devices controlled by one run-time

Built-in kernels enable control of specialized processors and hardware from OpenCL run-time

# K H R O N O S

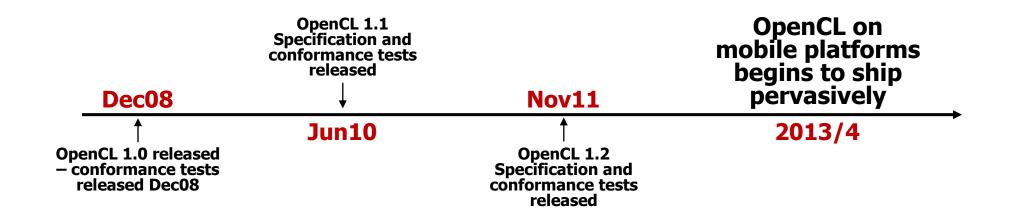

# **OpenCL Milestones**

# Six months from proposal to released OpenCL 1.0 specification

- Due to a strong initial proposal and a shared commercial incentive

- Multiple conformant implementations shipping on desktop

- For CPUs and GPUs on multiple OS

### 18 month cadence between releases

- Backwards compatibility protects software investment

S S

0° 2°

2

I

SIGGRAPH 2012

S

O°

Z°

2

I

# Adobe at SIGGRAPH 2012

Adobe V OpenCL

# Adobe

- Compute API supported across vendors

- Programming model familiar to C programmers

- Demonstrated performance

- Same compute kernels on CPU and GPU!

- Adobe is now active member of OpenCL working group

- Contributing Adobe's experience and minds to continue OpenCL evolution

SIGGRAPH - Khronos OpenCL BOF - August 8, 2012

Page 7

# **OpenCL Roadmap**

### **OpenCL-HLM** (High Level Model)

Exploring high-level programming model, unifying host and device execution environments through language syntax for increased usability and broader optimization opportunities

### Long-term Core Roadmap

Exploring enhanced memory and execution model flexibility to catalyze and expose emerging hardware capabilities

Considering ways to exploit unified and shared virtual memory systems where available

### **OpenCL-SPIR** (Standard Parallel Intermediate Representation)

Exploring LLVM-based, low-level Intermediate Representation for code obfuscation/security and to provide target back-end for alternative high-level languages

S O S S S S S S S S S S S

2

I

$\mathbf{\Sigma}$

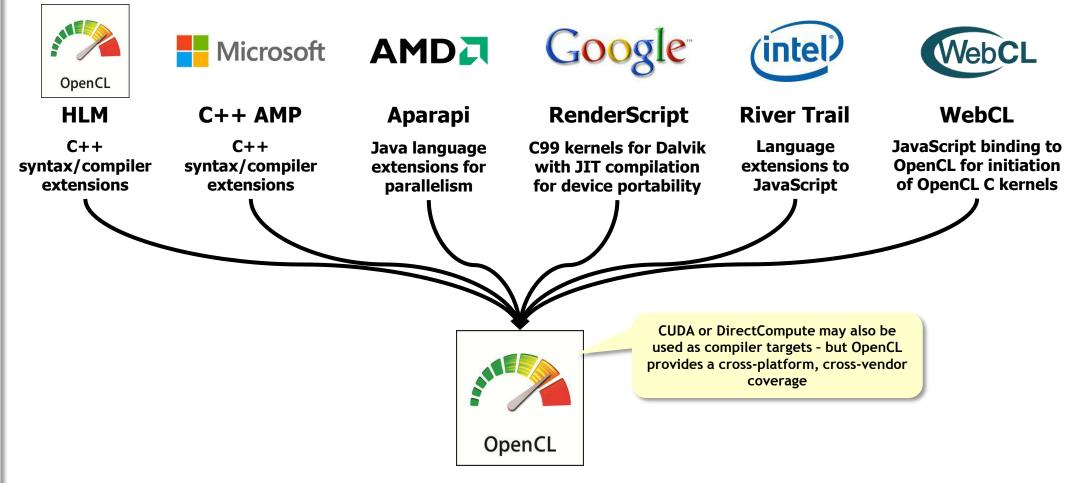

# **OpenCL as Parallel Compute Foundation**

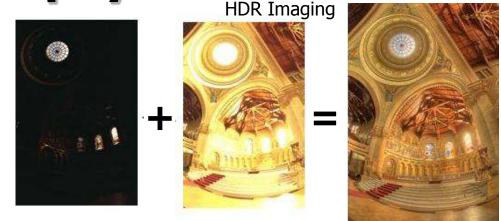

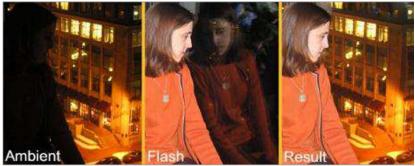

# **Computational Photography**

- Many advanced photo apps today run on a single CPU

- Suboptimal performance and power

- OpenCL is platform to harness CPUs/GPUs for advanced imaging

- Even if code is 'branchy'

"The tablet ... has new multimedia capabilities, including a computational camera, which lets devs tap directly into its computational capability through new application programming interfaces such as OpenCL. That access enables nextgeneration use cases such as light-field cameras for mobile devices."

###

Flash / no-flash imaging

S O S O S O S O S O S

HRC

$\mathbf{\Sigma}$

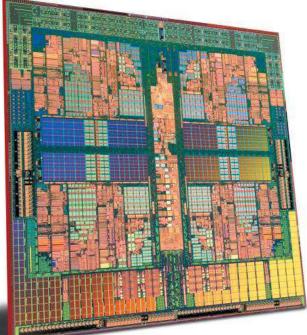

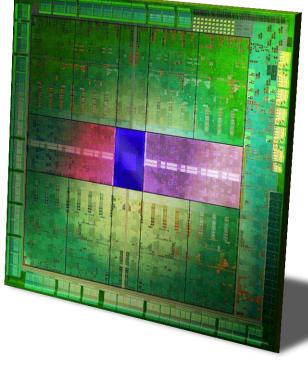

# **OpenGL 20th Birthday - Then and Now**

| OpenGL                                 | Ideas in Motion - SGI                                                      |                                                         | <section-header></section-header>                    |  |

|----------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|--|

| OpenGL<br>RUTH ANNIVERSARY   1992-2012 | 1992<br>Reality Engine<br>8 Geometry Engines<br>4 Raster Manager<br>boards | 2012 Mobile<br>NVIDIA Tegra 3<br>Nexus 7 Android Tablet | 2012 PC<br>NVIDIA<br>GeForce GTX 680<br>Kepler GK104 |  |

| Triangles / sec (millions)             | 1                                                                          | 103 (x103)                                              | 1800 (x1800)                                         |  |

| Pixel Fragments / sec (millions)       | 240                                                                        | 1040 (x4.3)                                             | 14,400 (x60)                                         |  |

| GigaFLOPS                              | 0.64                                                                       | 15.6 (x25)                                              | 3090 (x4830)                                         |  |

|                                        | <b>1.5KW</b>                                                               | <b>&lt;5W</b>                                           |                                                      |  |

C V V

I

$\mathbf{X}$

ິ

Z°

2

I

$\mathbf{\mathbf{\Sigma}}$

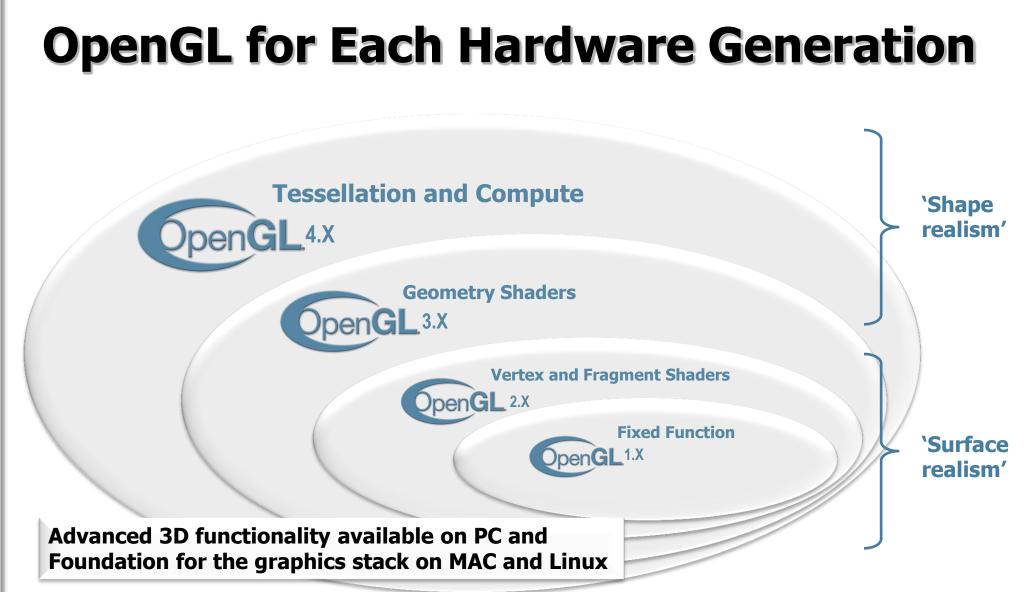

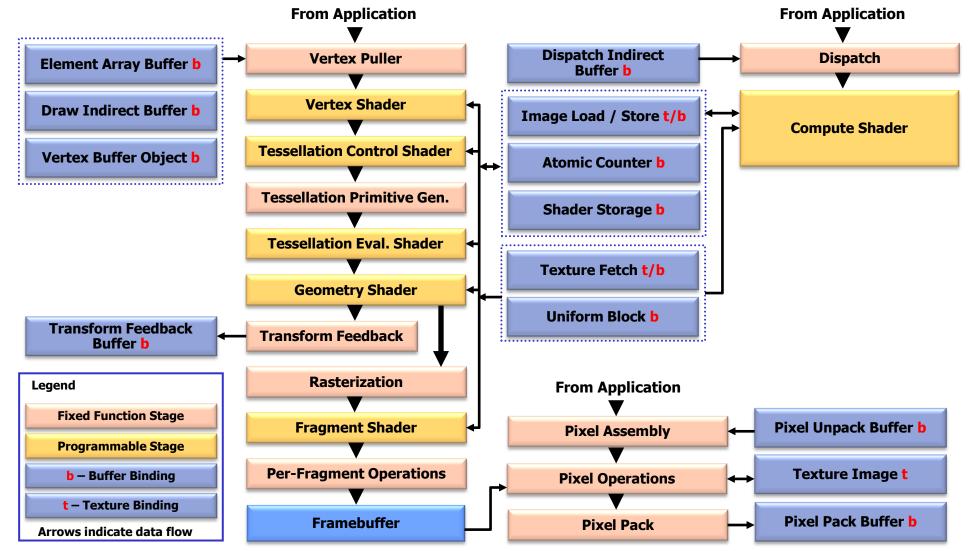

# **OpenGL 4.3 with Compute Shaders**

<sup>©</sup> Copyright Khronos Group 2012 | Page 37

N S S S S S S

H RC

$\mathbf{\mathbf{\Sigma}}$

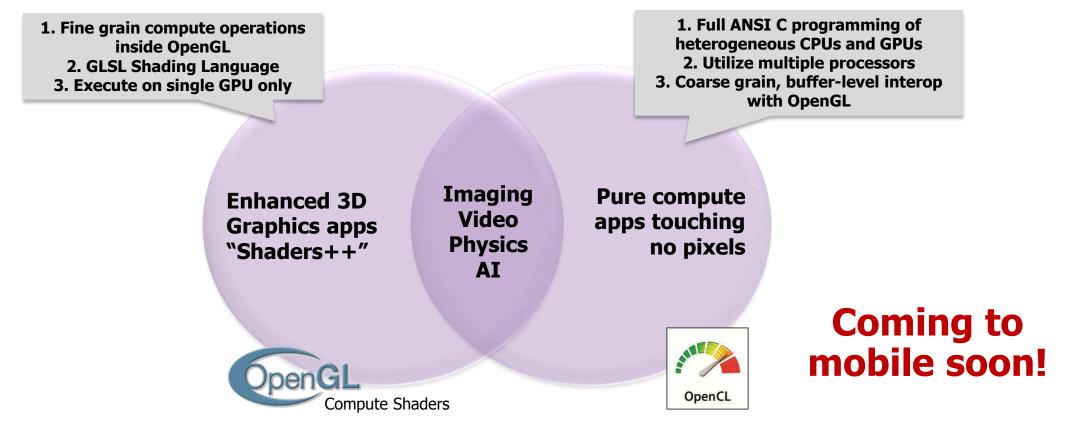

# **Compute Shaders**

### • Execute algorithmically general purpose GLSL shaders

- Operate on uniforms, images and textures

### Process graphics data in the context of the graphics pipeline

- Easier than interoperating with a compute API IF processing 'close to the pixel'

### Complementary to OpenCL

- Not a full heterogonous (CPU/GPU) programming framework using full ANSI C

### Standard part of all OpenGL 4.3 implementations

- Matches DirectX 11 functionality

Physics

AI Simulation

**Ray Tracing**

Imaging

**Global Illumination**

S O N S O N S

2

I

$\mathbf{\Sigma}$

# **OpenCL and OpenGL Compute Shaders**

### OpenGL compute shaders and OpenCL support distinctly different use cases

- OpenCL provides a significantly more powerful and complete compute solution

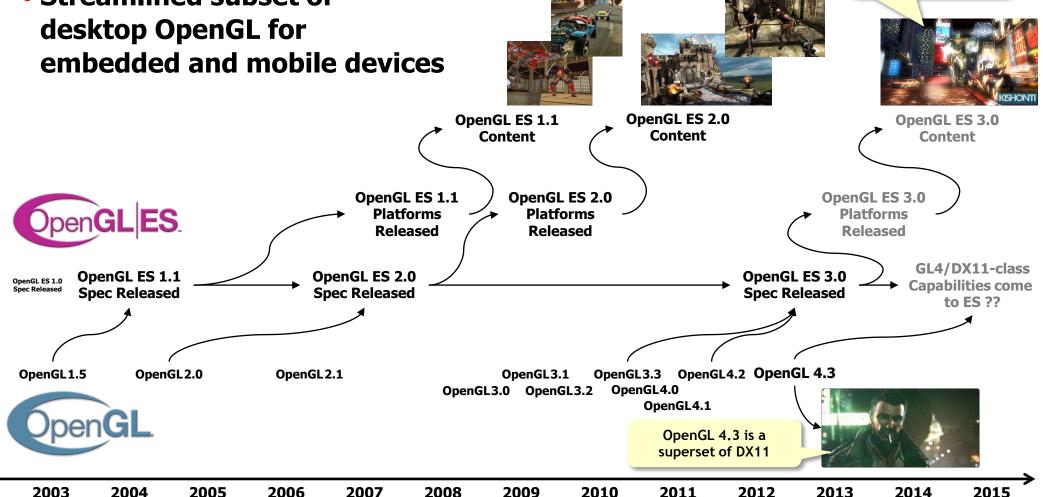

# **OpenGL ES**

Streamlined subset of desktop OpenGL for embedded and mobile devices

ES3 is backward compatible - so new features can be added incrementally

<sup>©</sup> Copyright Khronos Group 2012 | Page 40

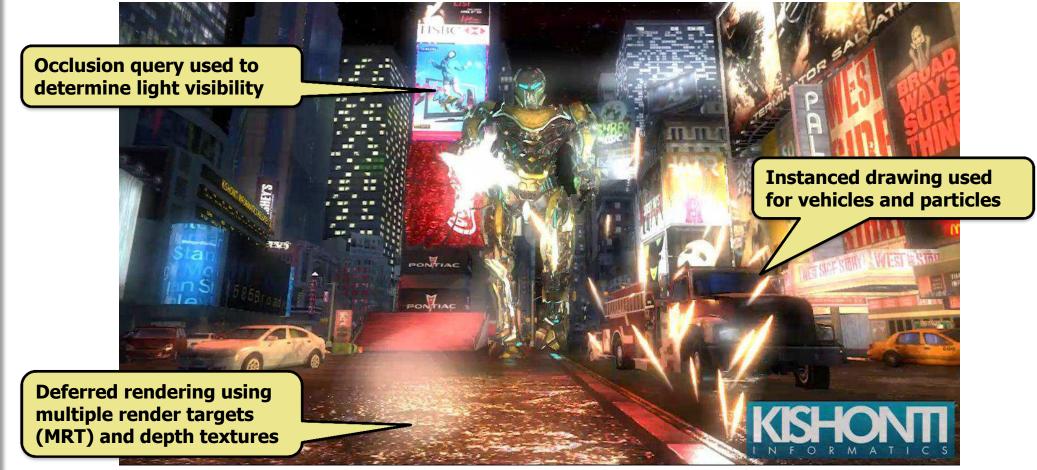

# **OpenGL ES 3.0 Highlights**

### Better looking, faster performing games and apps – at lower power

- Incorporates proven features from OpenGL 3.3 / 4.x

- 32-bit integers and floats in shader programs

- NPOT, 3D textures, depth textures, texture arrays

- Multiple Render Targets for deferred rendering, Occlusion Queries

- Instanced Rendering, Transform Feedback ...

### Make life better for the programmer

- Tighter requirements for supported features to reduce implementation variability

### Backward compatible with OpenGL ES 2.0

- OpenGL ES 2.0 apps continue to run unmodified

### Standardized Texture Compression

- #1 developer request!

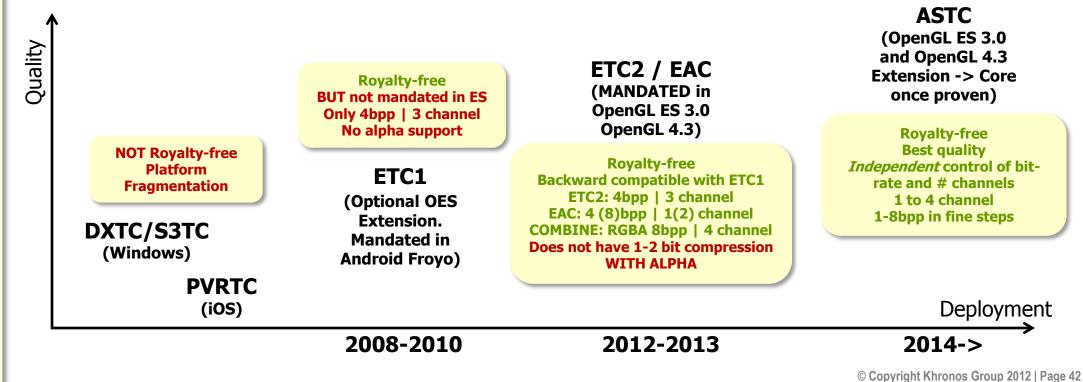

# **Texture Compression is Key**

### Texture compression saves precious resources

- Saves network bandwidth, device memory space AND memory bandwidth

- Developers need the same texture compression EVERYWHERE

- Otherwise portable apps such as WebGL need multiple copies of same texture

# ASTC – Future Universal Texture Standard?

### Adaptive Scalable Texture Compression (ASTC)

- Quality significantly exceeds S3TC or PVRTC at same bit rate

### Industry-leading orthogonal compression rate and format flexibility

- 1 to 4 color components: R / RG / RGB / RGBA

- Choice of bit rate: from 8bpp to <1bpp in fine steps

- ASTC is royalty-free and so is available to be universally adopted

Shipping as extension today for industry feedback

# **Kishonti GLBenchmark 3.0**

Kishonti "GLBenchmark 3.0" preliminary

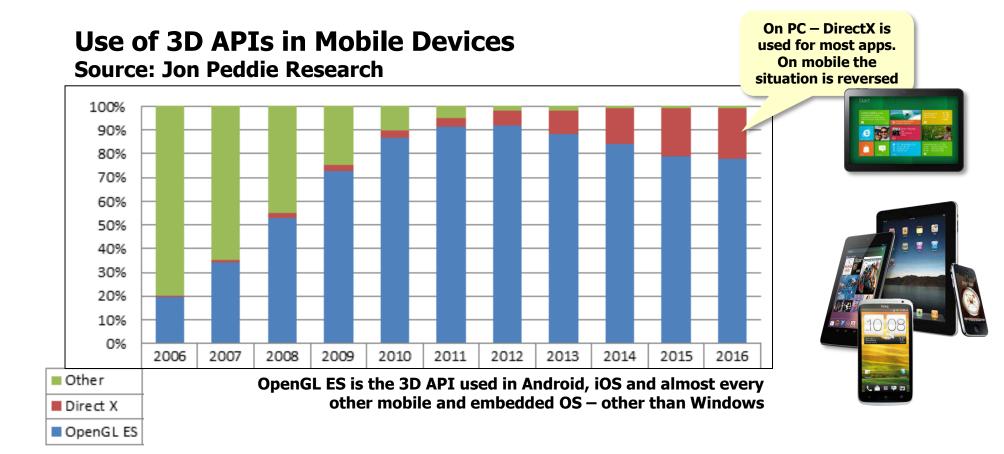

# **OpenGL ES Deployment in Mobile**

K H R N N O S

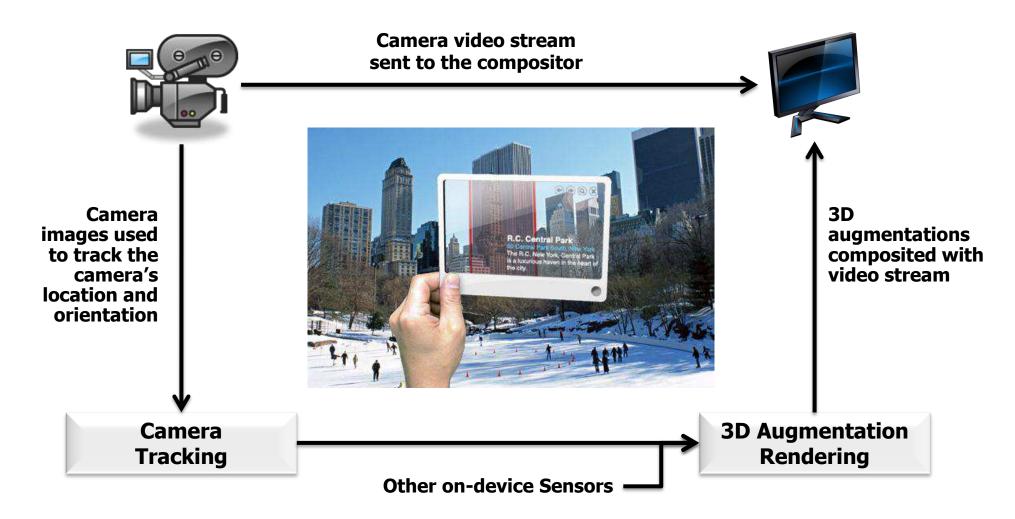

# **Visual-based Augmented Reality**

S O S O S O S O S O S

HR

$\mathbf{X}$

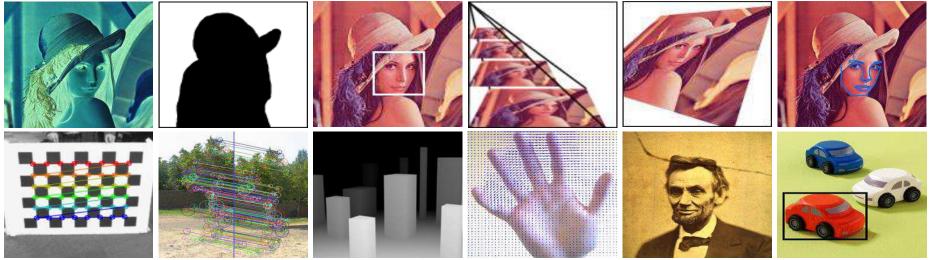

# OpenCV

### • Widely used Computer Vision open source project

- Not an API definition, not managed by Khronos

### Extensive functionality

- Used in academia, fast prototyping, some products

# Traditionally runs on a single CPU

- MulticoreWare open source CPU/GPU enabled OpenCV over OpenCL

**OpenCV**

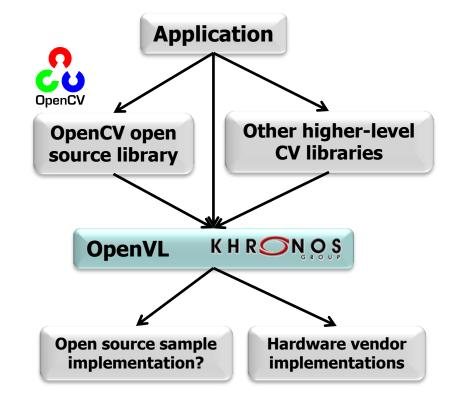

# **OpenVL**

### Vision Hardware Acceleration Layer

- Enable hardware vendors to implement accelerated imaging and vision algorithms

### Diversity of efficient implementations

- From dedicated hardware pipelines to parallel programmable processors

### Can be used by high-level libraries or applications directly

- Primary focus on enabling real-time vision apps on mobile and embedded systems

### OpenCV will leverage OpenVL for acceleration

- OpenVL does not duplicate OpenCV functionality

- JUST provides essential acceleration

S O N S O N

2

I

$\mathbf{\Sigma}$

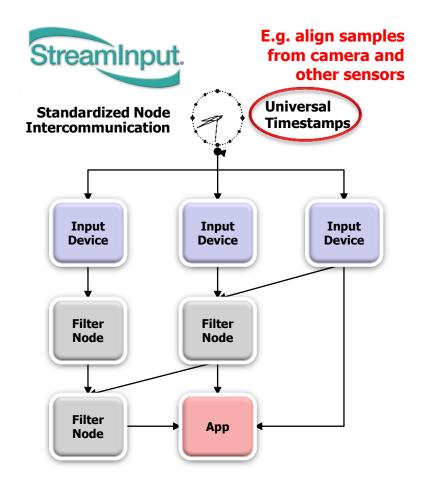

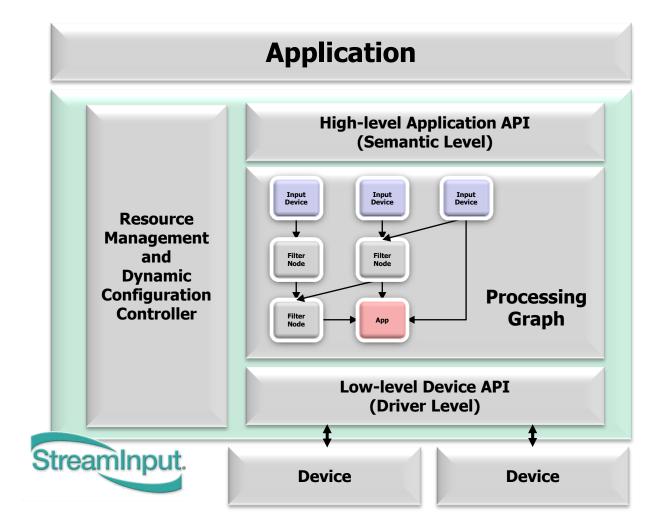

### **Possible Implementation of Vision Stack** Semantics and fusion of StreamInput. Implement camera and positional sensors StreamInput vision sensor modules with OpenCV **High-level** computer vision library Accelerate OpenCV OpenCV OpenMAX AL. library with **OpenVL Functions Camera input from** Data and event Accelerated computer OpenMAX AL or **OpenVL** interop with CL / other camera OpenGL ES GL / ES for display vision algorithms subsystems and compute processing **Use OpenCL** EGL EG to implement **OpenVL** with parallel OpenCL execution **Parallel computation** OpenCL

S O N S O N

2

Т

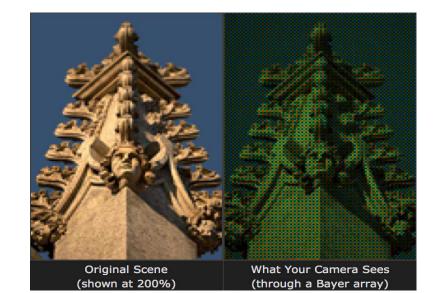

# **Requested Camera Extensions**

# Query camera information

- Focal length (fx, fy), principal point (cx, cy), skew (s), image resolution (h, w)

- Spatial information of how cameras and sensors are placed on device

- Calibration and lens distortion

# ROI extraction

- From wide angle and fish-eye lenses

# • FCAM++ - Extensive exposure parameters in single or burst mode

- Shutter, aperture, ISO, white balance, frame rate, focus modes, resolution

- Synchronization with other system sensors

# Data output format control

- Grayscale, RGB(A), YUV

- Access to the raw data e.g. Bayer pattern

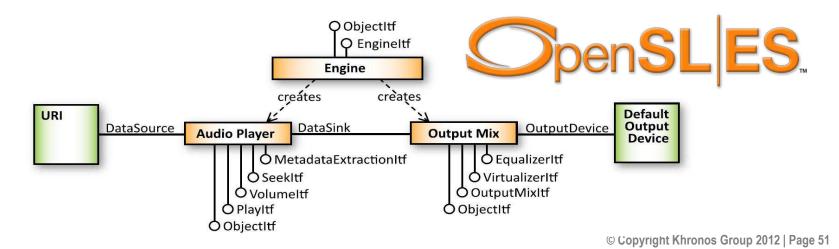

# **OpenSL ES – Advanced Audio**

### OpenSL ES does for audio what OpenGL ES does for graphics

- Advanced audio functionality from simple playback to full 3D positional audio

# Object-based native audio API for simplicity and high performance

- Same object framework as OpenMAX AL

- Reduces development time

### Attractive alternative to open source frameworks

- Tightly defined specification with full conformance tests

- Robust application portability across platforms and OS

K H R O N O S

2

I

$\mathbf{\Sigma}$

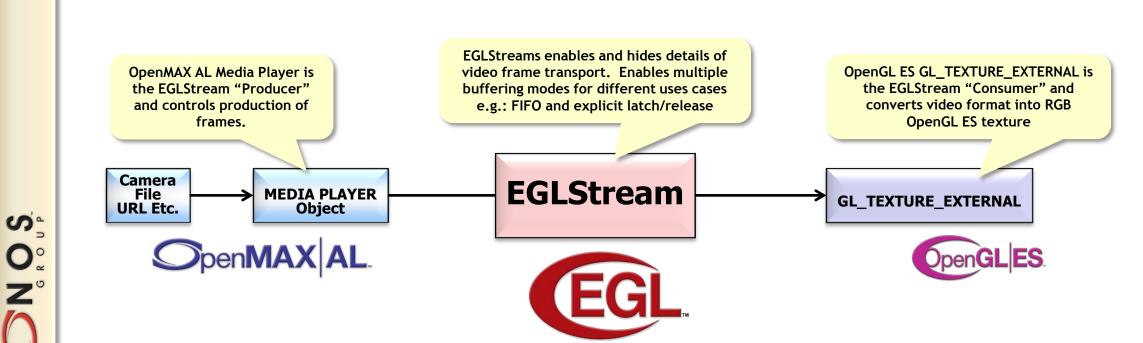

# EGLStream – Video/Graphics Interop

# **Portable Access to Sensor Fusion**

Advanced Sensors Everywhere RGB and depth cameras, multi-axis motion/position, touch and gestures, microphones, wireless controllers, haptics

keyboards, mice, track pads

Apps request semantic sensor information

StreamInput defines possible requests, e.g. "Provide Skeleton Position" "Am I in an elevator?"

### Processing graph provides sensor data stream

Utilizes optimized, smart, sensor middleware Apps can gain 'magical' situational awareness

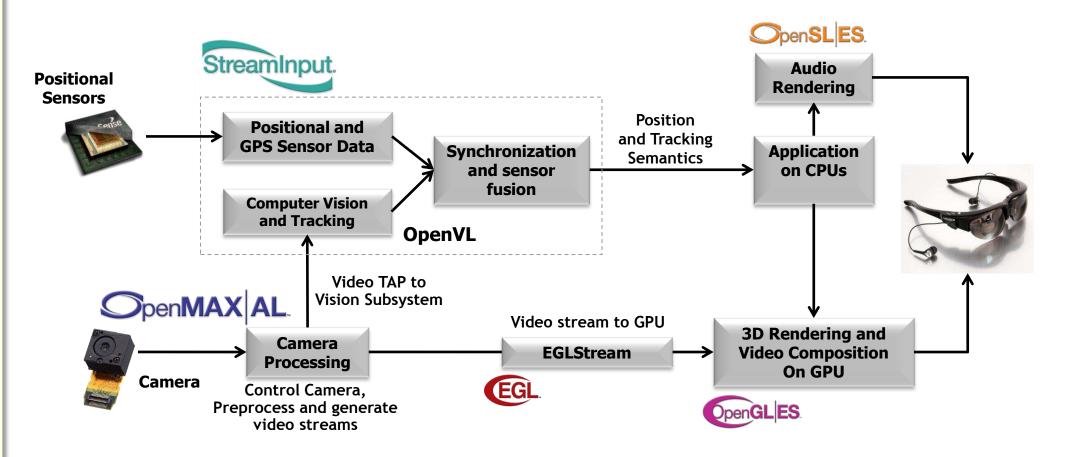

# **Example use of Khronos APIs in AR**

# **API Adoption**

|  | OpenGL ES. | OpenGL ES 2.0<br>Shipping - Android 2.2                   |  |

|--|------------|-----------------------------------------------------------|--|

|  |            | OpenSL ES 1.0<br>Shipping – Android 2.3                   |  |

|  |            | OpenMAX AL 1.0<br>Shipping - Android 4.0                  |  |

|  | EGL        | EGL 1.4<br>Shipping under SDK -> NDK                      |  |

|  | WebGL      | Chrome will have WebGL.<br>Opera and Firefox WebGL now    |  |

|  | OpenGL     | OpenGL 3.2<br>on MacOS                                    |  |

|  | OpenCL     | OpenCL 1.1<br>on MacOS                                    |  |

|  | OpenGL ES. | OpenGL ES 2.0<br>on iOS                                   |  |

|  | WebGL      | Can enable on MacOS Safari<br>iOS5 enables WebGL for iAds |  |

|  |            |                                                           |  |

### **Mobile Operating Systems**

**Microsoft Windows RT:**

- Only Microsoft native APIs

- HTML5 but not yet WebGL

S O S S S S S S S S S S S

2

Т

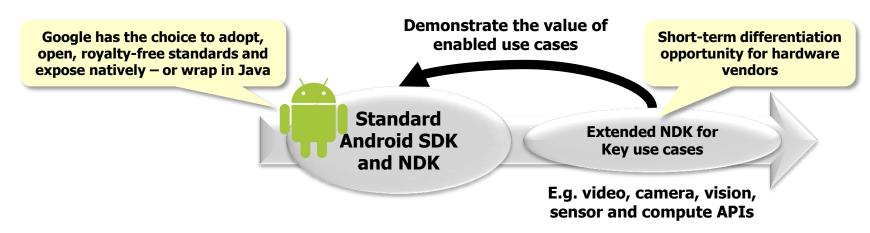

# **Extended Native APIs on Android**

### • Native APIs can be shipped as NDK extensions before Google Adoption

- Do not break/change existing Google APIs

### Khronos open standard APIs have strong momentum in silicon

- Google has choice to adopt into standard platform to eliminate fragmentation

- Exposed directly or wrapped in Java binding

### Extended APIs can be used by:

- Bundled apps, Market apps with API selection

- Multiple APKs behind single multi-APK SKU

# HTML5 – Cross OS App Platform

- Increasing diversity of devices creates a demand for a true cross OS programming platform

- BUT need more than "more HTML"

# Image: set in the set in

How can the Browser rapidly assimilate such diverse functionality?

Traditional Web-content

S O N S O S S S S S S S S S

2

I

$\mathbf{\mathbf{\Sigma}}$

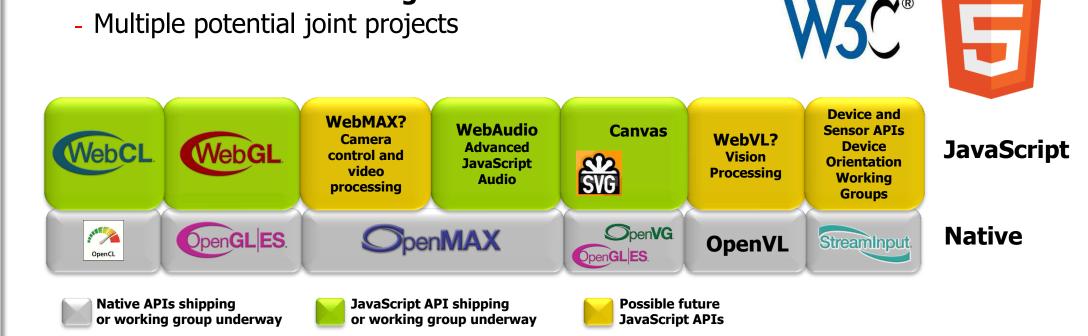

# Leveraging Proven Native APIs into HTML5

### Leverage native API investments into the Web

- Faster API development and deployment

- Familiar foundation reduces developer learning curve

### Khronos and W3C creating close liaison

- Multiple potential joint projects

HTML

W3C<sup>®</sup>

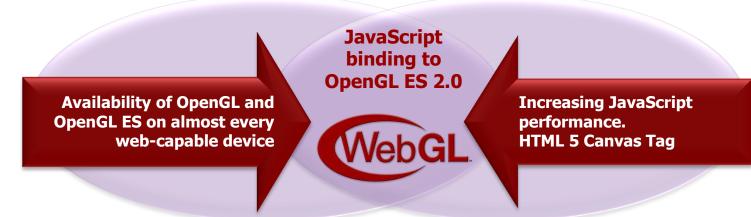

# WebGL – 3D on the Web – No Plug-in!

- Historic opportunity to bring accelerated 3D graphics to web

- WebGL defines JavaScript binding to OpenGL ES 2.0

- Leveraging HTML 5 and uses <canvas> element

- Enables a 3D context for the canvas

- Low-level foundational API for accessing the GPU in HTML5

- Flexibility and direct GPU access support higher-level frameworks and middleware

- WebGL 1.0 Released at GDC March 2011

- Mozilla, Apple, Google and Opera working closely with GPU vendors

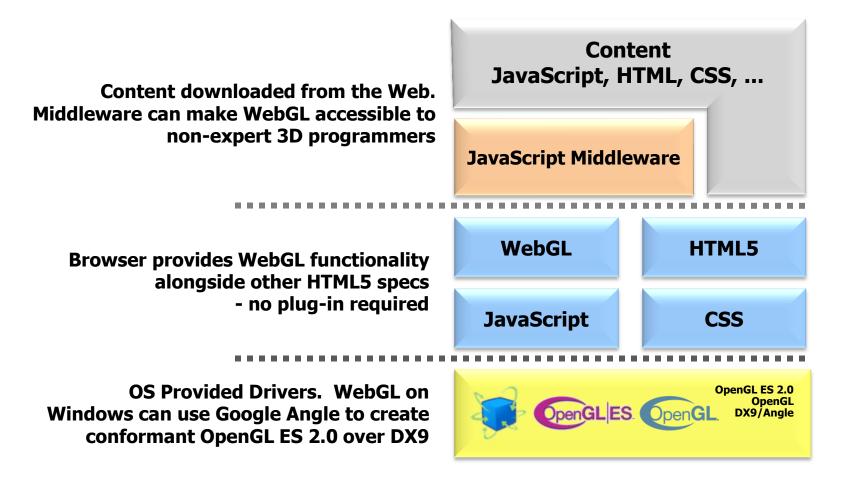

# **WebGL Implementation Anatomy**

# WebGL – Being Used by Millions Every Day

S

S O N N

2

I

$\checkmark$

# **WebGL and Security**

### WebGL is Architecturally Secure

- NO known WebGL security issues

- Impossible to access out-of-bounds or uninitialized memory

- Use of cross-origin images are blocked without permission through CORS

- Browsers maintaining black lists used if unavoidable GPU driver bugs discovered

# DoS attacks and GPU hardening

- Draw commands can run for a long time -> unresponsive system

- Even without loops in shaders

- WebGL working closely with GPU vendors to categorically fix this

- Short term: mandate ARB\_robustness and associated GPU watchdog timer

- Longer term: GPUs need robust context switch and pre-emption

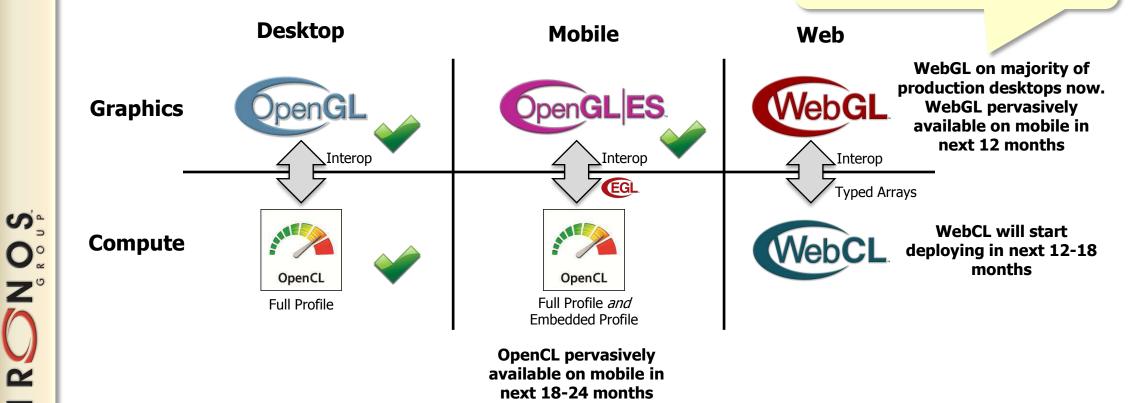

# WebCL – Parallel Computing for the Web

### JavaScript bindings to OpenCL APIs

- JavaScript initiates OpenCL C Kernels on heterogeneous multicore CPU/GPU

- Stays close to the OpenCL standard

- Maximum flexibility to provide a foundation for higher-level middleware

- Minimal language modifications for 100% security and app portability

- E.g. Mapping of CL memory objects into host memory space is not supported

- Compelling use cases

- Physics engines for WebGL games, image and video editing in browser

- API definition underway public draft just released

- https://cvs.khronos.org/svn/repos/registry/trunk/public/webcl/spec/latest/index.html

# WebCL Demo

http://www.youtube.com/user/SamsungSISA#p/a/u/1/9Ttux1A-Nuc

# WebCL for Hardware-Accelerated Web Applications

Advanced Browser Technology Samsung R&D Center San Jose, CA

S,

2

I

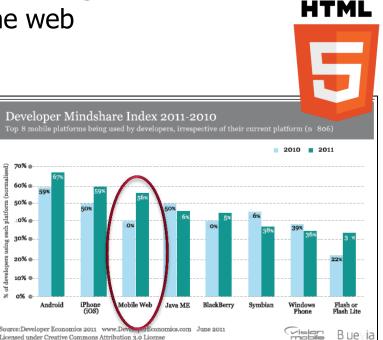

# Web Apps versus Native Apps

### Mobile Apps have functional and aesthetic appeal

- Beautiful, responsive, focused

# HTML5 with GPU acceleration can provide the same level of "App Appeal"

- Highly interactive, rich visual design

# Using HTML5 to create 'Web Apps' has many advantages

- Web app is searchable and discoverable through the web

- Portable to any browser enabled system

- Same code can run as app or as web page

- Not a closed app store no app store 'tax'

### How soon will we be able to write apps such as AR in HTML5?

60%

50%

0%

20% (

2

I

$\mathbf{Y}$

# **Expanding Platform Reach for Graphics and Computation**

Production Browsers Shipping with WebGL: Desktop - Chrome, Firefox, Opera, Safari Mobile - Opera and Firefox Apple iOS Safari uses WebGL for iAds

# Cross-OS Portability

VebGL

**Objective C**

GL ES

**NebGL**

Dalvik

(Java)

GL ES

HTML5 provides cross platform portability. GPU accessibility through WebGL available soon on ~90% mobile systems

C# Preferred development environments not designed for portability

**No WebGL**

**DirectX**

Native code is portablebut apps must cope with different available APIs and libraries

© Copyright Khronos Group 2012 | Page 67

K H R S S S

5

**SDK**

C/C++

# Summary

- Advances in SOC silicon processing are enabling significant new use cases

- Architectural shifts, such as unified memory, are creating challenges and opportunities for applications and the APIs that enable them

- Holistic cooperation between hardware and software needed to deliver increasing computational loads in a fixed power budget

- Dynamic tension between platform vendors that want captive apps and developers that benefit from cross platform portability

- Mobile operating systems lag in exposing the latest SOC capabilities which creates functional differentiation opportunities

- Cooperative API standards eliminate roadblocks to mobile industry growth

# **Thank You!**

# See you back at 11:10AM

# ArcSoft Multi-Frame Technologies Hot Chips 2012 Sean Mao, VP Marketing Advanced Imaging Technologies

ArcSoft

S O S S O S S S S

HR

$\mathbf{X}$

# **ArcSoft Overview**

- Founded in 1994

- HQ in Fremont, CA

- 900+ employees worldwide

- Photo & Video software

- Markets served:

- Mobile, tablet, PC, DSC

ິ

O°

Z°

2

I

$\mathbf{\Sigma}$

## **Industry Leaders Choose ArcSoft**

Nikon Canon Panasonic. OLYMPUS Di FUJIFILM

PENTAX EPSON Kodak FUITSU TOSHIBA

S O S O S O S O S O S

HR

## **ArcSoft Imaging Technologies**

- Adopted by major camera phone vendors and digital camera vendors

- Leverages various forms of hardware capabilities

- CPU, GPU, DSP, ISP, H/W Codec, Fast RAM, DMA, and other specialized hardware

- Highly efficient ISP

#### Boosts value to the end product

- Better capture quality and speed performance

- Better user experience

- Differentiation

S O S O S O S O S O

HR

$\mathbf{Y}$

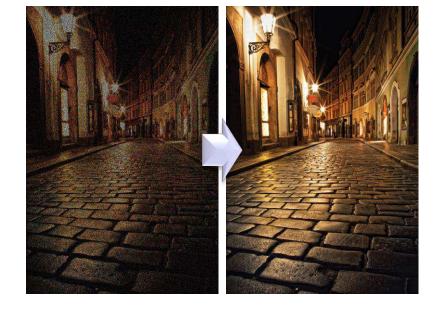

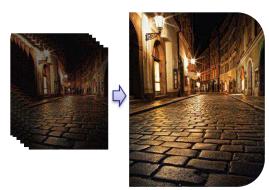

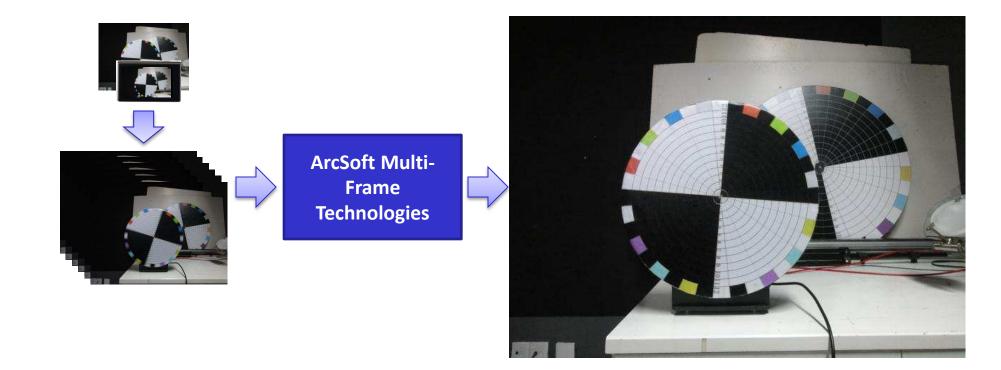

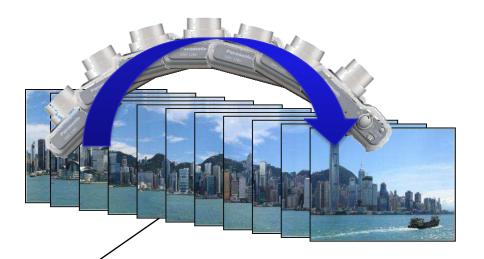

## ArcSoft Multi-Frame Technology Overview

- Takes advantage of high speed burst capability in latest capture SOC

- Combines multiple image frames to achieve improved image quality and better experience

S O S O S O S O S O S

2

I

## **ArcSoft Multi-Frame Technology Portfolio**

- Multi-Frame Night Shot

- Panorama BurstCapture

- Multi-Frame Anti-Shaking

- High Speed HDR

- PiClear (auto object removal)

- PicBest (optimal portrait composition)

- More...

## **Achieve Better Quality With Multi-Frame**

- Brighter

- Clearer

- Better resolution

**COMPARING WITH SONY DSC**

**TX-10**

ທ<sub>ີ</sub>

0° 2°

2

Т

## **Hardware Requirements**

- Fast burst capture capability (>15 FPS)

- Continuous burst to more than 300 shots and stop at any time

#### For each capture in the burst

- H/W noise filter enabled

- Output in YUV formats

- Capability to do bracketing

- e.g. void setEvBracketCapture(float[]); // In NvCamera

- Capability to change the capture parameters (3A, ISO, Gain, etc)

- e.g. void void setExposureTime(int); // In NvCamera

- Capability to lock the capture parameters

#### e.g.

void setAutoExposureLock(boolean lock); // In NvCamera

void setAutoWhiteBalanceLock(boolean lock); // In NvCamera

S O N N

2

I

## **Challenges and Expectations**

- Quality of the each frame in the burst is not well-tuned sometime, especially when captured with non-3A parameters

- Image frames sometime are not consistent even with all capture parameters locked

- Need downsized image frames passed from ISP

- Need Bayer RAW output

- Need hardware-based math functions especially for matrix operations

- e.g. add, subtract, multiply, absolute difference, division, max, min, linear gradual blend, etc..

#### **Touch-free technology** Itay Katz Founder and CTO

#### **Overview**

eyeSight's groundbreaking Touch Free technology provides an enhanced user experience, allowing to easily and intuitively control a variety of devices using simple hand gestures.

eyeSight's Natural User Interface solution utilizes the device's standard 2D camera, along with advanced real-time image processing and machine vision algorithms, to track the user's hand gestures and convert them into actions.

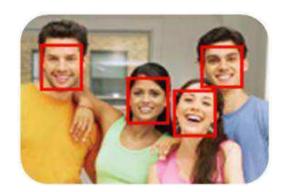

## Components of eyeSight's Gesture recognition technology:

- Directional gestures detection

- Real-time hand / fingertip tracking

- Face detection and tracking (multiple users)

- Hand signs; "OK", "Like" etc.

# Implementation Challenges of such technologies:

- Very high processing requirements

- Memory Throughput

- Real-time performance

N O S N O S

HR

### **Solutions: Managing performance**

- Algorithm- the key tool for minimizing performance

- Target specific optimizations

- Instrinsics using special instructions

- ISA Extensions: x86 SSE, ARM NEON

- Assembly

- GPGPU OpenCL

#### Solutions: Coping with memory throughput

- Image processing algorithms require reading/writing the video many times, placing a lot of load on the memory subsystem.

Reading a 720p YUV422 streams just once requires 55 Mbytes/Sec.

- DMA not usable in most systems, since there are no tightly-coupled memories.

- It is key to minimize the number of passes on the video data.

- **Designing for Cache**

- Minimize data footprint

- Locality

- Automatic pre-fetching

- Software pre-fetching

#### Solution: Handling real-time performance

- Most systems are non-deterministic: Caches, other processes, O/S behavior

- Algorithms require more processing when there's "action" in the video

- This makes the instantaneous performance requirements vary greatly

- As a result, it is not possible to guarantee hard real-time performance

- Instead, our solution is design to be soft real-time, and to handle realtime violations

- One challenge is the lack of standardized high-precision timers to allow software to monitor execution time

### **Platform portability - Challenges:**

#### Challenges:

- Maintaining a single code base across multiple products, OS types and compilers

- Stay up to date with recent OS version releases

- Maintain backward compatibility

- Maintaining pixel portability

#### **Platform portability - Solution:**

#### <u>Solution</u>:

- Working with automated tools for each core code change

- Maintain strict coding conventions to avoid using platform specific libraries

- Use cross platforms frameworks such as OpenCL

- Work with a configurable device abstraction layer to keep platform specific code from migrating into different platforms or devices

- Using a framework developed in eyeSight we can convert any video stream, any resolution or format (including IR), to a single representation that serves our algorithms

💥 eyeSigh

#### Thank you.

# www.eyeSight-tech.com

#### AUGMENTED SOLUTIONS

#### **Augmented Reality** Hot Chips 2012 **Ben Blachnitzky Director R&D, Metaio**

#### metaio

- Founded 2003 out of computer vision research

- Privately held, independently financed

- 500+ B2B customers worldwide

- 85+ people working in Munich (HQ) and San Francisco

- 10,000+ active developers worldwide

- Extensive R&D department with 100+ patents across 38 different families

- 200+ mobile apps running on metaio technology

K H RO

N S S

2

I

$\mathbf{X}$

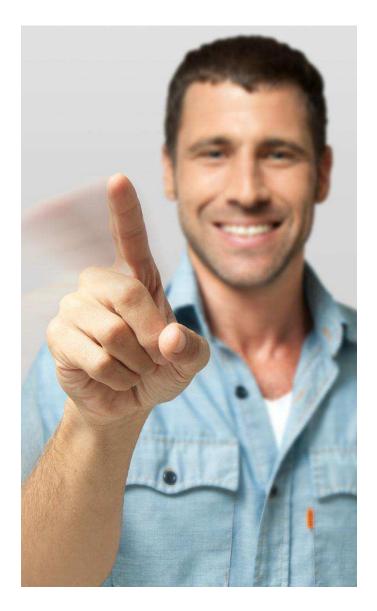

### From Hardware to Software to End User

## **General Milestones**

- Oct. 2011: Won ISMAR tracking competition with pure mobile marker-less tracking

- Dec. 2011: mobile SDK 3.0 release

- Advanced visual tracking of 2D and 3D objects

- Gravity aware AR

- Optimized AR-pipeline for major mobile chipsets (ARM, ST-Ericsson, Texas Instruments)

- February/March 2012: <u>Augmented City</u> Platform at MWC and SDK 3.1

- Advanced 3D object tracking

- Visual search technology

- Further hardware optimization on AR-pipeline

#### • Estimated Q4 2012: mobile SDK 4.0

## **Achievements and Challenges**

- From marker-tracking to full 3D Object Tracking on mobile in only 14 months

- Low level optimizations:

- Leveraging SIMD extensions (e.g. NEON) for certain computer vision tasks

- Memory constraints and optimizations especially for large client based visual search

- General pipeline optimizations and leveraging modern multi-core architectures

- Optimized camera access for e.g. high-resolution visualization images and lower resolution tracking images

- **Challenges:** Battery consumption & extending the limits of tracking in AR so that it becomes natural for consumers

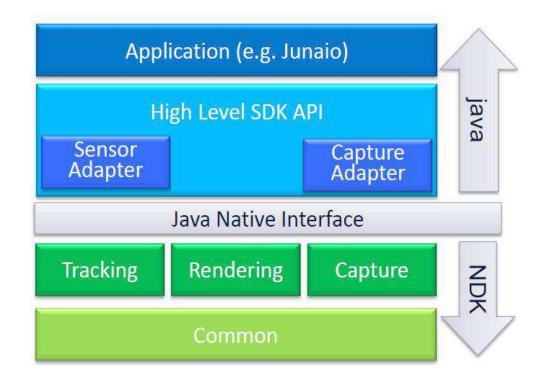

## **High-level Overview of Mobile SDK**

#### Android Developer Perspective

- Java IF for straightforward application development

- Computational-intensive operations in NDK

- JNI provides language interoperability

## **Multiple Object AR**

- More than 40 instances of client-based real-time image detection made possible through specific optimized algorithms

- Activation and recognition speed comparable to Quick Response (QR)

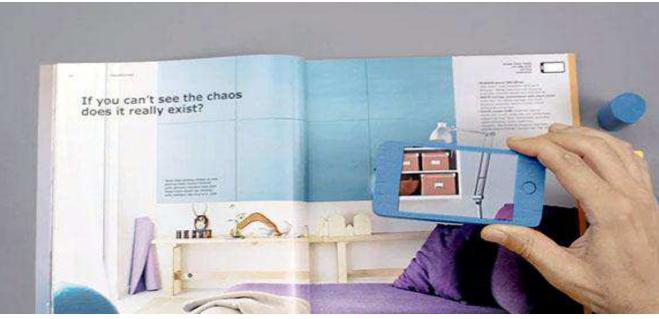

<u>http://www.youtube.com/watch?v=QQ8HNXtl7jQ&feature=player\_embedded</u> <u>http://creativity-online.com/news/mccannerickson-gives-new-ikea-catalog-a-vitamin-pill/236165</u>

## **Useful AR Optimizations**

#### http://www.youtube.com/watch?v=DMg4UUCaQdw

- 100+ images detected and recognized

- Same algorithms and technology are freely available to mobile developer ecosystem

# K H R N N O S

S

2

Т

$\mathbf{\mathbf{\Sigma}}$

## **AR Enhanced Print Media (Mobile AR)**

PERFORMANCE SA Packers go over th Powering "AR-Lite" cloud-based experiences that should

http://www.youtube.com/weltderwunderadsales#p/f/3/KZS1Q3I0a9Q

Süddeutsche 7eitun

- be accessible in nearly all connectivity environments

- Current adopters: The Atlantic, Axel Springer, Burda, Süddeutscher Verlag, USA Today

- +10 million copies of AR enhanced magazines are powered by junaio cloud infrastructure

## **API | Hardware Wish List**

- One Computer Vision hardware abstraction layer for Android and iOS

- Native/Advanced camera access across different platforms:

- Visualization image and tracking image

- Hardware optimized image pre-computations/conversions

- Full control of camera parameters such as shutter, brightness, (auto-) focus

- Very fast texture upload to renderer for camera image

- Platform independent parallelization approaches (SIMD and multi-core)

- HW implementation for most important AR functions to address the battery consumption issue

#### www.metaio.com

@twitt\_AR

#### facebook.com/metaio

#### augmentedblog.wordpress.com

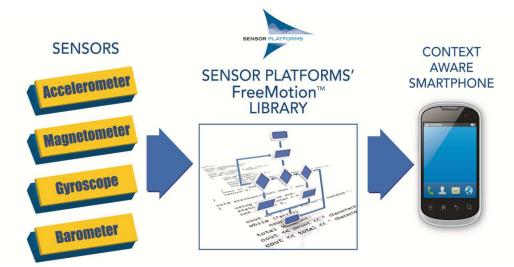

SENSOR PLATFORMS

#### Sensor Fusion Mobile Platform Challenges and Future Directions Jim Steele VP of Engineering, Sensor Platforms, Inc.

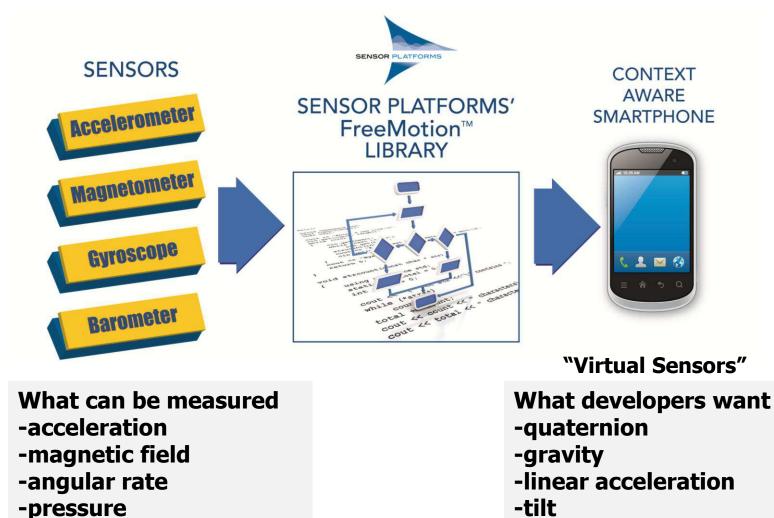

## **How Many Sensors are in a Smartphone?**

- Light

- Proximity

- 2 cameras

- 3 microphones (ultrasound)

- Touch

- Position

- GPS

- WiFi (fingerprint)

- Cellular (tri-lateration)

- NFC, Bluetooth (beacons)

- Accelerometer

- Magnetometer

- Gyroscope

- Pressure

- Temperature

- Humidity

## **Mobile Sensor Challenges**

~90° compass error in the first Ice Cream Sandwich smartphone

- Underlying problems:

- Some sensor components lack repeatability

- RF and other PCB noise interaction with mag sensor

- Non-standard availability (no gyro, pressure, 2nd camera, ...)

- Non-standard capability (resolution, update rate, ...)

- Not fully specified (non-uniform gain, skew)

## **User Experience Across Platforms**

- Heavy engineering burden to maintain consistency across system variations

- Hard and soft iron contents

- Component selection for optimal price/performance

- Different application processors (sensor hubs)

- Different mobile OS

#### Validation efforts diffused over multiple platforms

#### **Sensor Fusion Algorithms Solve Challenges**

K H R O N O S

## **Examples of Sensor Fusion**

#### 10-axis sensor fusion and background calibration

- Industry standard foundation for sensors

- No user-intervention to keep sensors calibrated

- Adjusts to changes in environment

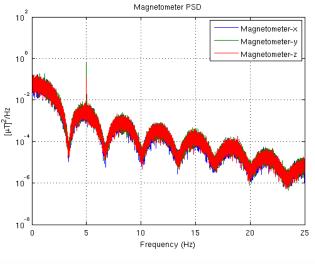

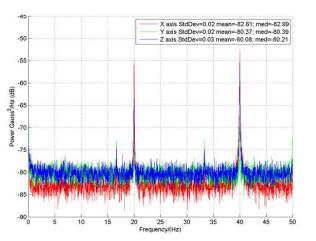

#### Sensor data can be interpreted using algorithms

- Magnetometer  $\rightarrow$  Compass (avoid magnetic anomalies)

- Pressure  $\rightarrow$  Altitude (avoid pressure anomalies)

- Throttle the gyroscope (keep highest power sensor off until needed)

#### Combine multiple sensors to improve sensing

- Pressure + GPS = faster GPS fix

- Camera + Sensor Fusion = Augmented Reality

- inElevator sensor?

## **Comparison of Mobile OS Sensor Support**

| Sensor                      | iOS 5            | Android             | Win8         |  |

|-----------------------------|------------------|---------------------|--------------|--|

| Accel/Mag/Gyro              | $\checkmark$     | $\checkmark$        | $\checkmark$ |  |

| Pressure/Humidity           | x                | $\checkmark$        | x            |  |

| Quaternion                  | CMAttitude       | ROTATION_VECTOR     | Orientation  |  |

| <b>Euler Angles</b>         | CMAttitude       | ORIENTATION (depr.) | Inclinometer |  |

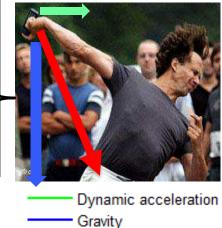

| Dynamic<br>Acceleration     | userAcceleration | LINEAR_ACCELERATION | Shake        |  |

| Gravity in body<br>frame    | gravity          | GRAVITY             | Tilt         |  |

| Tilt-compensated<br>Compass | X                | X                   | Compass      |  |

| In Elevator                 | x                | x                   | x            |  |

Virtual Sensors, e.g.

Measured acceleration

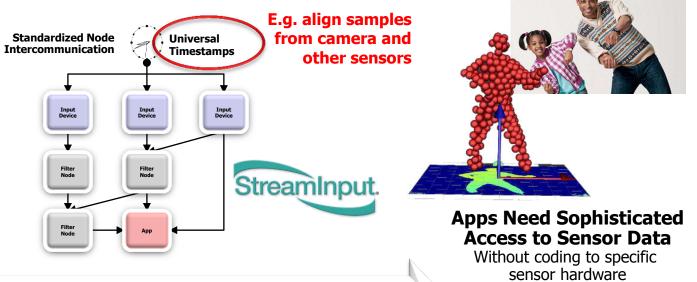

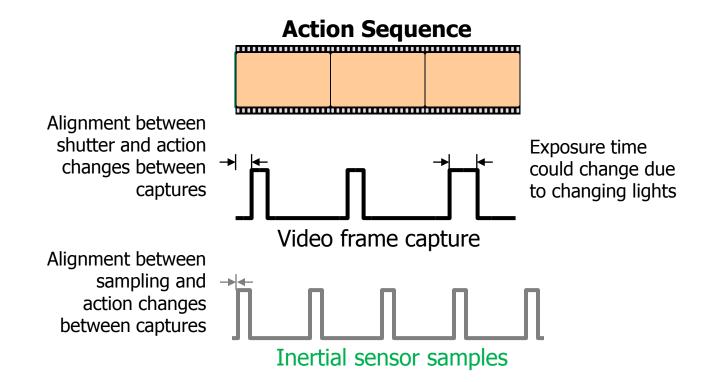

## **Need Unified Timestamp between Sensors**

- Sensors work on different time bases that drift

- Not all sensors support the same sampling rate

K H R O N O S

S O S O S O S O S

2

I

## **StreamInput Concepts**

#### Standardized Application-defined filtering and conversion

- Can create virtual input devices

#### • Sensor Hardware Vendor Agility for OEMs

- Allows standardized interface for hardware accelerated features

#### Extensibility to any sensor type

- Can define new node data types, state and methods

#### Sensor Synchronization

- Universal time stamp on every sample

## StreamInput Architecture

- 1. Setup Processing Graph (or use pre-supplied graph), request and receive semantic sensor stream through Highlevel API

- 2. Optionally, dynamically configure sensor processing through Lowlevel API – can tune power vs. performance

Implementable over existing OS input APIs to simplify adoption

S O N S O N

2

Т

## **Sensor Platforms**

• We create algorithms for sensors

- More information at our blog: <u>www.sensorplatforms.com</u>

- jsteele@sensorplatforms.com

## **Platform Performance** Dan Wexler, CxO The 11<sup>ers</sup>

N O S

K H R

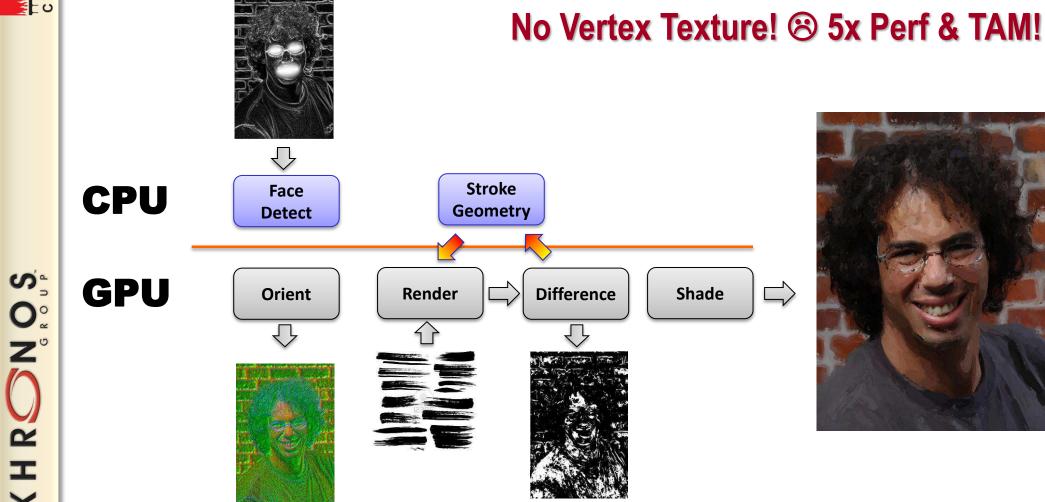

## CPU

# AGP PCIe

GPU

N O S S O S

HR

$\mathbf{X}$

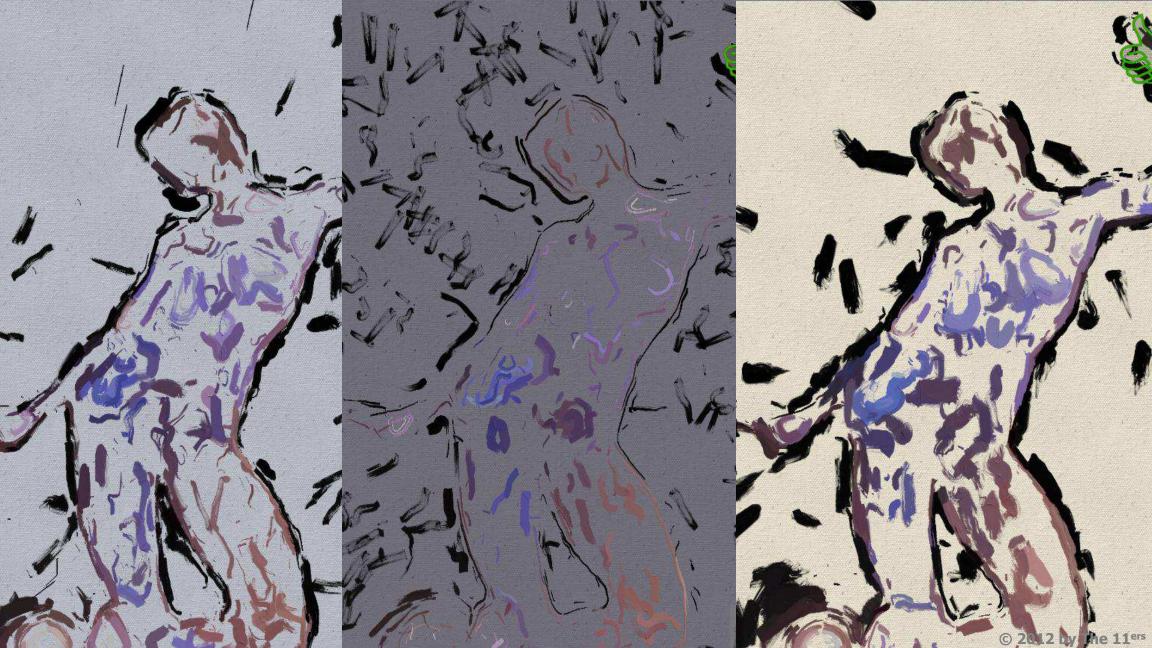

#### "Leading edge graphics in tasty mobile bytes."

#### Small Scope → Low Risk → Experience

S O N S O S S S S S S S S S

HR

$\mathbf{X}$

# \$5B & 650K

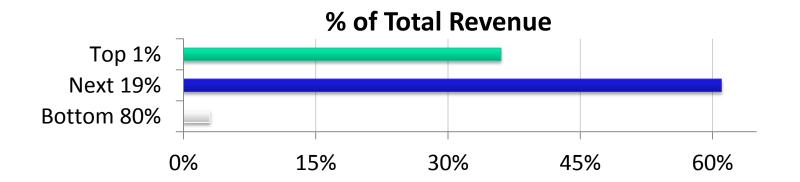

## Top 1% get 36% (\$270K) Next 19% get 61% (\$25K) Last 80% get 3% (\$290)

51 titles *before* Angry Birds

\* http://DaveAddey.com/?p=893, 7/26/12

HR

$\mathbf{X}$

## **Dynamic, Dependent, Reusable**

N S O S O S O

2

I

$\mathbf{X}$

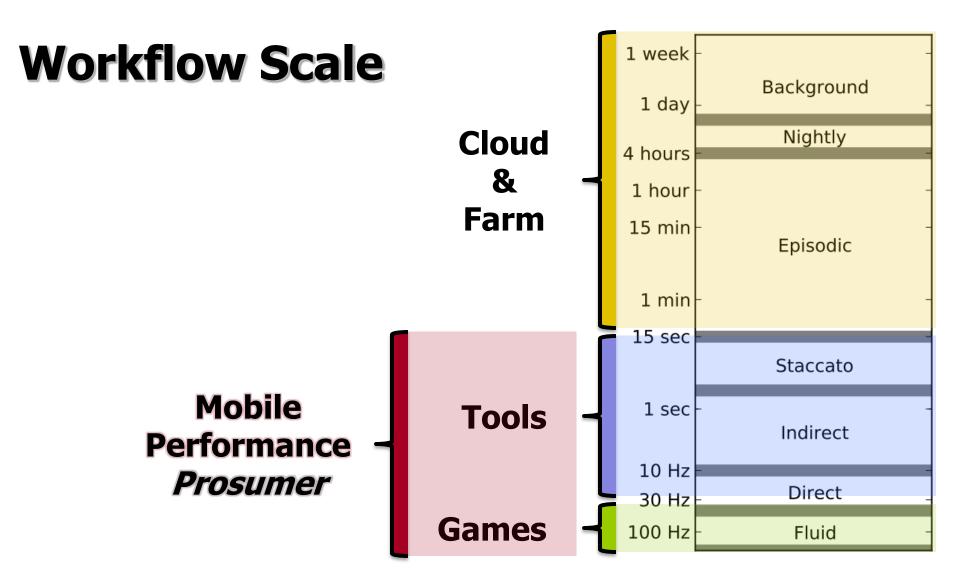

Enderton & Wexler, "The Workflow Scale: Why 5x Faster Might Not Be Enough", CGI 2011

## What's Shared Memory?

- No copies (OpenGL API forces copies)

- Simplified synchronization (map/unmap, fence, cache flush)

- Shared virtual address space (segmented ok)

- Texture instead of attributes? (Why VAR failed?) Must be able to dynamically generate geometry on GPU and CPU (© GLES3)

- Gosh, it would be really nice if pointers Just Worked ™

- Shared memory uses less power & less bandwidth

## Leapfrog Opportunity

- We tried and failed for 10 years to move more algorithms to the GPU due to the lack of shared memory and the cost of bandwidth.

- Mobile UMA eliminates the bottleneck, fix the APIs and apps will follow.

- Shared memory is *lower power* → inevitable.

- Shared memory is *transformative* → whole new classes of apps.

Thanks to Cass Everitt, Eric Enderton

#### AFTERNOON TUTORIAL

### **Die Stacking**

|             |                                                  | 0                       |

|-------------|--------------------------------------------------|-------------------------|

| 2:00 – 2:15 | 3-D Stacking Tutorial Introduction               | Liam Madden, Xilinx     |

| 2:15 – 3:05 | Foundry TSV Enablement                           | Remi Yu, <b>UMC</b>     |

|             | For 2.5D/3D Chip Stacking                        |                         |

|             | Full Processing Interposer Process               | Choon Lee, Amkor        |

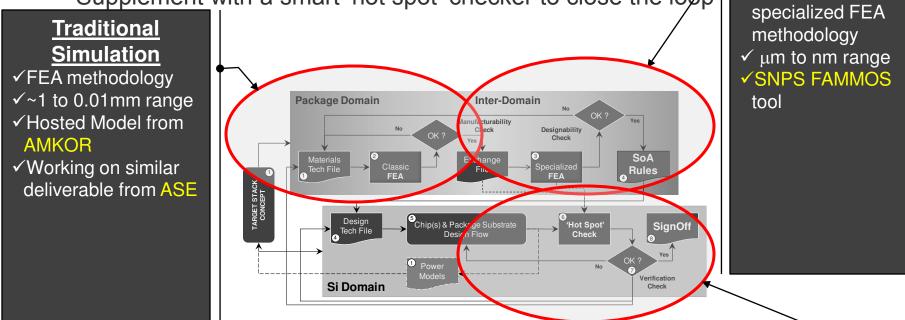

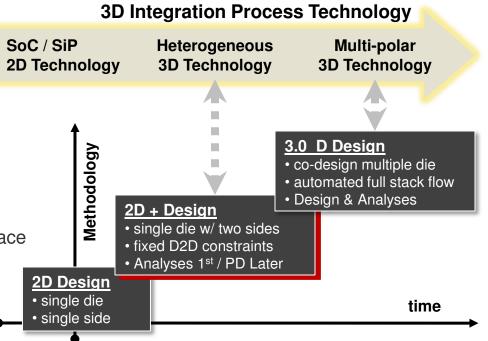

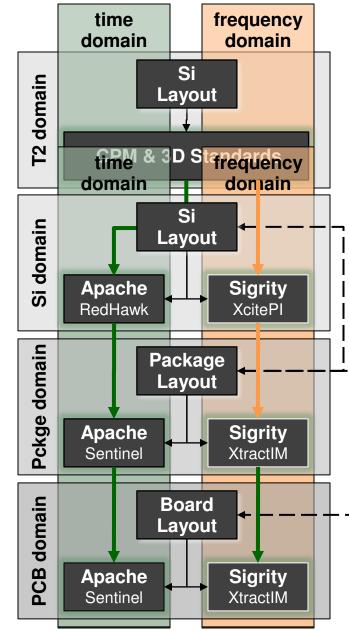

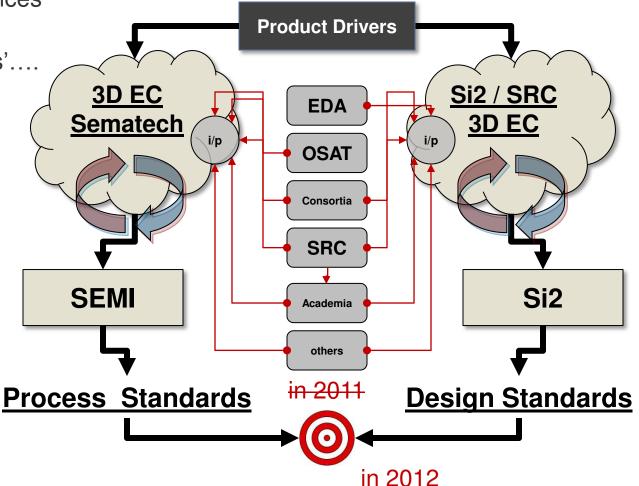

| 3:05 – 3:55 | Roadmap for Design and EDA                       | Riko Radojcic, Qualcomm |

|             | Infrastructure for 3D Products                   |                         |

|             | Xilinx SSI Technology                            | Shankar Lakka, Xilinx   |

|             | Concept to Silicon Development<br>Overview       |                         |

| 3:55 – 4:10 | Break                                            |                         |

| 4:10 – 5:00 | Memory Consideration and<br>Heterogeneous Die    | Bryan Black, <b>AMD</b> |

|             | Optical Backplanes with 3D Integrated Photonics? | Ephrem Wu, Xilinx       |

| 5:00 – 5:30 | Panel                                            |                         |

| 5:30 - 7:00 |                                                  |                         |

|             | Reception                                        |                         |

|             | •                                                |                         |

Copyright © 2012 HOTCHIPS. All rights reserved. All trademarks property of their respective owners.

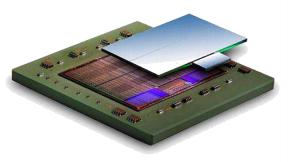

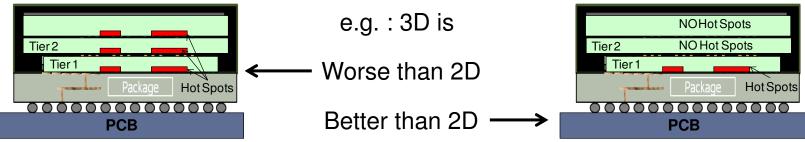

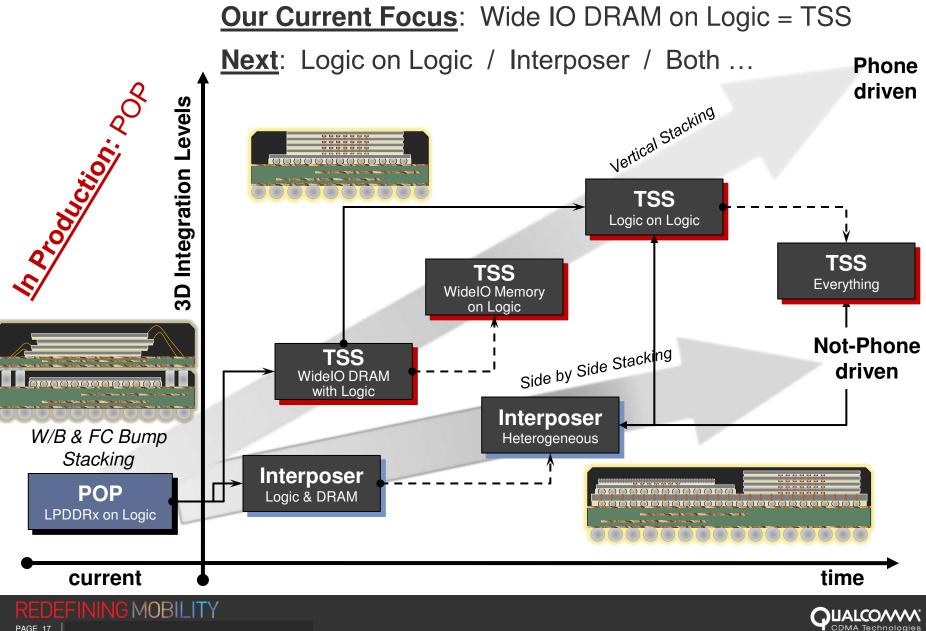

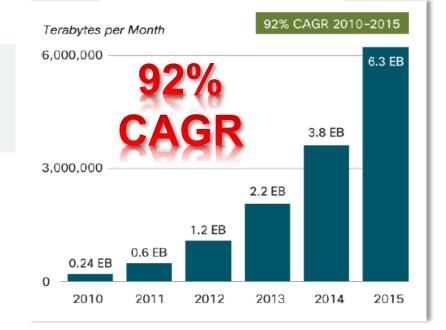

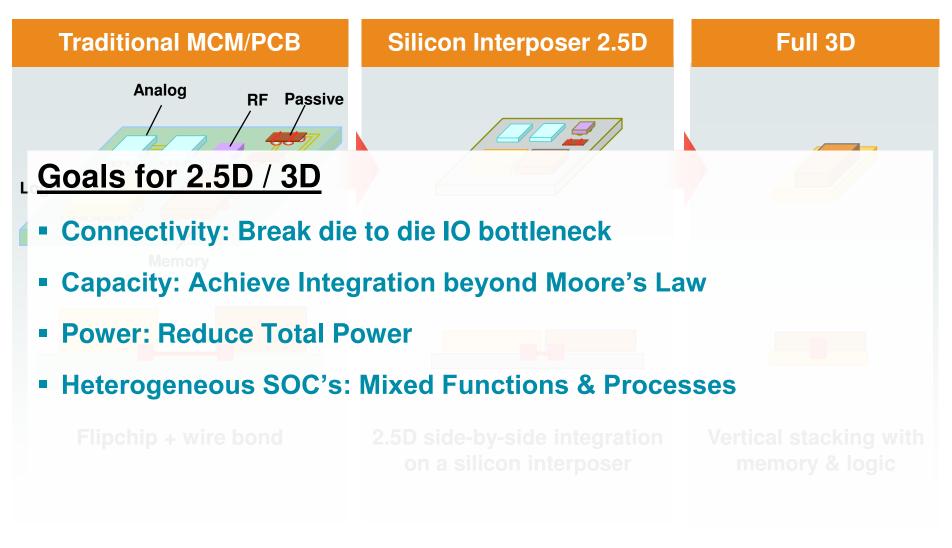

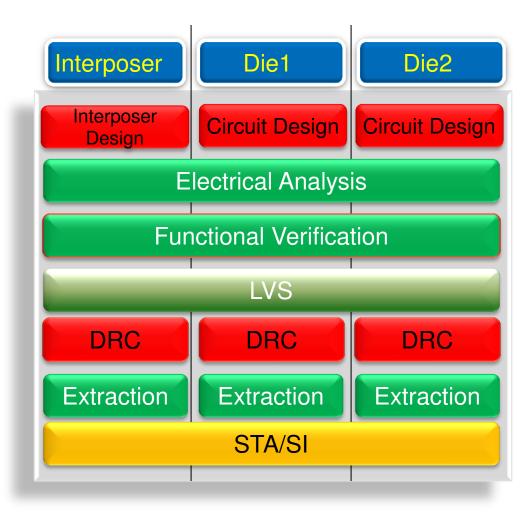

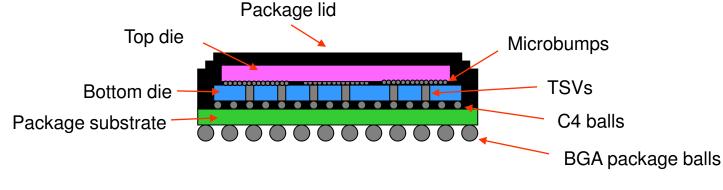

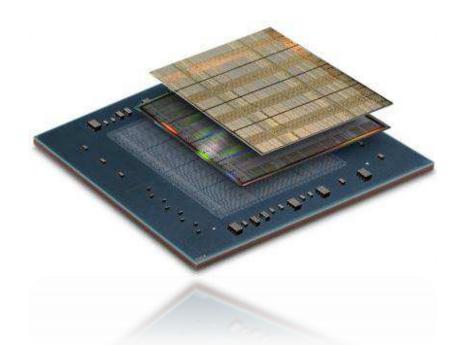

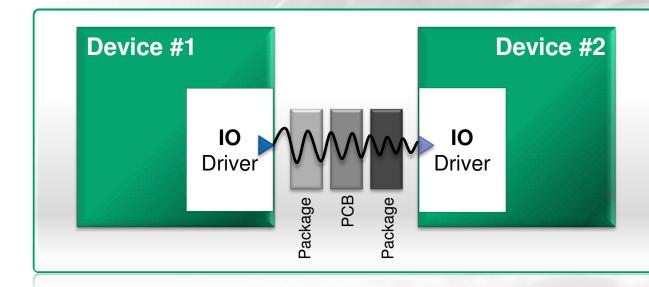

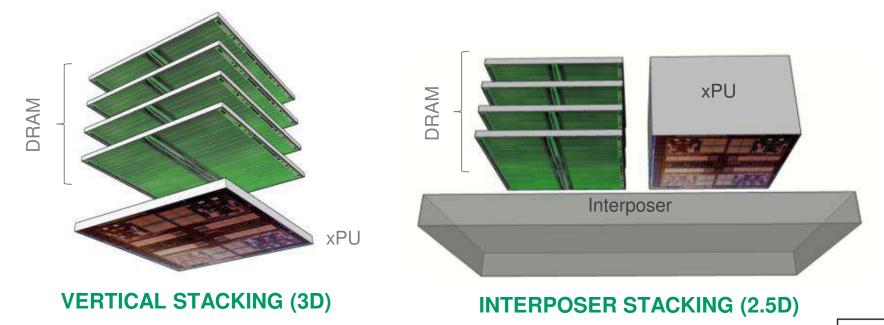

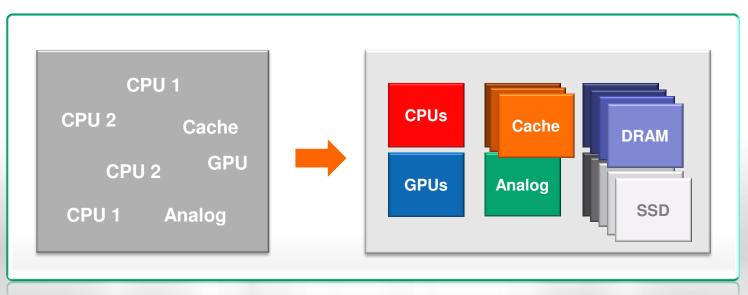

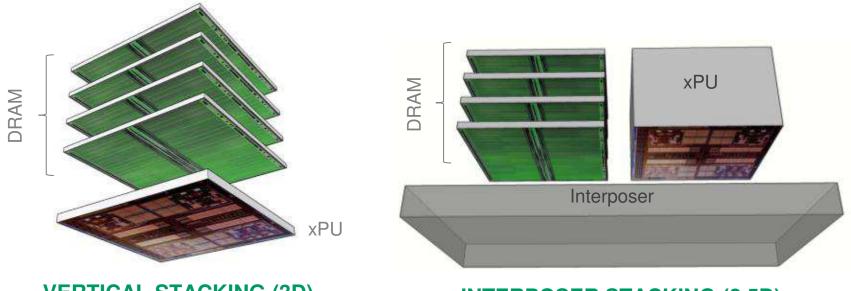

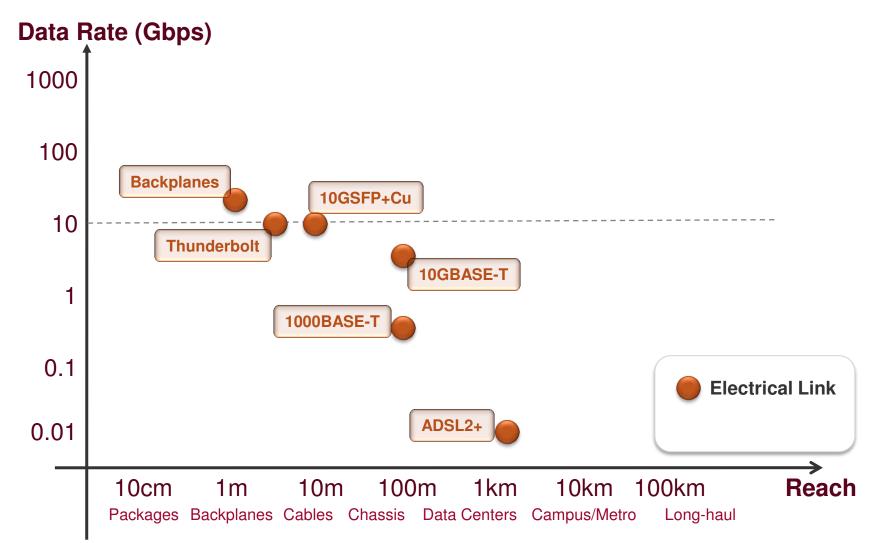

#### Die Stacking

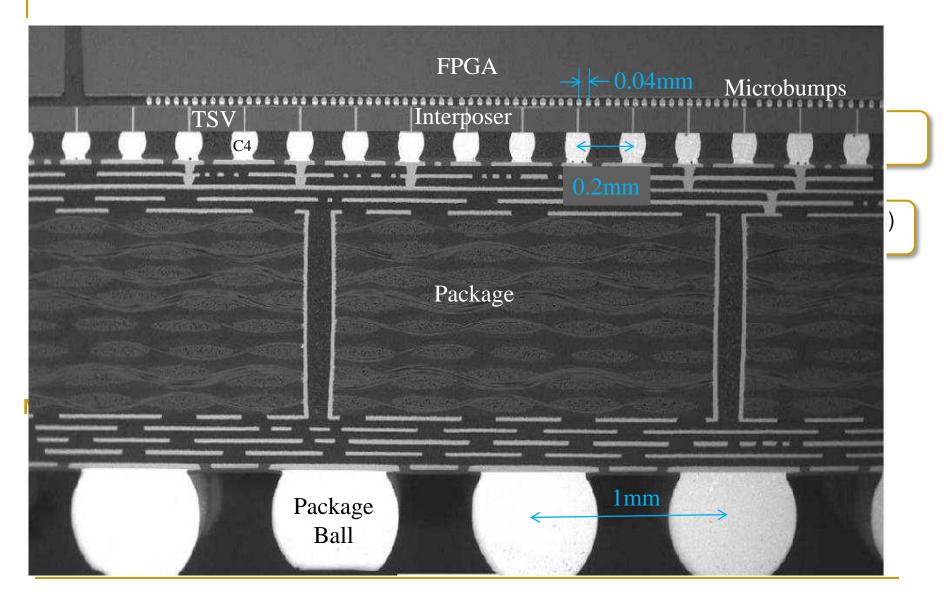

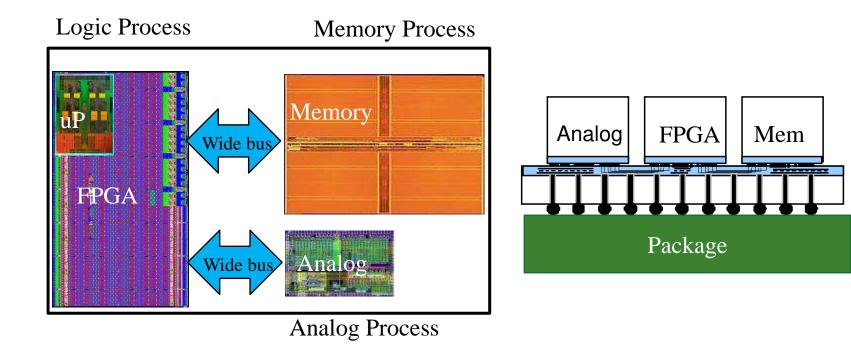

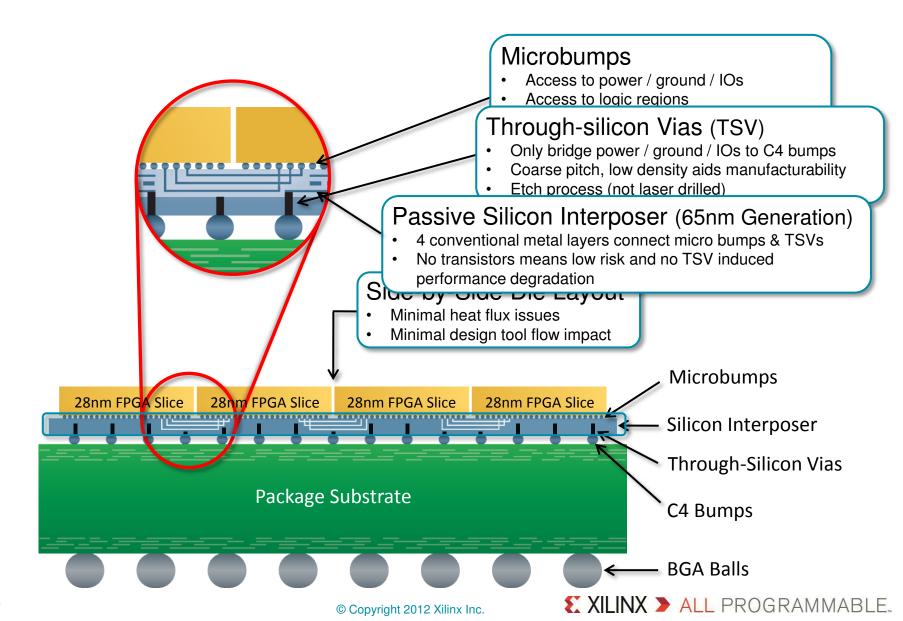

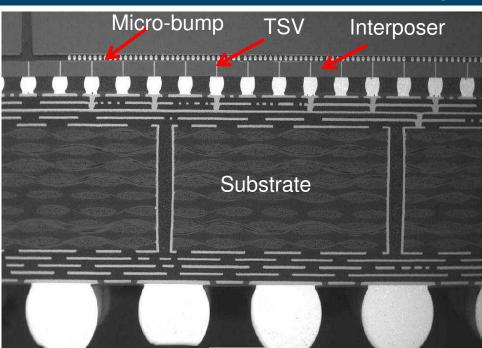

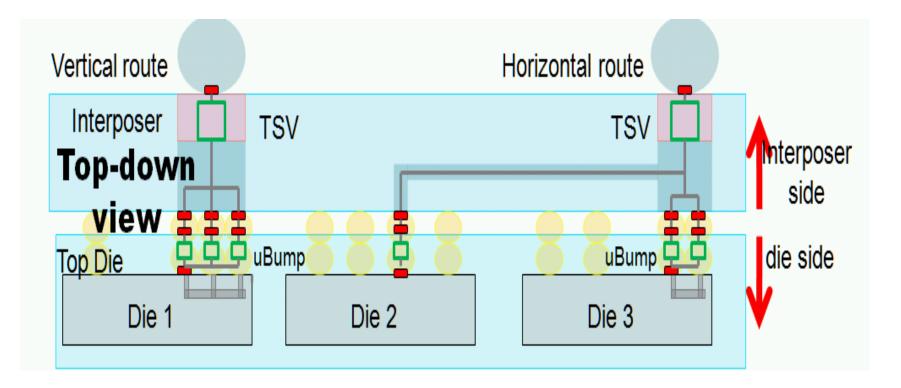

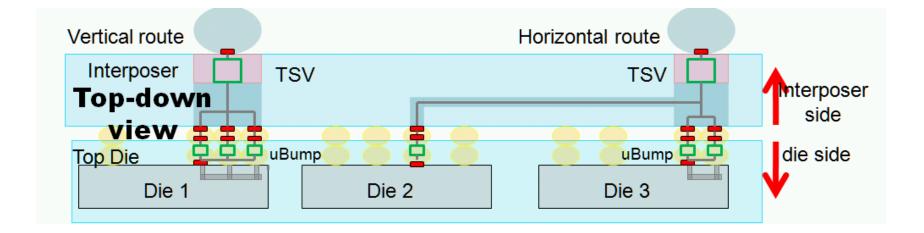

2.5D/3D die stacking increases aggregate inter-chip bandwidth and shrinks board footprint while reducing I/O latency and energy consumption. By integrating in one package multiple tightly-coupled semiconductor dice – each possibly in a process optimized for power, performance and costs for a particular function – this technology gives system designers additional options to partition and scale solutions efficiently. Die stacking has already transformed the design of high-end CMOS image sensors, and it promises to also enhance FPGA, graphics and mobile applications.

In Part 1 of this tutorial we will examine the key enabling technologies such as silicon interposer, TSV, micro-bump and assembly integration. In Part 2 we will cover the design considerations & trade-offs of 2.5D/3D in CAD, ESD and architecture. Part 3 will showcase how the technology is used in systems and applications for memory integration, optics integration and monolithic die partitioning. Schedule

2:00pm – 2:15pm: Introduction by Liam Madden from Xilinx

2:15pm – 3:05pm: Technology Fab, Interposer and TSV by Remi Yu from UMC Assembly and Micro Bumps by Choon Lee from Amkor

3:05pm – 3:55pm: Design Considerations 3D, CAD and Floorplanning by Riko Radojcic from Qualcomm 2.5D, CAD and ESD by Shankar Lakka from Xilinx

3:55pm – 4:10pm: Break for refreshments

4:10pm – 5:00pm: System Implications Memory Consideration and Heterogeneous Die by Bryan Black from AMD Optical Considerations by Ephrem Wu from Xilinx

5:00pm - 5:30pm: Panel moderated by Liam featuring all the speakers

Copyright © 2012 HOTCHIPS. All rights reserved. All trademarks property of their respective owners.

August 22 to 24, 2010 Memorial Auditorium, Stanford University A Symposium on High Performance Chips Sponsored by the IEEE Technical Committe on Microprocessors and Microcomputers

#### **3-D Stacking Tutorial** Introduction

Liam Madden Corporate Vice President Xilinx Aug 27<sup>th</sup> 2012

#### **Dedicated to the Memory of Chuck Moore: Visionary**

Chuck Moore, AMD Corporate Fellow 1961-2012

#### Agenda

- Introduction: Liam Madden, Corp VP, Xilinx (2:00-2:15)

- Technology: (2:15-3:05)

- Foundry: Remi Yu, Director Marketing, UMC

- OSAT: ChoonHeung Lee, Corp VP, Amkor

- Design Considerations: (3:05-3:55)

- Mobile Communications: Riko Radojcic, Director, Qualcomm

- FPGA: Shankar Lakka, Director Integration, Xilinx

- Break (3:55-4:10)

- System Implications (4:10-5:00)

- Processor and GPU: Bryan Black, Senior Fellow, AMD

- Integrated Optics, Ephrem Wu, Senior Director, Xilinx

- 5:00-5.30 Panel Discussion

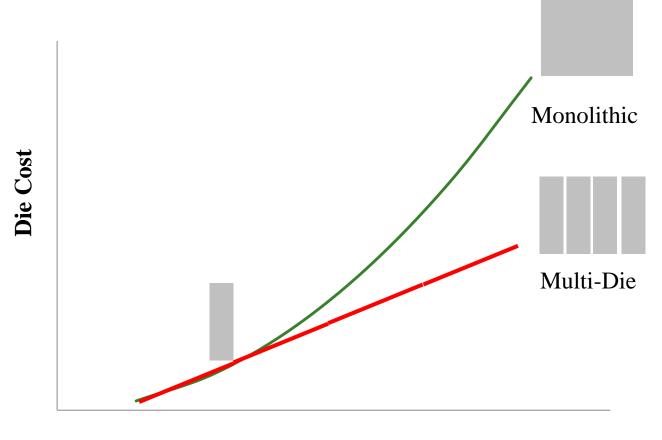

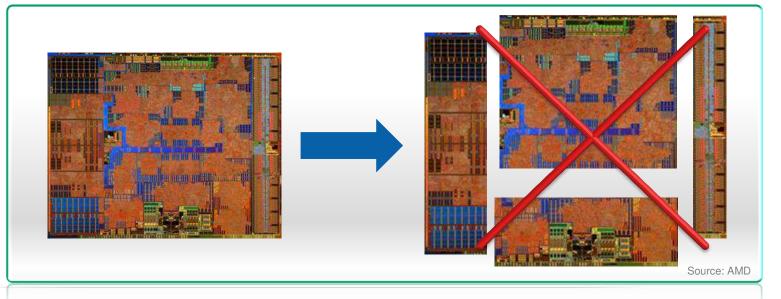

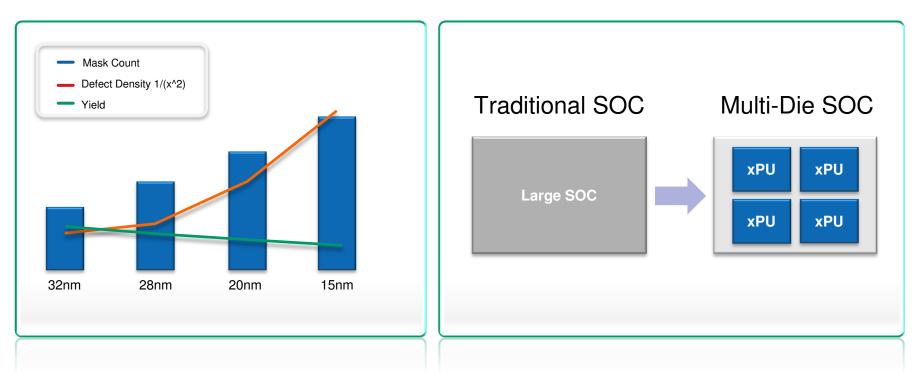

#### **Cost Comparison: Monolithic vs Multi-Die**

"Moore's Law is really about economics" Gordon Moore

**Die Area**

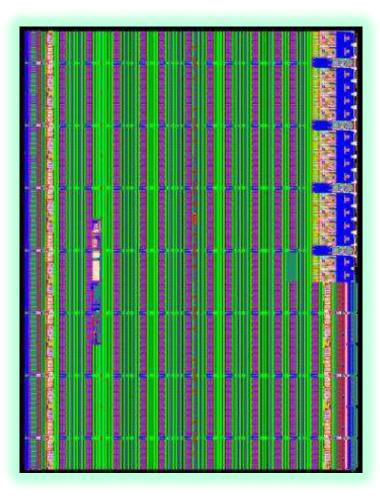

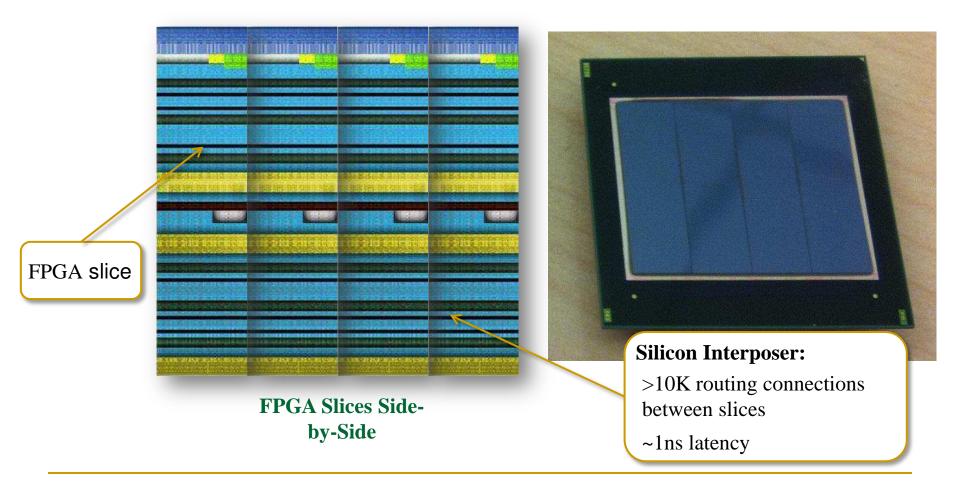

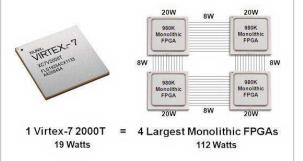

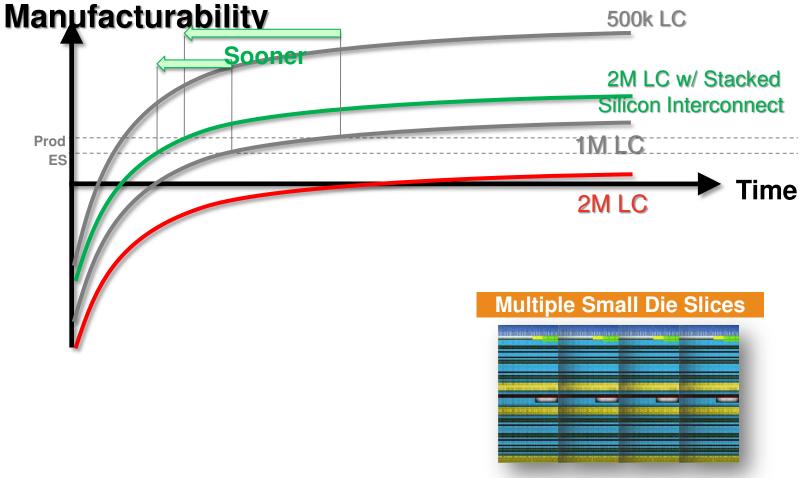

#### Why is first 3D logic product an FPGA?

- Natural partition using "long lines"

- Very low "opportunity cost"

- No 3<sup>rd</sup> party dependence

- "Size matters" to customers

- Compelling value proposition "next generation density in this generation technology"

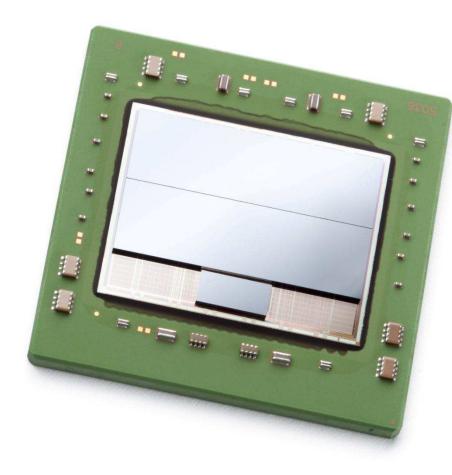

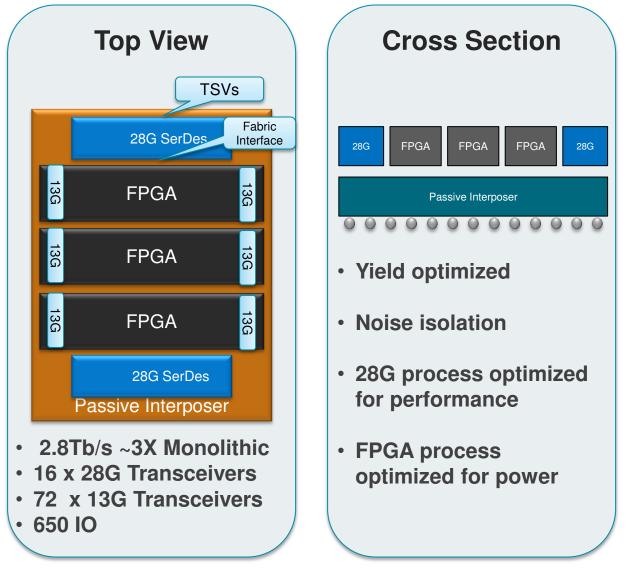

#### **Virtex 2000T: Homogeneous Stacked Silicon Interconnect Technology (SSIT)**

**Elements of SSIT**

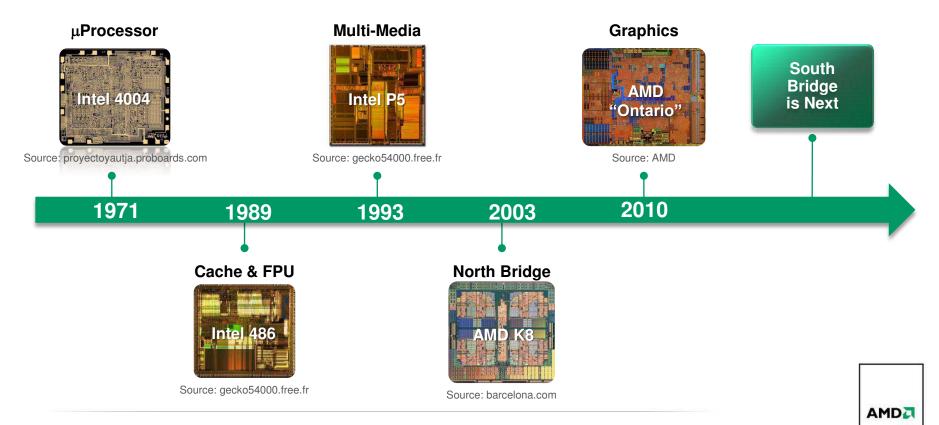

#### **3 Decades of Microprocessor Integration: A personal history**

"Integrate or be integrated" Fred Webber, former CTO AMD

| Year | Company   | Product | Integration Level |      |     |       |      |                 |     |  |

|------|-----------|---------|-------------------|------|-----|-------|------|-----------------|-----|--|

|      |           |         |                   | Core |     |       | L2\$ | North<br>Bridge | GPU |  |

|      |           |         |                   | DP   | Ctl | L1 \$ | FPU  |                 |     |  |

| 1983 | Harris    | J11     | 4um               |      |     |       |      |                 |     |  |

| 1989 | DEC       | Rigel   | 1.5um             |      |     |       |      |                 |     |  |

| 1991 | DEC       | Alpha   | 0.75um            |      |     |       |      |                 |     |  |

| 2005 | Microsoft | Xenon   | 90nm              |      | 3 ( | Core  |      |                 |     |  |

| 2011 | AMD       | Fusion  | 40nm              |      | 2 ( | Core  |      |                 |     |  |

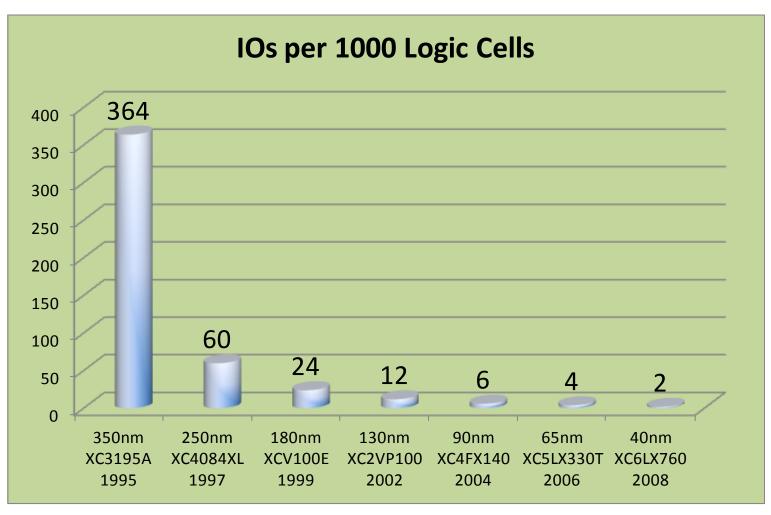

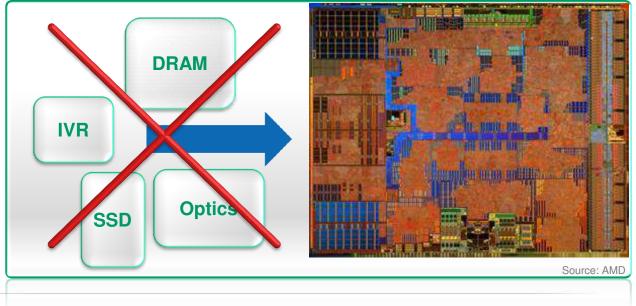

What happened to System on a Chip?

|                               | Logic                            | Memory                                  | Analog                            |

|-------------------------------|----------------------------------|-----------------------------------------|-----------------------------------|

| Global Revenue 2011           | \$150B                           | \$68B                                   | \$45B                             |

| Moore Scaling                 | Good (except I/O)                | Good (except I/O)                       | Poor                              |

| Technology "Vintage"          | 2012                             | 2012                                    | 2000                              |

| Transistor<br>Characteristics | High performance/<br>Low leakage | Low leakage/<br>moderate<br>performance | Stable with good voltage headroom |

| Metallization                 | >9 layers                        | <5 layers                               | <6 layers                         |

| Differentiators               | High density logic               | Charge storage                          | Passives, Optical                 |

#### **Crossing the packaging chasm**

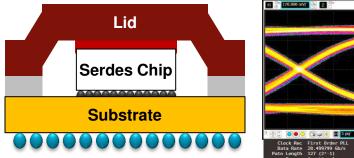

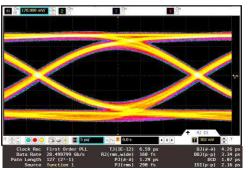

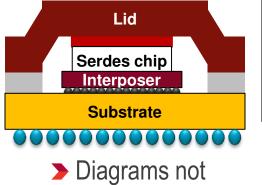

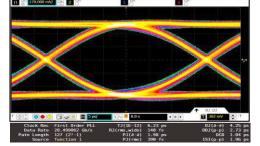

#### 7V580T – Dual FPGA Slice with 8x28Gb/s SerDes Die

#### Virtex-7 HT @ 28Gbps

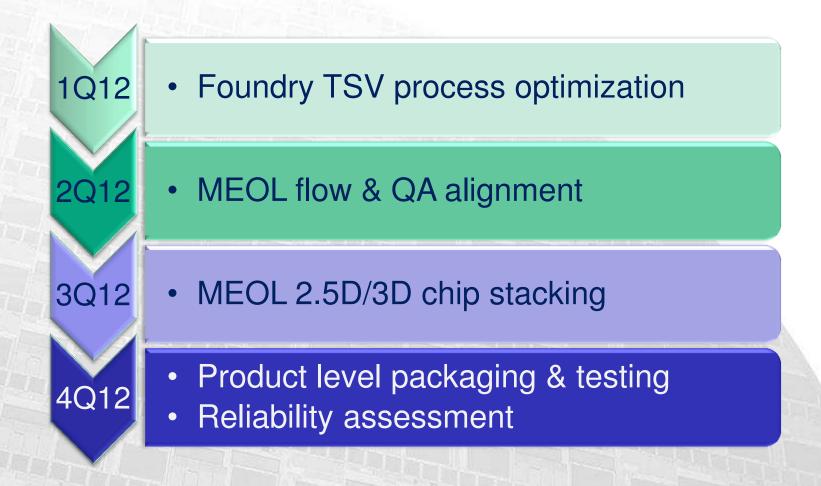

## Foundry TSV Enablement For 2.5D/3D Chip Stacking

Remi Yu, UMC Hot Chips 24 August 27, 2012

**Customer-Driven Foundry Solutions**

## Outline

2.5D/3D Applications

Foundry TSV Enablement

Ecosystem Work Flow

Summary

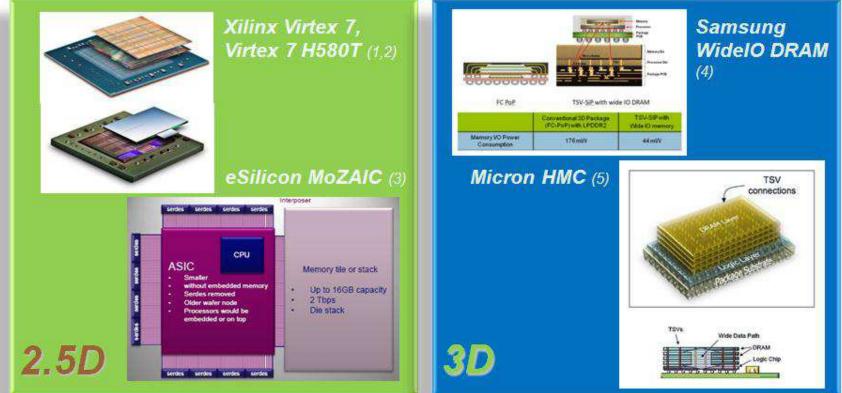

## 2.5D/3D Applications

**Customer-Driven Foundry Solutions**

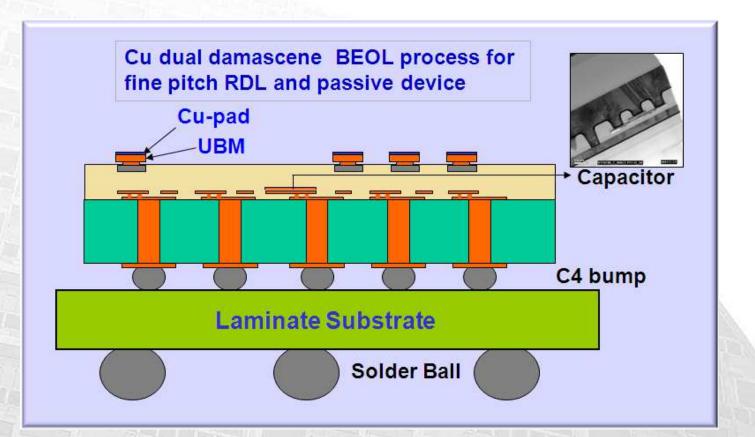

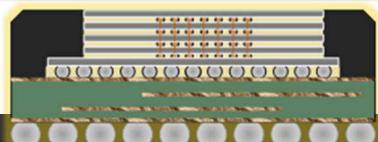

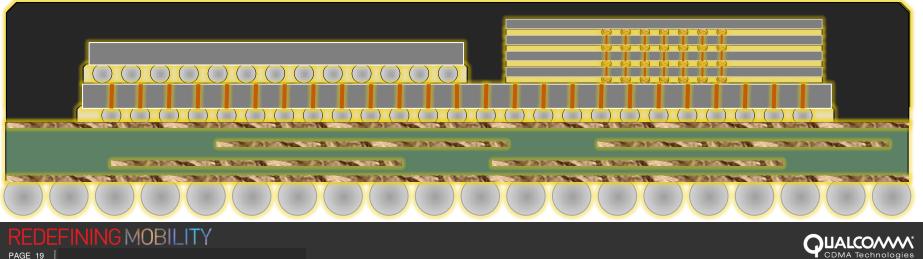

## 2.5D Si Interposer Stacking

## Logic/logic: FPGA, networking infrastructure Logic/memory: Gaming, HPC

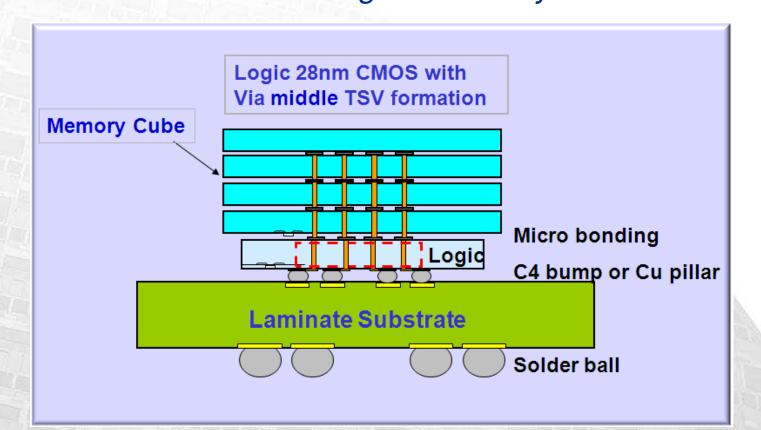

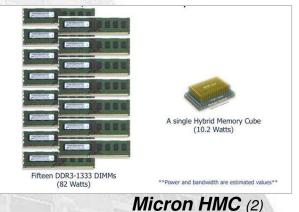

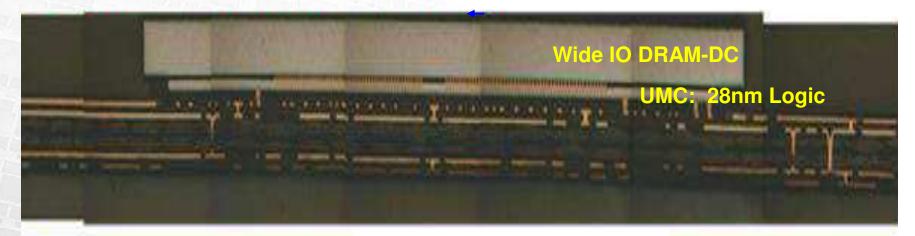

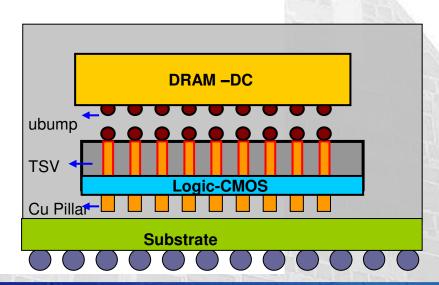

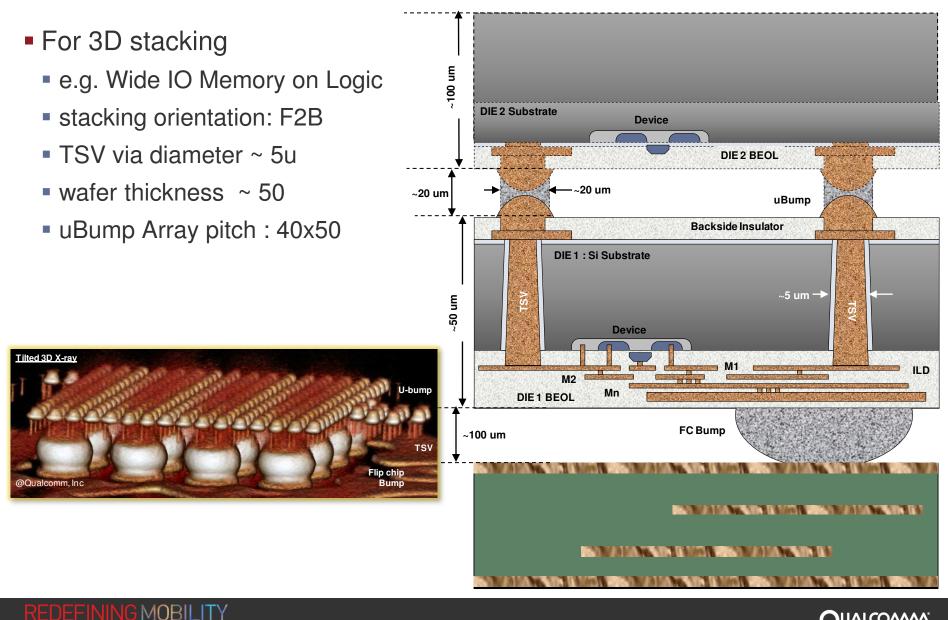

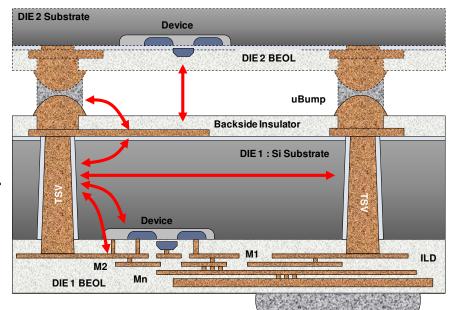

### **3D Logic/Memory Stacking** - Via-Middle TSV 28nm Logic + Memory Cube

### Mobile WidelO, Computing WidelO, HMC

# **Application Examples**

### - More are being developed

(1) http://low-powerdesign.com/sleibson/2011/10/25/

generation-jumping-2-5d-xilinx-virtex-7-2000t-fpga-delivers-1954560-logic-cells-consumes-only-20w/

- (2) http://eda360insider.wordpress.com/2012/06/01/

- friday-video-3d-thursday-xilinx-virtex-7-h580t-uses-3d-assembly-to-merge-28gbps-xceivers-fpga-fabric/

- (3) eSilicon, "GSA 3D Working Group", July 2012

- (4) http://www.ecnmag.com/news/2011/03/samsung-wide-io-memory-mobile-products-deeper-look

- (5) http://denalimemoryreport.com/2012/06/28/arm-hp-and-sk-hynix-join-hybrid-memory-cube-consortium-hmcc-first-spec-due-by-end-of-year/

### UMC

# **Cost-of-Ownership Advantages**

#### **Motivations:**

Higher BW, lower W/BW, smaller form-factor

### **Opportunity of return on 3D IC investment:**

- Chip process node optimization

- Homogeneous partition

- Cross-node combinations

- BOM cost optimization

- Less demanding substrate/PCB, lighter cooling assembly, ...

- Ultimately: better product, better margin

#### Xilinx Virtex 7 (1)

(1) http://low-powerdesign.com/sleibson/2011/10/25/ generation-jumping-2-5d-xilinx-virtex-7-2000t-fpga-delivers-1954560-logic-cells-consumes-only-20w/

(2) http://www.i-micronews.com/news/Micron-Samsung-TSV-stacked-memory-collaboration-closer-look,7766.html

### UMC

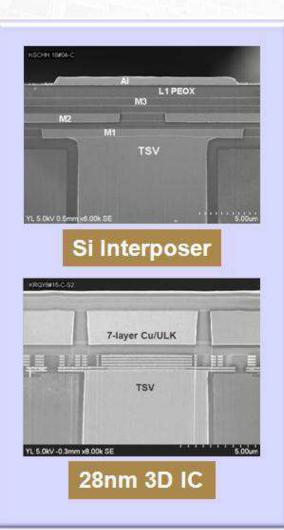

## **Foundry TSV Enablement**

# Foundry TSV Process Technology

### Mainstream: Via-middle Cu TSV

- 2.5D: 65nm-generation BEOL

- 3D: 28nm CMOS logic

After 28nm entry, TSV for 3D may come as a standard option for foundry CMOS logic at 20nm and beyond

### UMC

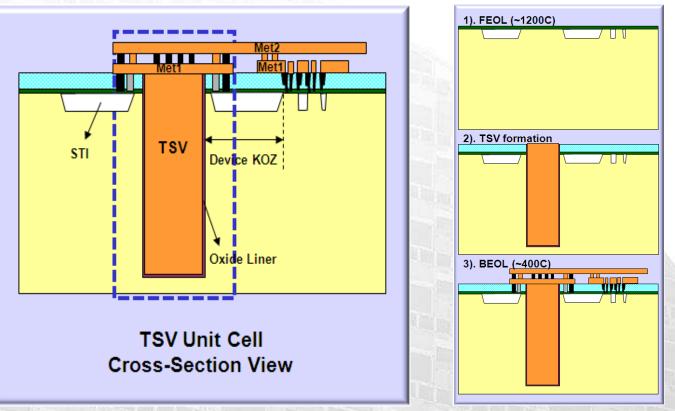

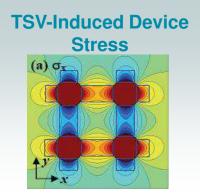

# - Via-Middle TSV for 3D

(drawn not to scale)

### TSV formed after CMOS, before contact/metal

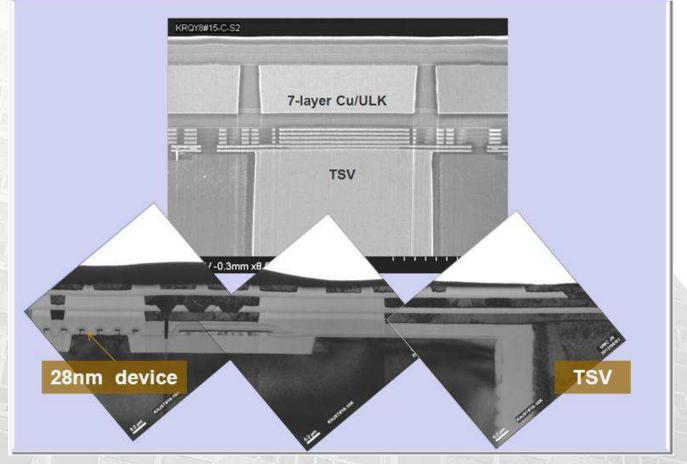

### UMC 28nm 3D IC

(CMOS device and TSV in proportion)

### UMC

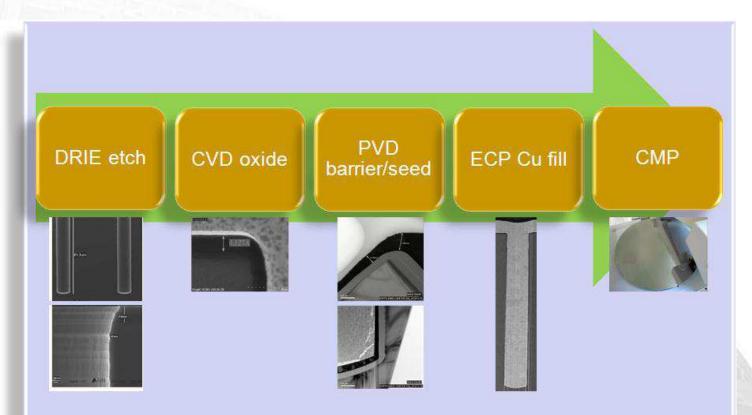

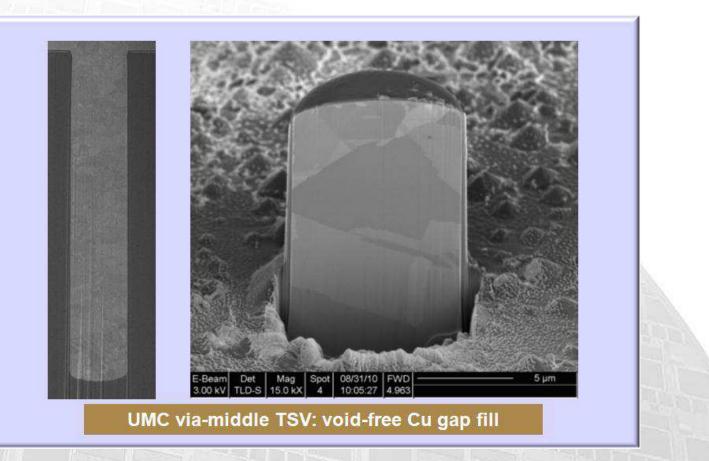

### **UMC Via-Middle TSV Unit Process**

Leveraging existing CMOS tools and capability

Size is new to fab practice: diameter/depth

### UMC

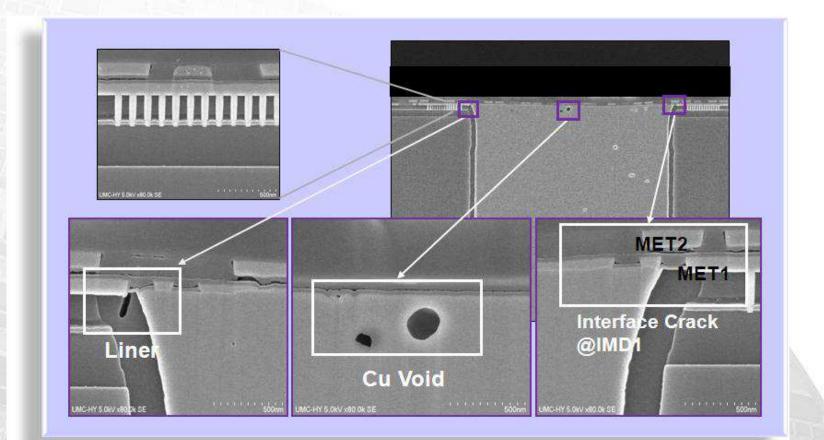

### Early Stage TSV Process Issues

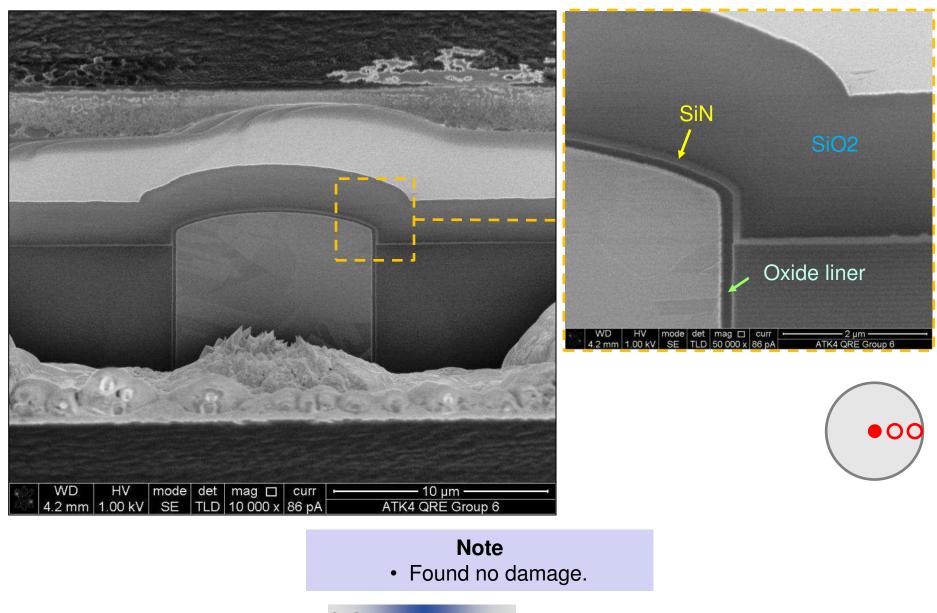

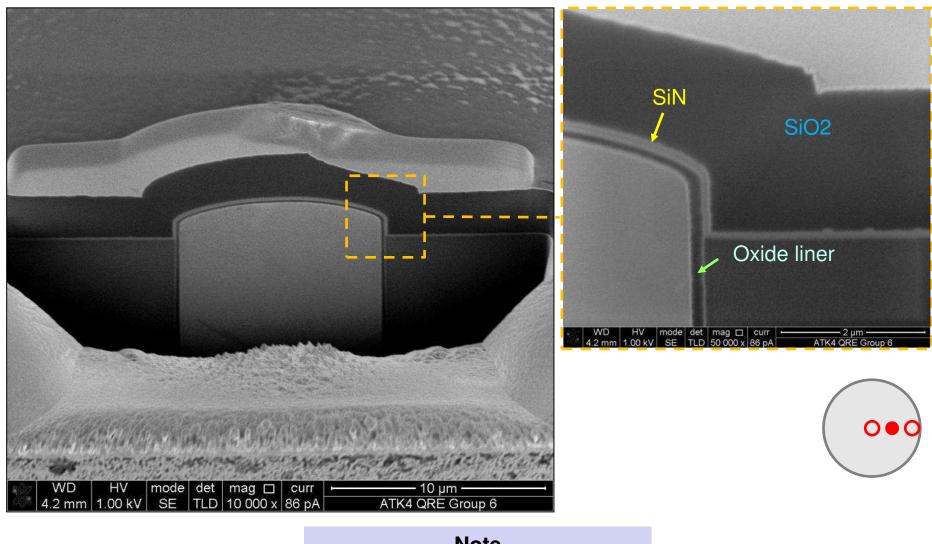

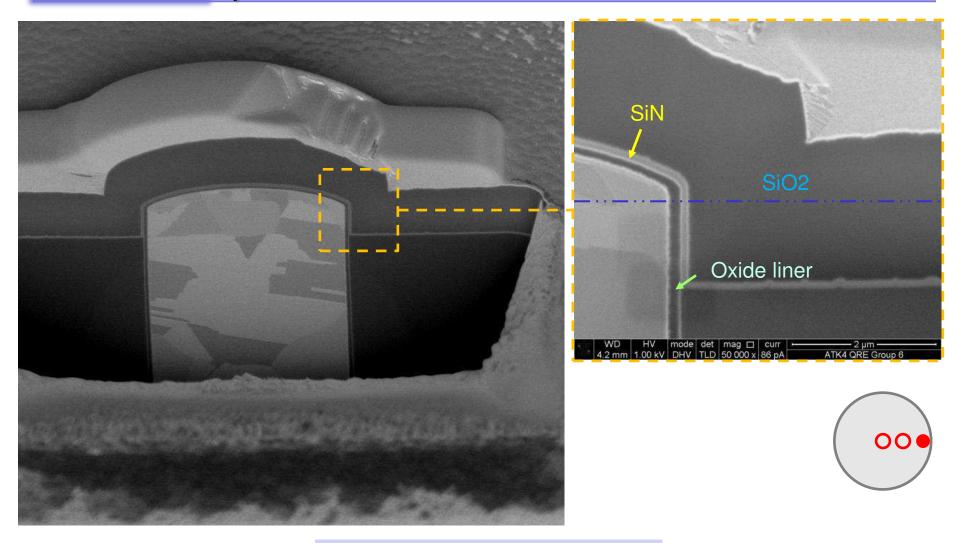

### TSV integrity – Cu fill, oxide liner, metal stack

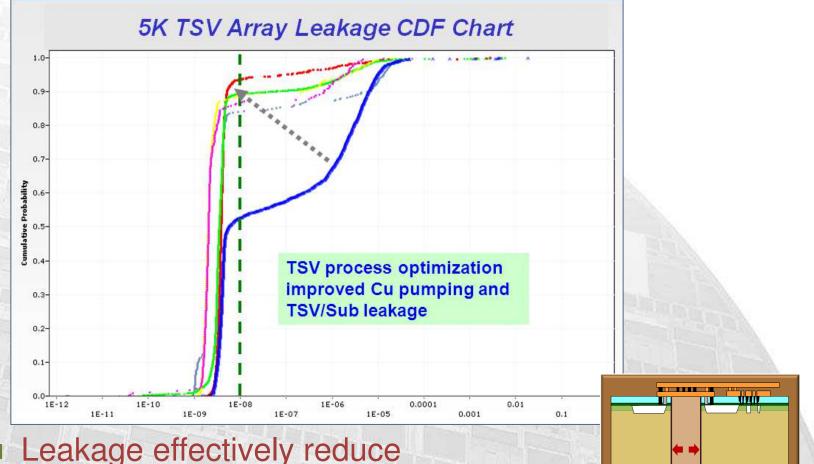

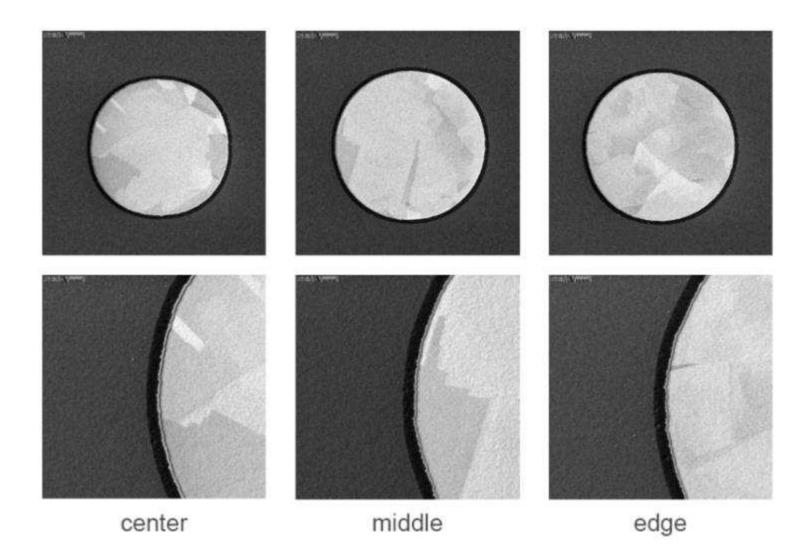

## **ECP Cu Fill Process Optimization**

### - Cu pumping reduction

### ECP Cu plating critical to TSV integrity

### **UMC Via-Middle TSV Solution**

#### UMC

### **TSV Top Side Impact Evaluation** - BEOL WAT testkeys

|                         |       |                       | Above TSV           | Cross TSV           | Beside TSV                | After Sinter          |  |

|-------------------------|-------|-----------------------|---------------------|---------------------|---------------------------|-----------------------|--|

| WAT<br>test item        | Layer | Testkey rule<br>(w/s) | TSK<br>Metz<br>Metz | Met2<br>Het1<br>Tsv |                           |                       |  |

| Metal<br>Bridge         | M3    | 1x W /1 x S           | Passed              | Passed              | Passed (min. x=1)         | No significant        |  |

|                         | IVIS  | 2x W /2x S            | Passed              | Passed              | n/a                       |                       |  |

|                         | M4    | 1xW/1xS               | Passed              | Passed              | Passed (min. x=1)         | change                |  |

|                         |       | 2x W /2x S            | Passed              | Passed              | n/a                       |                       |  |

| Metal<br>Resistan<br>ce | M3    | 1xW/1xS               | Passed              | Passed              | Comparable for variable x |                       |  |

|                         |       | 2x W /2x S            | Passed              | Passed              | n/a                       | No significant change |  |

|                         | M4    | 1x W /1 x S           | Passed              | Passed              | Comparable for variable x |                       |  |

|                         | W 4   | 2x W /2x S            | Passed              | Passed              | n/a                       |                       |  |

| Via<br>Bridge           | V3    | Com_run Via           | Passed              | Passed              | Comparable for variable x | No significant        |  |

|                         | V3    | Non_comVia            | Passed              | Passed              | Comparable for variable x | change                |  |

Routing over TSV allowed

**Customer-Driven Foundry Solutions**

**W**U

### **TSV Bottom Side Impact Evaluation** - Leakage CDF

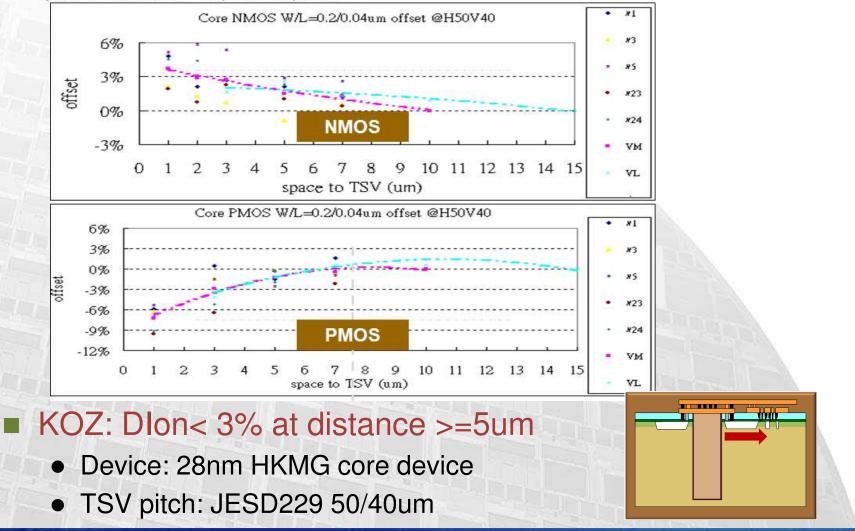

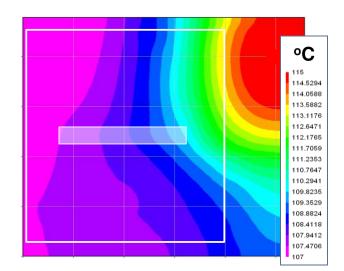

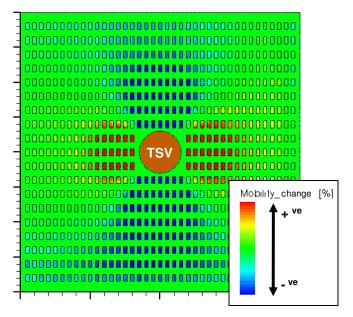

# **CMOS Impact Evaluation (3D)**

- Keep-Out Zone (KOZ) Characterization

### UMC

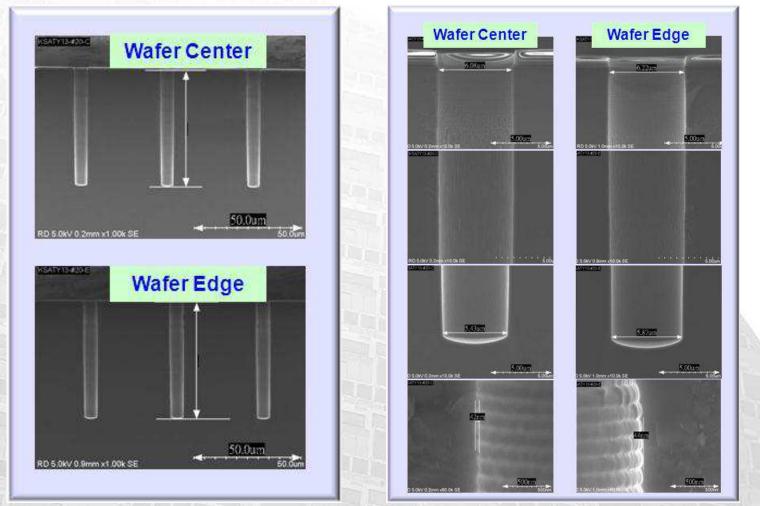

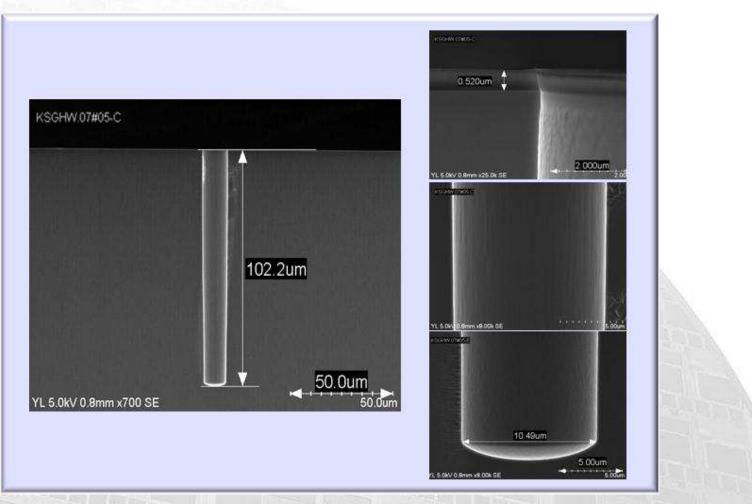

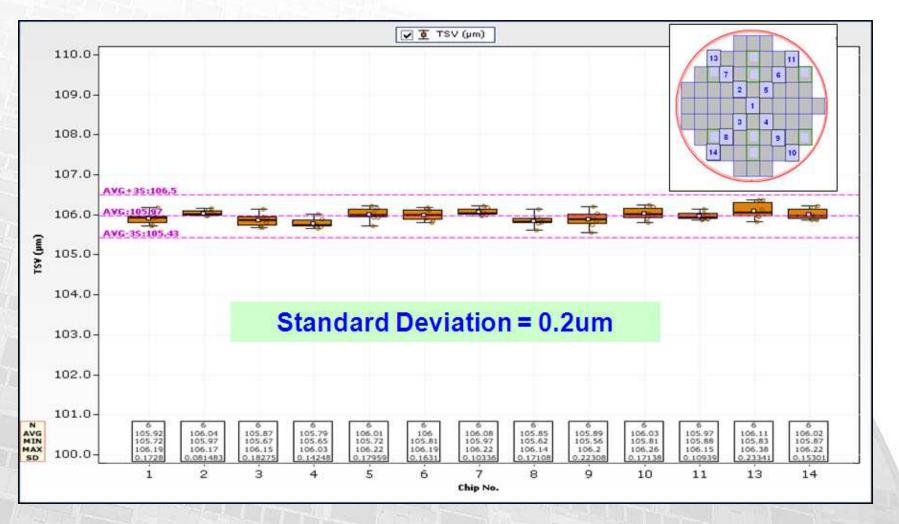

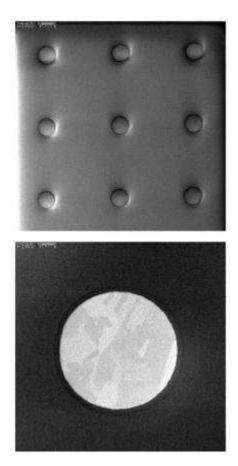

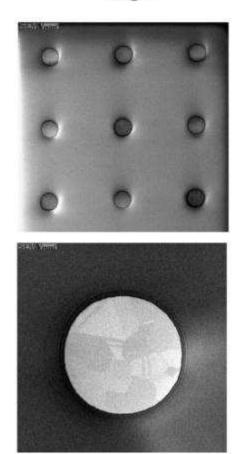

# Via Middle TSV (3D)

- 6um diameter, 54um depth

### UMC

## Si Interposer TSV (2.5D)

- 10um diameter, 100um depth

### UMC

# - 2.5D Si Interposer, 10x100um

#### UMC

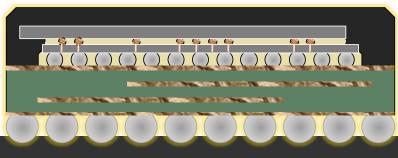

# **UMC 3D IC TV Stacking & Package**

#### **JEDEC WidelO interface**

#### UMC

# **Ecosystem Work Flow**

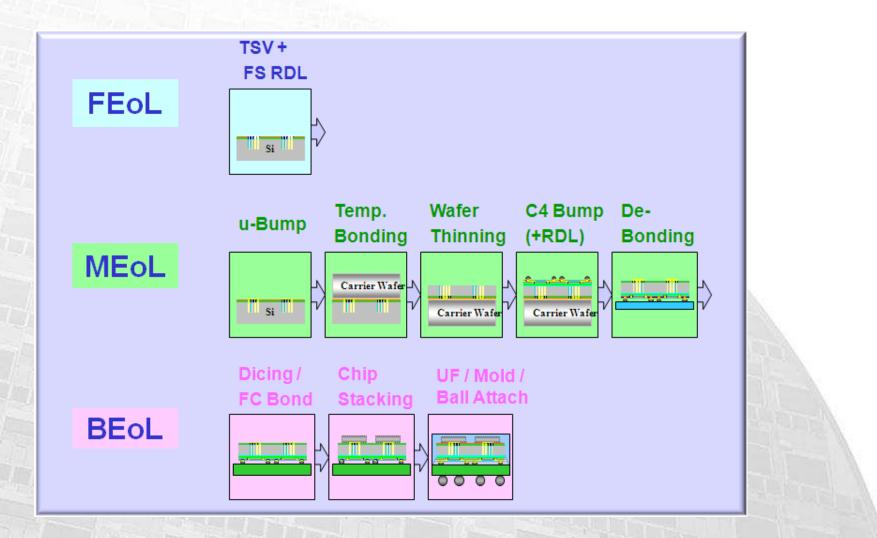

# **Example 2.5D Stacking Flow**

### UMC

### Various Work Models

|      |                 | FEOL    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MEOL           |                  | BEOL     |                         |  |  |

|------|-----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------|-------------------------|--|--|

|      |                 | Logic   | TSV + FS RD'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Wafer Thinning | BS RDL +<br>Bump | Assembly | Test                    |  |  |

|      | OSAT MEOL       |         | Foundry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | OS               | АT       |                         |  |  |

| 2.5D | Foundry MEOL    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Foundry        |                  | OSAT     |                         |  |  |

|      | Foundry Turnkey |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | Foundry          |          |                         |  |  |

|      | OSAT MEOL       | Foundry |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OS₽T           |                  |          |                         |  |  |

| 3D   | Foundry MEOL    |         | Fou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ndry           |                  | OSAT     |                         |  |  |

|      | Foundry Turnkey |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fou            | ndry             |          |                         |  |  |

|      |                 |         | and the second se |                |                  | 1000     | CONTRACTOR OF THE OWNER |  |  |

- Service scopes distinguished by MEOL inclusion

- Consult your foundry/OSAT

Work flow optimization may depend on BOM cost, stack recipe and test strategy

# Foundry TSV Design Collaterals

| Scheme                             | Feature Size               |                     |                                        |                         | Document Status          |                           |                       |                     |                     |

|------------------------------------|----------------------------|---------------------|----------------------------------------|-------------------------|--------------------------|---------------------------|-----------------------|---------------------|---------------------|

|                                    | TSV<br>CD/Depth<br>(um/um) | RDL<br>Cu<br>Layers | Cu<br>Thickness<br>/L /S<br>(um/um/um) | Al<br>Thickness<br>(um) | Topologic<br>Layout Rule | Electrical<br>Design Rule | Interconnect<br>Model | DRC<br>Command File | LVS Command<br>File |

| 1.0um-wide                         | 10/100                     | 0.13 Inductor       | 2.0<br>/1.00/1.00                      | 2.50                    | Ready                    | Ready                     | Ready                 | Ready               | Ready               |

| 0.4um-wide                         | 10/100                     | 55nm 4X             | 0.8<br>/0.40/0.40                      | 1.45                    | Ready                    | Ready                     | Ready                 | Ready               | Ready               |

| 0.56um-wide                        | 10/100                     | 65nm 6X             | 1.25<br>/0.56/0.56                     | 3.60                    | Ready                    | Ready                     | Ready                 | Ready               | Ready               |

| (UMC 2.5D Si interposer documents) |                            |                     |                                        |                         |                          |                           |                       |                     |                     |

### Consider TSV a passive device with rule decks/models

• Typical foundry engagement applies under ecosystem work flow

## **UMC Ecosystem Effort**

# Summary

# Summary

### Foundry TSV process demonstrated

- Applicable to both 2.5D/3D

- Leverage existing CMOS process technology

- Key process issues identified & conquered

- Ecosystem work flow

- Typical foundry/OSAT engagement flow applies for both 2.5D/3D, among other models

- Foundry TSV next step: ecosystem focus

- Product level reliability assessment

- Potential EDA collaboration for emerging 3D tools

## Thank you for your attention!

Contact lound Quind con or into@hour be dig.

### Full Processing Interposer Process

Hot Chips, Aug., 2012

Enabling a Microelectronic World<sup>®</sup>

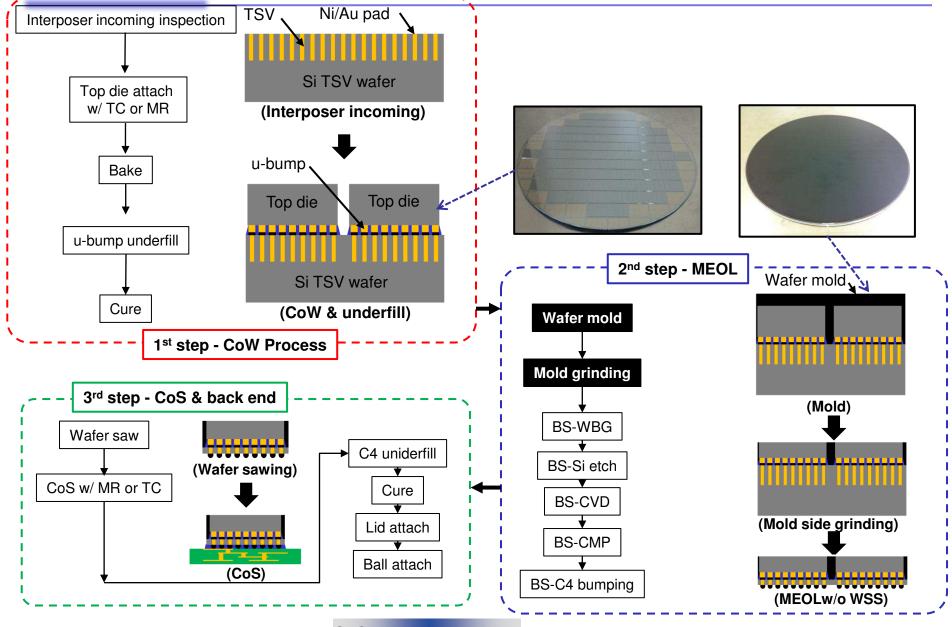

#### **Chip on Interposer First Process**

© 2012 Amkor Technology, Inc.

© Copyright Amkor

#### **Chip on Interposer First Process**

© 2012 Amkor Technology, Inc.

© Copyright Amkor

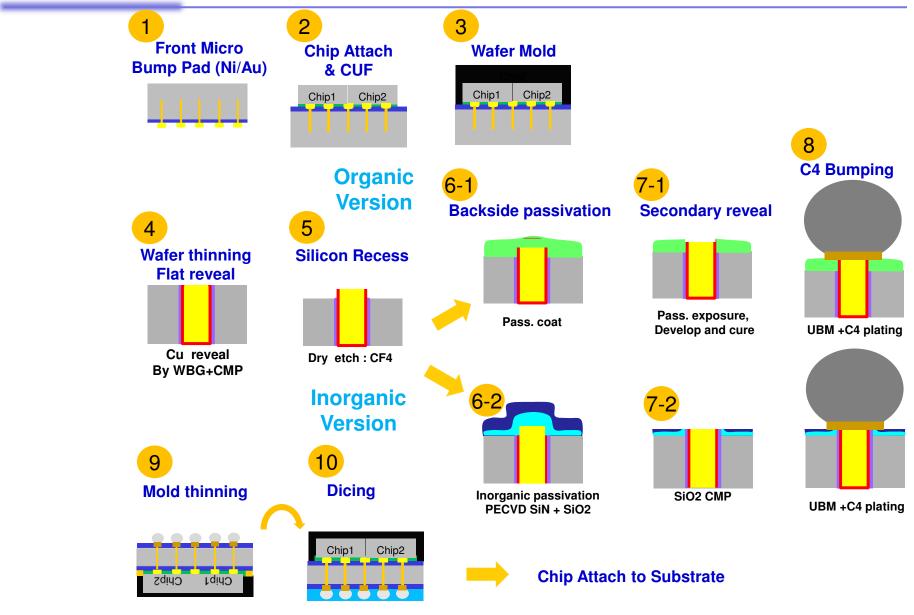

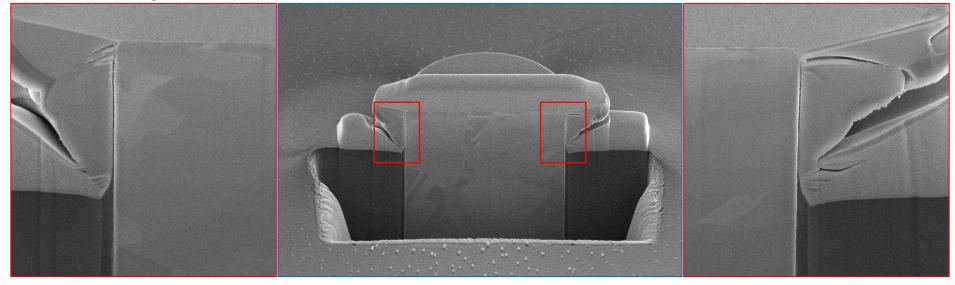

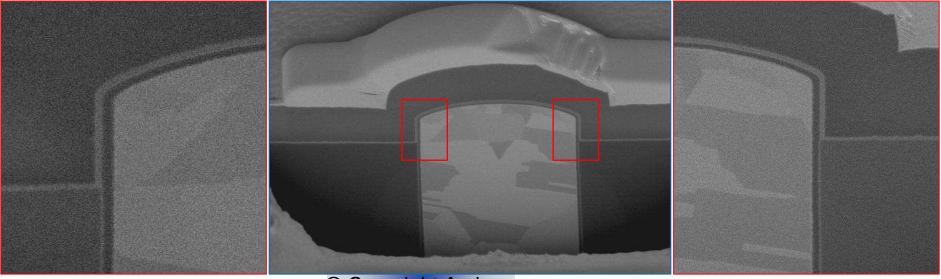

### Chip on Interposer First Process – High Level Risk 🕢

### **1** Front Micro Bump Pad

- Ni/Au Pad : Shape, Thickness, IMC embrittlement

# 2 Chip Attach & CUF : Chip Attach alignment, Flux cleaning, Underfill dispensing

**3** Wafer Mold : Warpage, Void

### Flat Reveal Wafer Thinning + CMP

– Wafer Cracking, Cu smearing, Cleaning

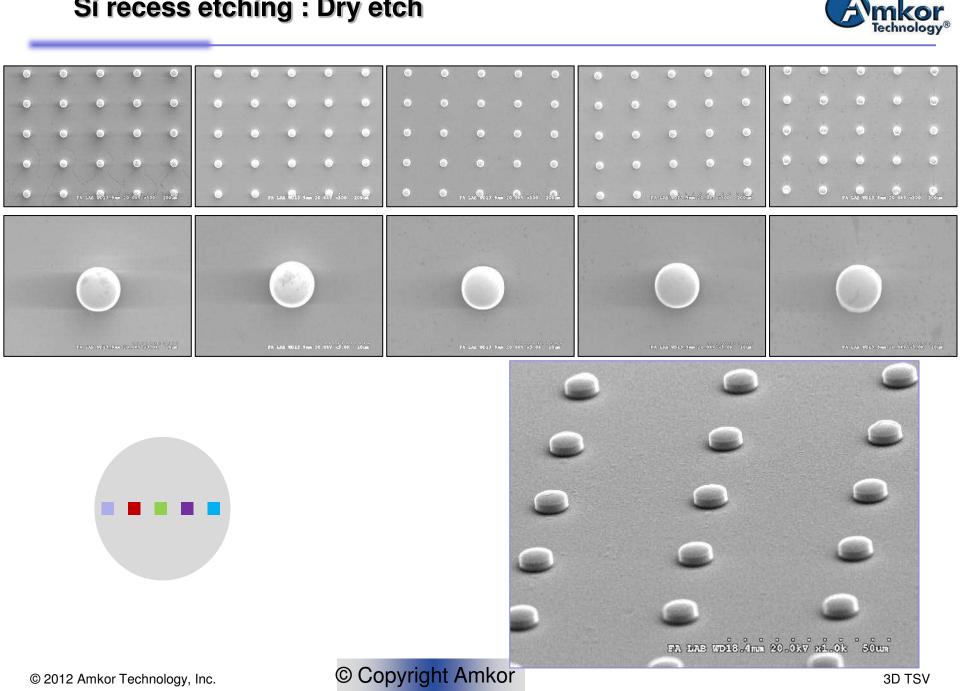

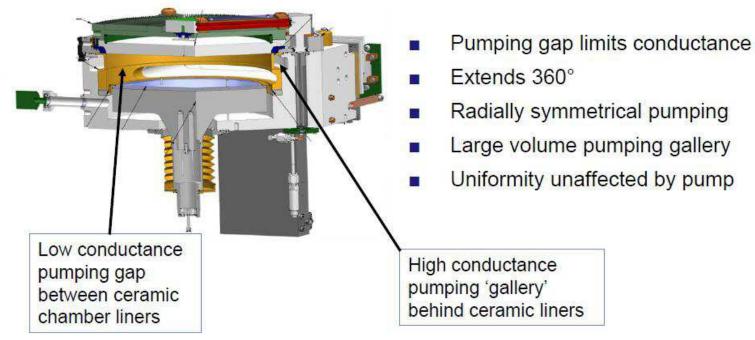

### 5 Silicon Recess – Dry Etch (CF4)

Cu corrosion, Etch rate variance, Slow Etch, Contaminate

### 6 Passivation – organic pass. coating, PECVD

– Wafer Cracking, Edge Arcing, Thickness/Stress control

### **7** Secondary Reveal – CMP : Wafer Cracking

**8** C4 Bumping

- 9 Mold Thinning (optional)

- 10 Dicing Saw street cracking

4

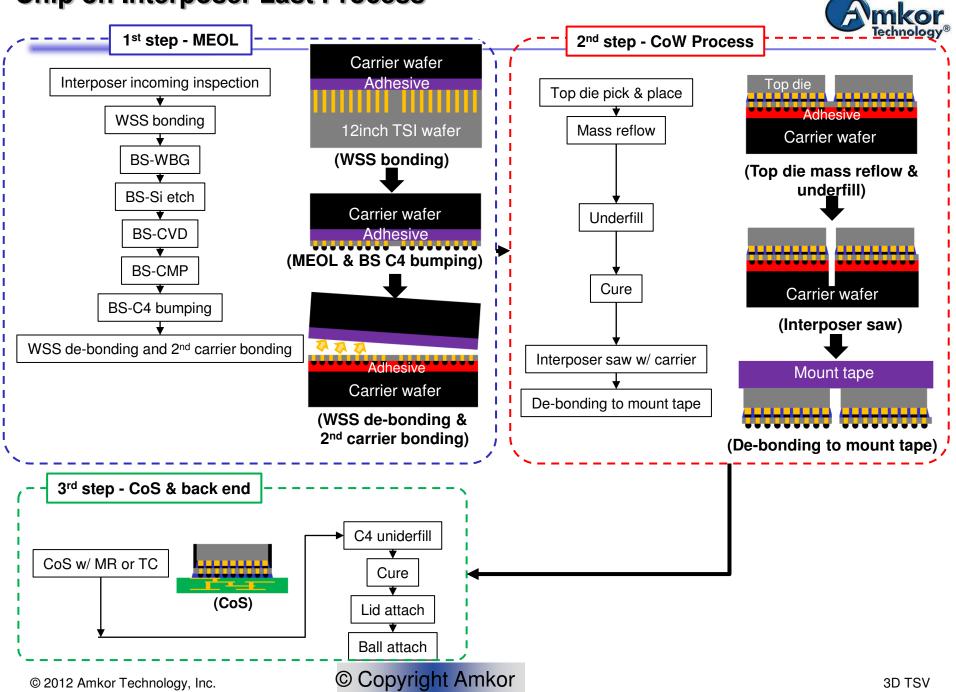

#### **Chip on Interposer Last Process**

#### **Chip in interposer Last Process**

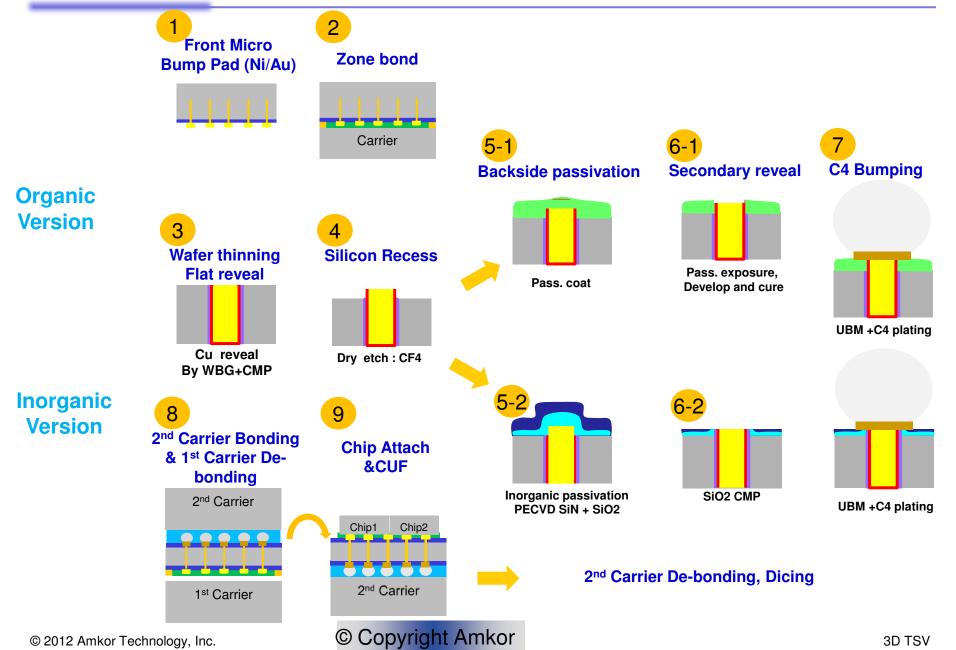

### Chip on Interposer Last Process – High Level Risk

#### **1** Front Micro Bump Pad

- Ni/Au Pad : Shape, Thickness, IMC embrittlement

### 2 Zone Bond : TTV Control

#### **3** Flat Reveal Wafer Thinning + CMP

– Wafer Cracking, Cu smearing, Cleaning

### 4 Silicon Recess – Dry Etch (CF4)

- Cu corrosion, Etch rate variance, Slow Etch, Contaminate

### **5** Passivation – Organic pass. coating, PECVD

– Wafer Cracking, Edge Arcing, Thickness/Stress control

### 6 Secondary Reveal

Wafer Cracking

### 7 C4 Bumping

**8** 2<sup>nd</sup> Carrier Bonding & 1<sup>st</sup> Carrier De-bondding

**9** Chip Attach on Interposer

### **10** 2<sup>nd</sup> Carrier de-bonding

7

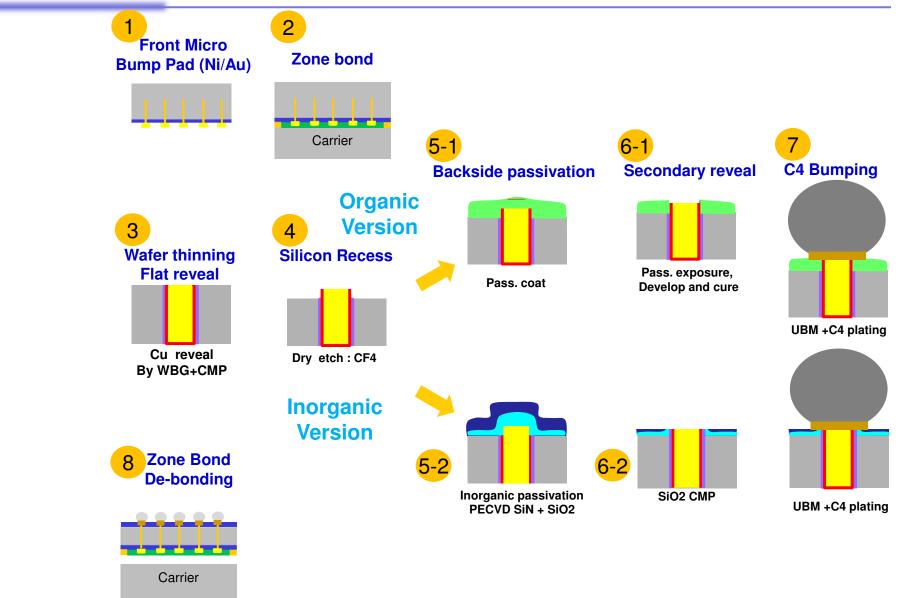

#### **TSV - Interposer M/BEOL Process**

#### © Copyright Amkor

### **1** Front Micro Bump Pad

- Ni/Au Pad : Thickness, IMC embrittlement

### 2 Zone Bond

TTV Control

### **3** Flat Reveal Wafer Thinning + CMP

- Wafer Cracking, Cu smearing

### 4 Silicon Recess – Dry Etch (CF4)

- Cu corrosion, Etch rate variance, Slow Etch, Contaminate

### **5** Passivation – Organic pass. coating, PECVD

– Wafer Cracking, Edge Arcing, Thickness/Stress control

### 6 Secondary Reveal

– Wafer Cracking

### **7** C4 Bumping

### 8 Carrier De-bondding

- Wafer Breakage

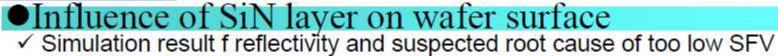

## 1. FS NiAu – CoC Evaluation

### CoC Evaluation on E-lytic Ni/Au

- AOI inspection

- Ni/Au thickness measurements

- Auger analysis for surface condition

- Wafer bonding

- Simulated backside thermal processes

- Debond

- AOI Pad inspection for FM

- Singulate

- Mass Reflow

- TC Bond

- "FA X-section, EDX line scan, EDX area mapping"

- TC CoC

- FA

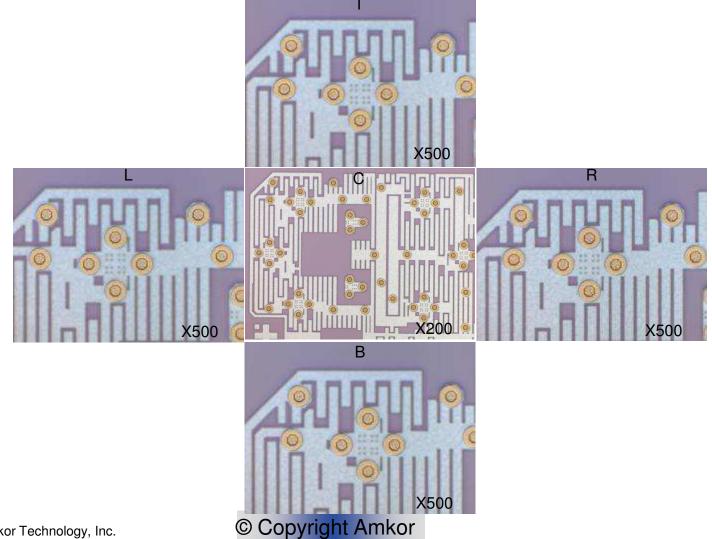

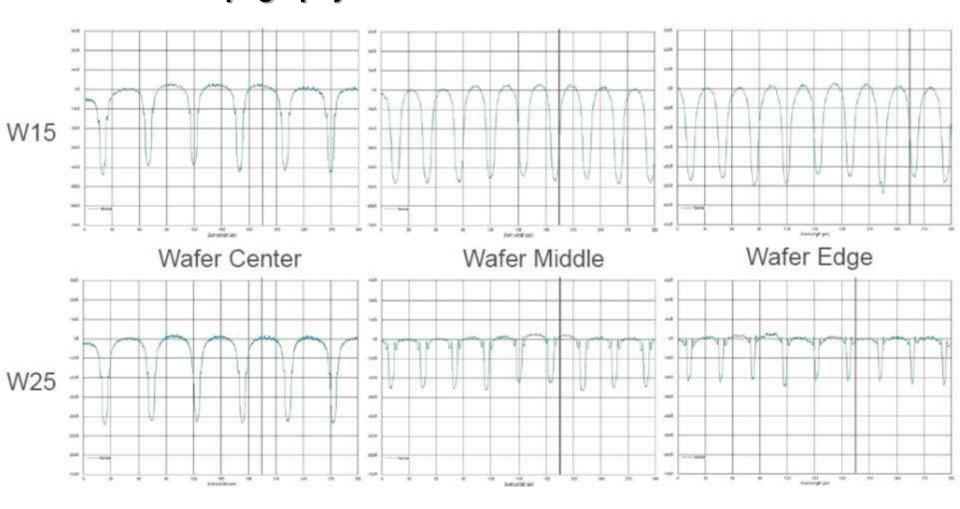

#### **Images - Post UBM Etch Process**

- There are no abnormalities

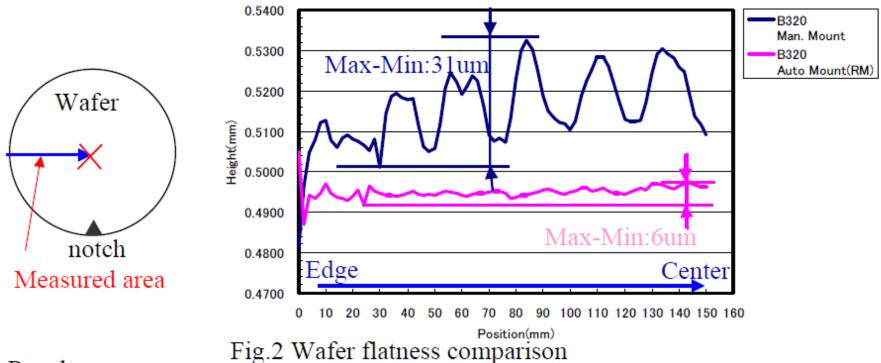

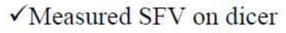

## Process validation

- For edge trimming to reduce chipping.

- Optimization of wafer bonding to minimize thickness variance of temporary bonding adhesive.

- Minimizing wafer crack on debonding process.

- EAR optimization

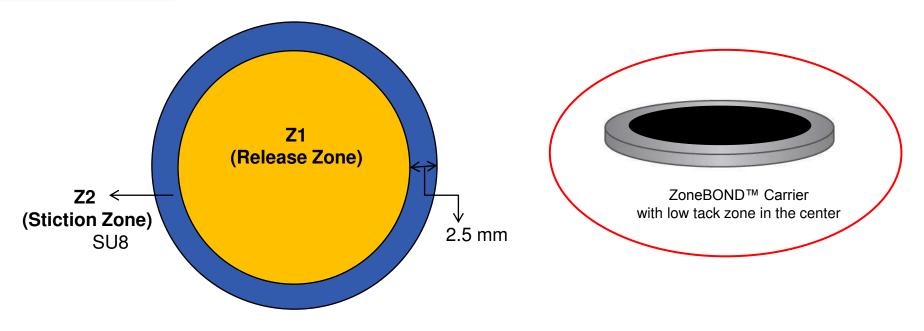

## **Overview of ZoneBOND carrier wafer**

- Silane+FC40 (Z1, release zone)

- This is anti-sticky zone.

- Edge zone (Z2, stiction zone)

- Edge zone width is approximately 2.5mm.

- Minimum edge zone width is 1.5 mm.

- SU8 is used as the edge zone mask.

#### Drop test to Acetone

- We can confirm that Zone treated carrier wafer(Z1) to acetone.

- Z1 is non stick. The reaction of the material to the wafer is just to make the material chemically bond to the wafer that as a "Silanol condensation reaction". Once it reacts with the surface, the single molecule layer that's permanently attached to the carrier acts as a poly tetrafluoroethylene(PTFE) or "Teflon like" coating on the wafer.

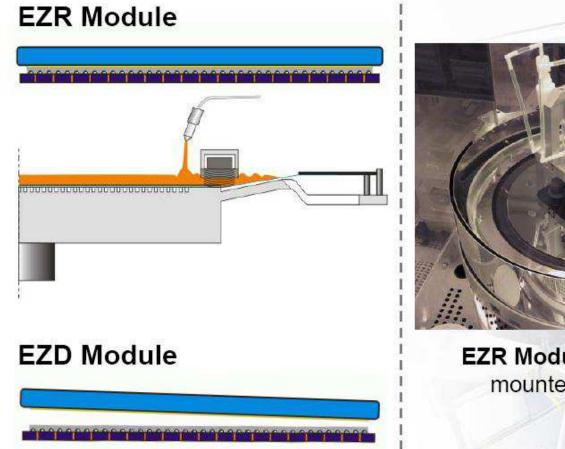

## **ZoneBOND De-bonding**

Edge Zone Release with EZR & EZD module

EZR Module: 300mm wafer mounted on film frame

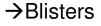

## Failures & Problems Related with ZoneBOND De-Bonding

→Delamination

$\rightarrow$ Adhesive squeeze out

$\rightarrow$ Crack at edge zone

→Crack

→Wafer shift

© 2012 Amkor Technology, Inc.

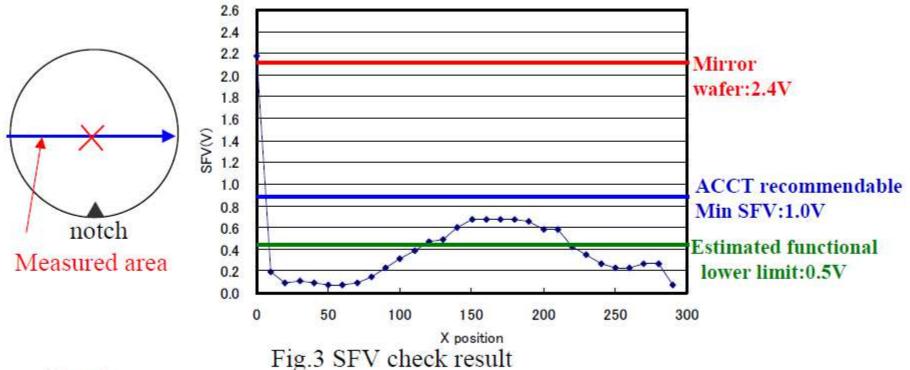

|                   | Thermal                    | Zone                    | Laser               | Chemical | Wedge     |

|-------------------|----------------------------|-------------------------|---------------------|----------|-----------|

| Machine           | EVG, TEL, SUSS             | EVG, SUSS               | TAZMO, Yushin, SUSS | ТОК      | SUSS      |

| Material          | BSI, ShinEtsu,<br>Sumitomo | BSI, ShinEtsu, Sumitomo | 3M                  | ТОК      | TMAT, Dow |

| Machine<br>price  | Middle                     | High                    | Middle              | Middle   | High      |

| Material<br>price |                            | High                    | Middle              | High     | Middle    |

| тти               | Good                       | Normal                  | Good                | Normal   | Normal    |

| UPH               | Middle                     | Low                     | High                | Low      | High      |

The miracles of science HD-3007

SUSS XBC300

brewer ZoneBOND™

© 2012 Amkor Technology, Inc.

## Advantage & Disadvantage of Various Methods

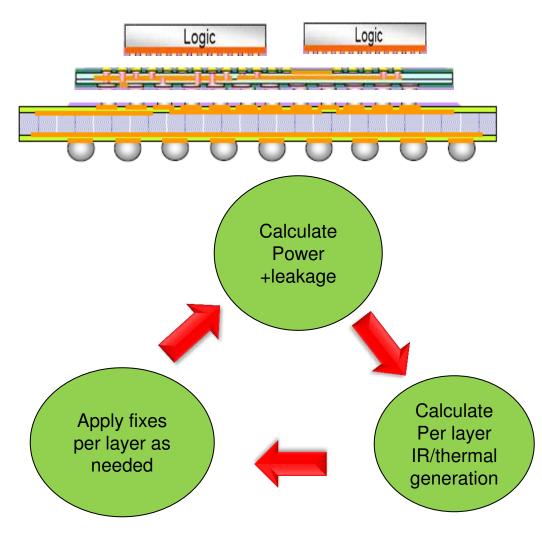

|                 |                  | POR                                                                                                                | NEW                                                                                                                        |                                                                                                                          |                                                                                                                           |                                                                                                                             |