qctconnect.com

UALCOMM CDMA Technologies QUALCOMM CONFIDENTIAL AND PROPRIETARY

# **Roadmap for Design and EDA** Infrastructure for 3D Products

| Riko Radojcic                      | HotChips 2012 |

|------------------------------------|---------------|

| Qualcomm                           | Cupertino, CA |

| E-mail : <u>rikor@qualcomm.com</u> | Aug 2012      |

| Tel : 1 858 651 7235               |               |

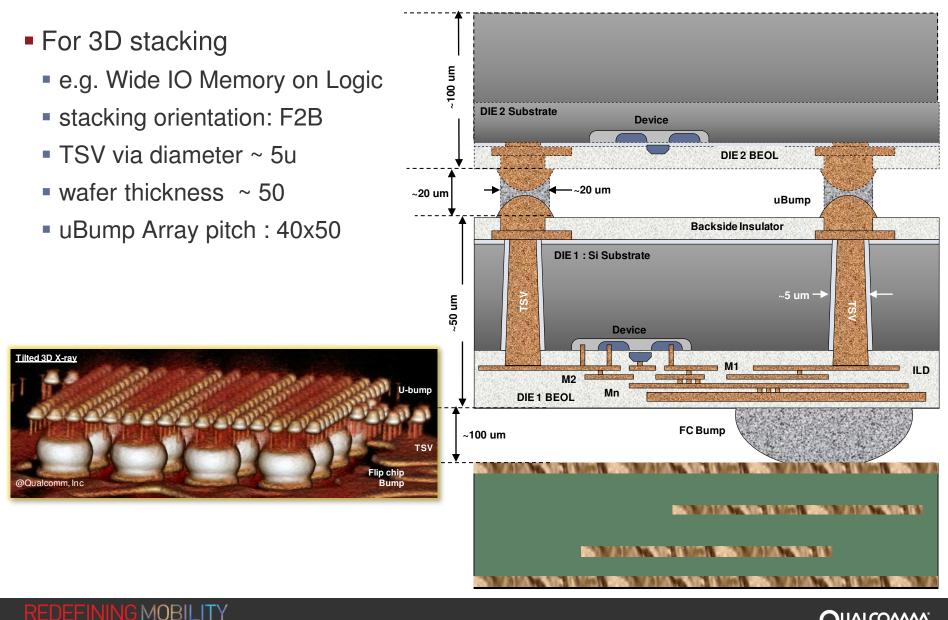

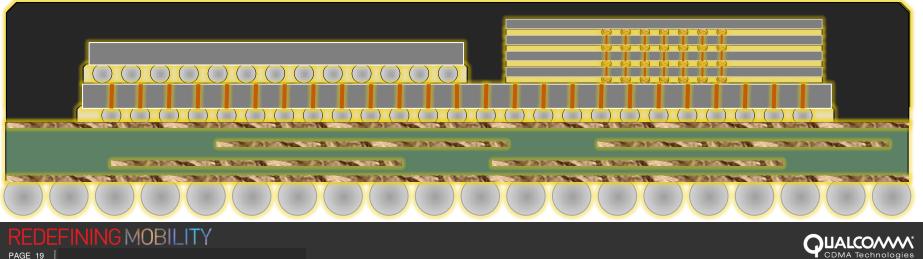

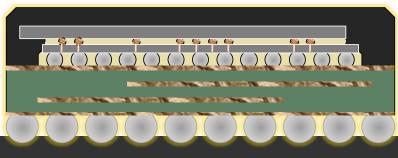

### Some of the Typical 3D Options

| 2.5D                            | Side by side die stacked<br>on a passive <u>interposer</u><br>that includes TSVs |  |

|---------------------------------|----------------------------------------------------------------------------------|--|

| <b>3D</b><br>Memory             | Multiple DRAM die<br>stacked standalone or on<br>an active interposer            |  |

| <b>3D</b><br>Memory<br>on Logic | One or More DRAM die<br>stacked directly on logic<br>die ( <u>M-0-L</u> )        |  |

| <b>3D</b><br>Logic on<br>Logic  | Multiple logic die stacked<br>on top of each other<br>( <u>L-o-L</u> )           |  |

| <b>3D +</b><br>Interposer       | Mix of side by side and<br>stacked schemes with a<br>passive or active interpsr  |  |

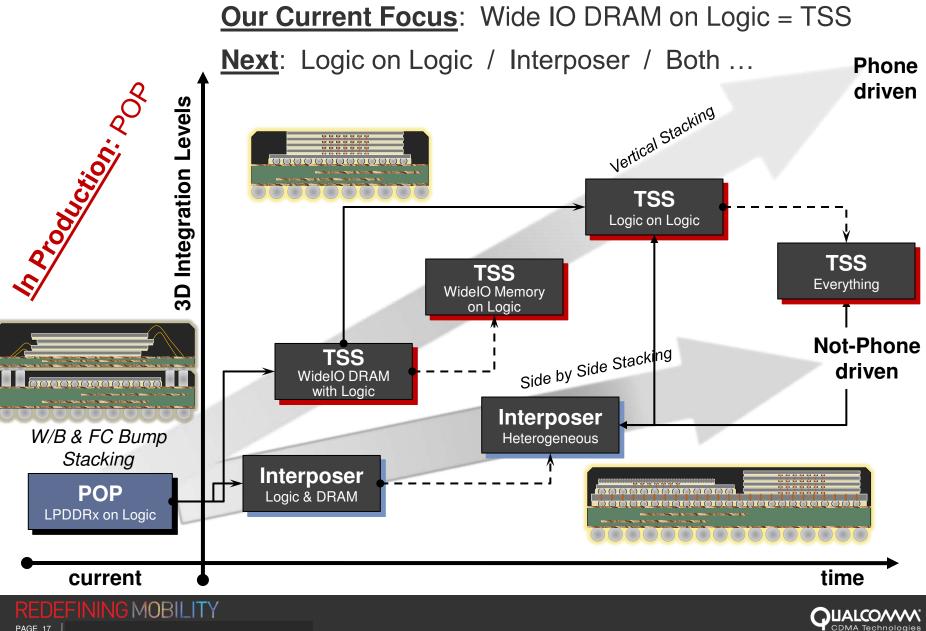

### **Evolving to "Mainstream" 3D Technologies**

PAGE 3

### Snapshot of Intrinsic Technology Status

|         | Was (common concern a few years ago)                      | ls (our take)                               |

|---------|-----------------------------------------------------------|---------------------------------------------|

| Process | High aspect ratio (10:1) 5/50 TSV process                 | ✓                                           |

|         | Thinning & Backside wafer processing                      | ✓                                           |

|         | Microbump and Joining                                     | ✓                                           |

|         | Integration & Stacking                                    | $\checkmark$                                |

|         | Intrinsic Reliability Assessment                          | 🔹 in flight                                 |

|         | Standards (JEDEC, SEMI, Sematech, 3D EC,)                 | 🔹 in flight                                 |

|         | EDA tools (for "2D-like" Memory-on-Logic design)          |                                             |

| Design  | Design Enablement (for "2D-like" Memory-on-Logic design)  | $\checkmark$                                |

| Design  | Testability (for "2D-like" Memory-on-Logic design)        | ✓                                           |

| (M-o-L) | Variability (Corner for "2D-like" Memory-on-Logic design) | $\checkmark$                                |

|         | Standards (JEDEC, Si2, IEEE)                              | 🔹 in flight                                 |

| Product | System Level Value Proposition                            | $\checkmark$                                |

|         | Thermal Modeling & Design for Thermal                     | 🔹 in flight                                 |

|         | Stress Modeling & Design for Stress                       | ✓                                           |

|         | SI modeling & Design for Parametric Yield                 | ✓ in flight                                 |

|         | Cost Structure & Business Models                          | ● <sup>™</sup> TBD                          |

|         | Yield and Yield Learning                                  | ● <sup>™</sup> TBD                          |

|         | Volume Manufacturing Ramp                                 | <b>●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●●</b> |

**REDEFINING MOBILITY**

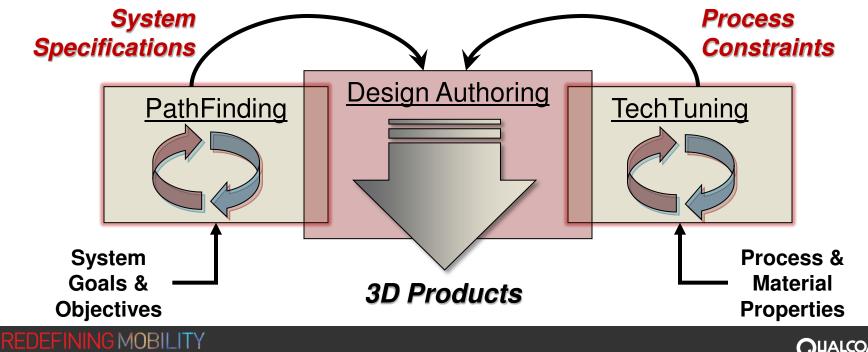

### **Eco-System for 3D Design**

- Segment Design Eco-System into 3 Buckets to Address 3 Key Challenges

- Design Authoring actual chip design

- Implement Design via (mostly) Traditional 2D Chip Design Flow (RTL2GDS))

- Output GDS

- PathFinding design/technology concept exploration

- Manage Choices via Cheap, Quick & Dirty Concept Design

- Output Clean Specs

- TechTuning physical space exploration

- *Manage Interactions* via Cheap, Electrical, Thermal & Mechanical Chip Simulation

- Output Clean Constraints

CDMA Technologies

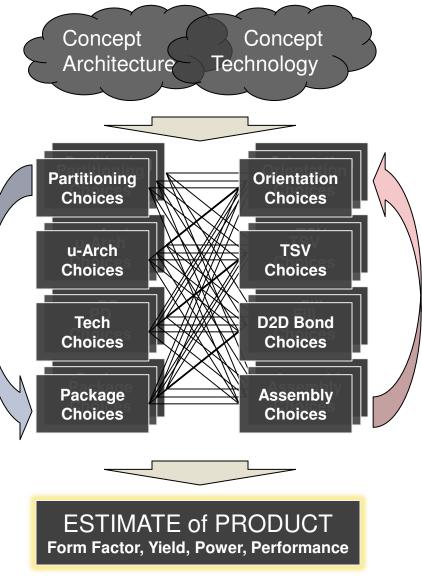

## PathFinding: Why & What ?

- Managing Choices ....

- Want to optimize product attributes

- Cost, power, performance, engineering ...

- Need to Co-Optimize Process & Design

- Winning 3D Product will Be Architected specifically to Leverage 3D Technology

- Selection of choices is Product Specific

- In General: <u>Need Spatial Awareness</u>

- Quick and flexible

- Hi fidelity vis-a-vis accuracy

- For 3D : <u>Also Need Heterogeneity</u>

- Multiple stacking styles & orientations

- Multiple tech files

- Multiple levels of hierarchy

- Multiple resource constraints

- <u>Structured</u> Methodology.

- Past experience not applicable

- Opportunity for paradigm shifts

- Not tied to Legacy design

- Process-Design-Package co-optimization

Details :3D System Integration, Springer 2011

imec

CDMA Technologies

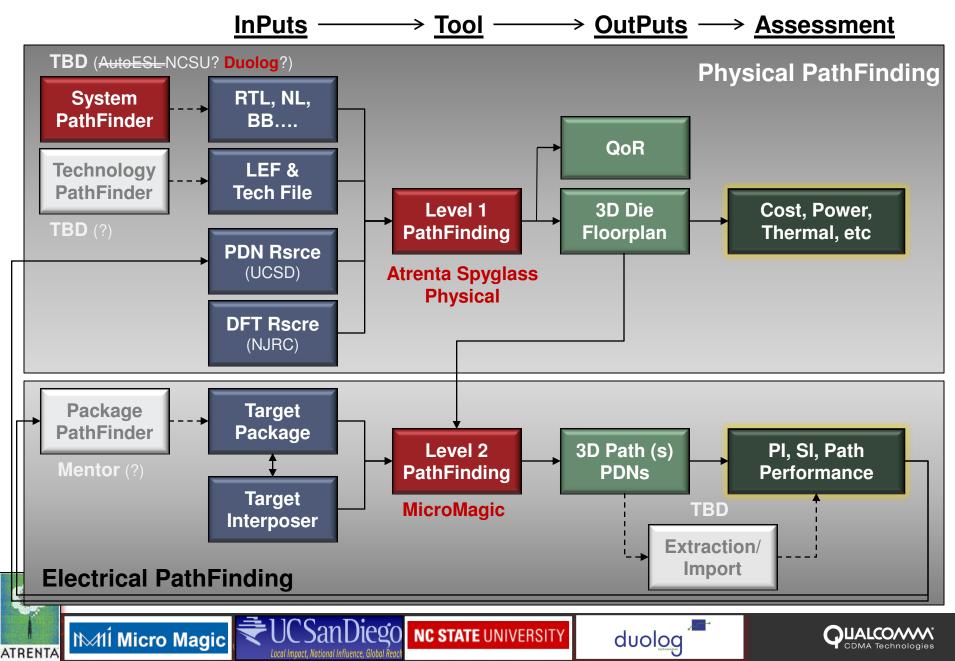

## **3D PathFinding : Current View**

## **PathFinding**

- Level 1 (Atrenta): think

- RTL & Netlists

- Block Level Schematics

- Partitions

- Block assignments

- T2T connectivity

- Global Routing

- Floorplans

- Level 2 (MicroMagic): think

- Transistor Level Schematics

m4 v34 m3 v23 m2 v12

ml ct mmi15jactive poly ndif pdif

mmi15|othe nw od2 n3v

pplus

- T2T layout

- SPICE Netlist

- Waveforms

- Polygons

-18.60pS, 1.22

**CDMA** Technologies

## TechTuning: Why & What ?

- Managing Interactions

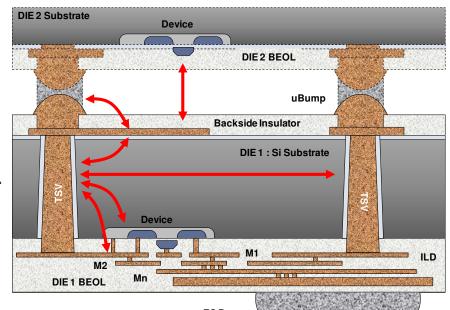

- Intimate Proximity and Coupling Between Die

- In Electrical, Thermal & Mechanical Domains

- Electrical Domain Interactions

- Within Die Interactions with New Features

Substrate noise, Coupling etc..

- Die to Die interactions (SI, PDN, PI...)

- Thermal Domain Interactions

- Within a Die & Die to Die

- Need Thermal Rules & Guidelines

- Design Specific & Technology Specific

- Need a methodology to plug into std design flow

- Stress Domain Interactions

- Within a Die & Die to Die

- Need Stress Rules & Guidelines

- Design Specific & Technology Specific

- $-\ensuremath{\,\text{Need}}$  a methodology to plug into std design flow

Details :3D IC Stacking Technology, McGraw Hill 2011

DMA Technologies

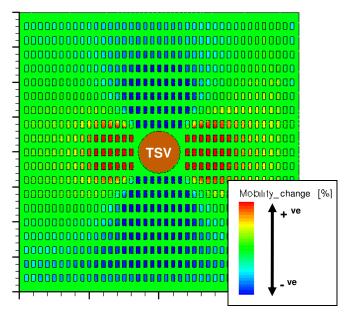

## **3D Electrical Interactions**

- Many Possible Interactions

- Die to Die close proximity

- Within a Die new features

- New Geometries: not just simply planar

- uBump to BRDL

- TSV to BRDL

- TSV to TSV

- TSV to M1

FC Bump

- New Features: not just conductor or insulator

- MOS nature of TSV & Semiconductor nature of Si

- e.g. Substrate Noise Coupling: TSV to Device

- vs. substrate thickness

- vs. Doping Profile in the Si substrate

- vs. TSV to Device Separation

- vs. Substrate Tap & Guard Ring Configuration

- etc...

cādence

### Need true 3D Chip Level Extraction & Coupling Analyses

Or a restricted layout with pre-characterized macro model

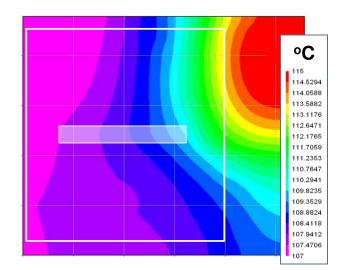

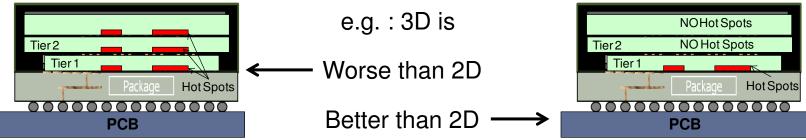

### Thermal Challenges => a Fundamental Constraint

- Thermal: a Global (=System Level) & Local (=Component Level) Challenge

- Global Concern : must manage skin temperature and overall system power

- Local Concern : must manage hot spots, junction temperature, and power density

- Compounding Factor: all advanced systems use some form of Thermal Mitigation

- Thermal is not a 3D-only Challenge

- A Problem that has to be addressed with 2D Components as well...

- At Architecture, Design, Floorplanning, Packaging, Application, Software ...

- Could be a 3D Opportunity ?

### Need a System-Chip Co-Design Methodology & Tools

Faster and More Flexible than the traditional CFD / FEA methodologies

DOCEA

- Compatible with cross company handshake (a la TDP practice in PC domain)

- Compatible with fuzzy PathFinding-like forward looking inputs

- Compatible with different system level 'knobs'

- Compatible with different chip level 'knobs'

cādence

ritable analysis

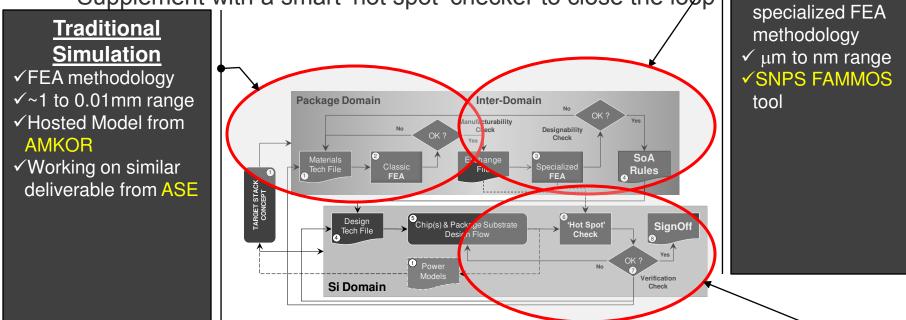

## **Implementation of a TechTuning Flow for Stress**

- Interface to actual Design Authoring : <u>Rules</u> now

- maybe in-flow model based simulation later..

- Based on 'off-line' simulations using specialized tools

- Define a 'Safe Operating Area' => a set of rules

- Supplement with a smart 'hot spot' checker to close the loop

#### "Hot Spot" Checker

- Validation that bits and pieces fit & SIGN OFF the design

- Must interface to design environment : I/P : GDS2 , LEF, DEF  $\ldots$

- May have to be COMPACT MODEL Based (read the whole design and include all effects)

- Working with MENT

**Specialized**

Simulation

✓ Submodeling &

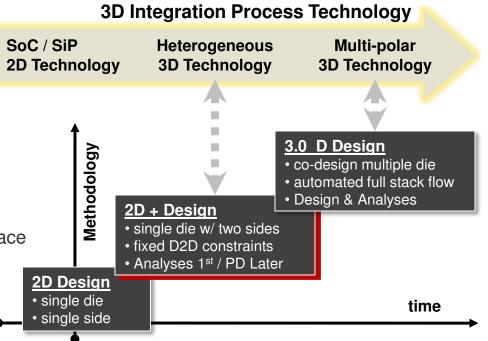

## Managing Costs : What Does It Mean for TSS Design?

- Expect Gradual and Graceful Evolution

- Process and Design together / in synch

- Significant investment in the existing flow

- Will be Applications Driven

- Now : Heterogeneous Stacking

- e.g. Memory (or Std Analog) on logic

- Design Methodology Requirements

- Partitioning : by die types w/ spec interface

- Syntheses e-at-a-time

- Floorplannin constraint from the other die

- Physical Design : partial 2-sided die (maybe)

- Physical Verification: 1-die-at-a-time + interface

- Analyses : whole stack (eg PDN)

- Next : Integrated Stack Designs

- e.g. Logic-on-Logic or Interposers

- Design Methodology Requirements

- Integrated PD Co-Design w Interposer & Substrate

- Design Constraint Methodology

- Design Authoring including the Package

- Manufacturability (aka TechTuning)

## Evolving from 2D Design

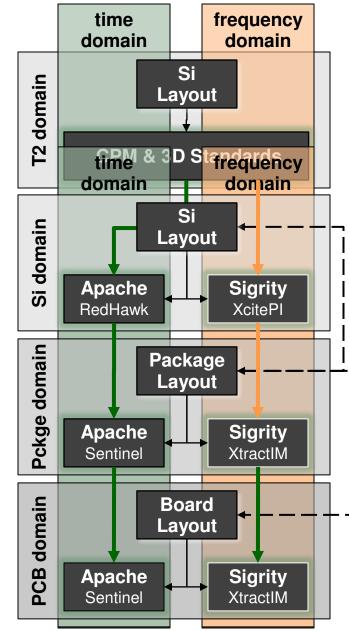

## **3D PDN Design Flow**

- 2D Ref Flow

- Sign off in time domain (Apache)

- Analyses in frequency domain (Sigrity)

- 3D PDN Flow Approach

- Take as much as possible from ref flow

- ✓ Similar approach as Si-Package-PCB Analyses

- Extract each tier separately

- Model as an integrated stack

- Upgraded tools to understand new features

- TSV, uBump, BRDL, Tier n ...

- Current Status

**Apache**

- Demonstrated Tools & Flow

- Supporting development of standard Compact PDN Models and associated 3D Design Exchange Format Standards

SIGRIT

### **Inventory of Current Core Design Technologies**

|                                                        | PathFinding                                                                                         | TechTuning                                                                                                                                                  | Design Authoring                                                                                                                               |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Things<br>We Do<br>Have                                | <ul> <li>✓ 3D Floorplanner</li> <li>✓ 3D Net generator</li> <li>✓ PDN resource estimator</li> </ul> | <ul> <li>✓ Package Stress simulator</li> <li>✓ Feature Stress simulator</li> <li>✓ Reference Thermal sim.</li> </ul>                                        | <ul> <li>✓ 2D design flow &amp; tools</li> <li>✓ Timing with a fixed</li> <li>TSV/uBump layout</li> <li>✓ 3D aware PI / SI analyses</li> </ul> |

| Things<br>We are<br>Working                            | <ul> <li>Package PathFinder</li> <li>System PathFinder</li> <li>Standard 3D design</li> </ul>       | <ul> <li>Chip Level Stress Sim</li> <li>Chip thermal floorplanner</li> <li>Standard 3D design</li> </ul>                                                    | <ul> <li>M-o-L product design</li> <li>3D Variability Flow</li> <li>Standard 3D design</li> </ul>                                              |

| On                                                     | exchange formats                                                                                    | exchange format & PDK                                                                                                                                       | exchange formats                                                                                                                               |

| Things<br>we do<br>NOT<br>Have<br>(and wish<br>we did) | Technology PathFinder                                                                               | <ul> <li>3D in flow substrate<br/>coupling analyse</li> <li>Fully supported<br/>TechTuning "PDK'</li> <li>System component<br/>thermal co-design</li> </ul> | <ul> <li>TBD Logic on Logic</li> <li>TBD Interposer</li> <li>TBD 3D Extraction</li> <li>TBD 3D ++ (see below)</li> </ul>                       |

■ We don't have Everything – but we do have much more than Nothing ☺ !!

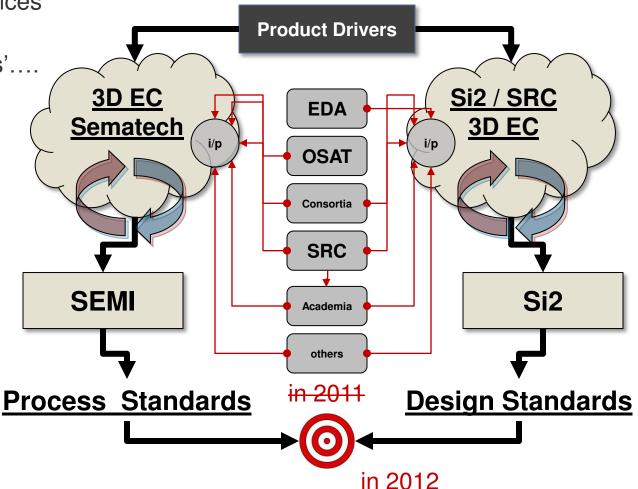

## Standards : a Lubricant for the Supply Chain

### Leverage Existing Standards Bodies

- Established balloting, adoption and management practices

- But formal and hence need 'mature proposals'....

### Process Standards

- 3D Enablement Center

- Sematech

- SEMI ...

- Design Standards

- Si2

- 3D EC / SRC

- IEEE

- JEDEC...

- Encourage Participation by the Industry – esp EDA

### 2.5D / 3D Stacking Roadmap

PAGE 17

### **Design Environment for Memory-on-Logic**

| Status          | Arena                            | Item                                                                                                                                                                                     |

|-----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Design                           | <ul> <li>✓ 2D design flow &amp; tools</li> <li>+ quasi-manual placement of T2T / TSV array</li> <li>+ custom T2T buffer design &amp; incremental rules to manage interactions</li> </ul> |

| Have            | Timing                           | <ul> <li>✓ 2.5D analyses flow &amp; tools</li> <li>+ compound 'lumped' TSV delay model</li> </ul>                                                                                        |

|                 | PI                               | <ul> <li>✓ 2D analyses flow and tools</li> <li>+ extended hierarchy + recognition of new features</li> </ul>                                                                             |

|                 | SI & Variability                 | ✓ 'Off Line' analyses to produce set of 'keep out' rules                                                                                                                                 |

| In Flight       | 'In Line' Rule<br>Checkers       | <ul> <li>✓ Chip Level Stress Simulator – for 'stress Hot Spots'</li> <li>✓ Chip Level Thermal Floorplanner</li> <li>✓ Chip Level SI Simulator</li> </ul>                                 |

|                 | Integration w/<br>Commercial Die | ✓3D Design Exchange Formats                                                                                                                                                              |

| e to            | SI Analyses                      | In Flow SI analyses – on line and in product flow                                                                                                                                        |

| Like to<br>Have | TechTuning & PathFinding         | <ul> <li>Fully supported TechTuning "PDK'</li> <li>System-Component thermal co-design</li> </ul>                                                                                         |

**REDEFINING MOBILITY**

### **Design Environment for Interposers**

| Status       | Arena            | Item                                                                 |

|--------------|------------------|----------------------------------------------------------------------|

| Have         | Design           | <ul> <li>✓ 2D Layout tools</li> <li>✓ 2D Extraction Tools</li> </ul> |

| e ve         | Extraction       | The straction inc. TSV , routing and FRDL/BRDL                       |

| Need to Have | Signal Integrity | Integrated SI tools inc floating substrate and 3D features           |

| eed t        | Power Integrity  | Integrated PI analyses tools & flow                                  |

| Ž            | DFT / Test       | Integrated Double Sided Passive Floating Substrate                   |

|              | PathFinding      | Architectural Trade Off Analyses for Value Proposition               |

## **Design Environment for Logic on Logic**

| Status    | Arena             | Item                                                         |

|-----------|-------------------|--------------------------------------------------------------|

| Have      | Design            | ✓ 2D Flow for One Single Sided Die & Technology at a time    |

| На        | PathFinding       | ✓ 3D Physical PathFinding Flow for finding Value Proposition |

|           | Floorplan         | 3D with optimization across multiple tiers (technologies)    |

|           | Utility Insertion | ● 3D tools for global utilities – eg NoC, Clock, DFT         |

|           | Extraction        | ● 3D Extraction inc. TSV , routing and FRDL/BRDL             |

| ave       | Timing            | across multiple tiers, technologies, libraries               |

| Must Have | Power Integrity   | Integrated PI analyses tools & flow                          |

| Mus       | Signal Integrity  | in flow SI analyses tools inc 3D features                    |

|           | DFT / Test        | Optimized DFT overhead for pre-stack test                    |

|           | Verification      | ● 3D Physical Verification, LVS, etc across multiple tiers   |

|           | etc               | dependent on the actual stack partition                      |

**REDEFINING MOBILITY**

qctconnect.com

**UALCOMM**

CDMA Technologies

QUALCOMM CONFIDENTIAL AND PROPRIETARY

### REDEFINING MOBILITY QUALOW