# The Maven Vector-Thread Architecture

<sup>1</sup>Parallel Computing Laboratory, UC Berkeley <sup>2</sup>Computer Systems Laboratory, Cornell University

# **Motivation**

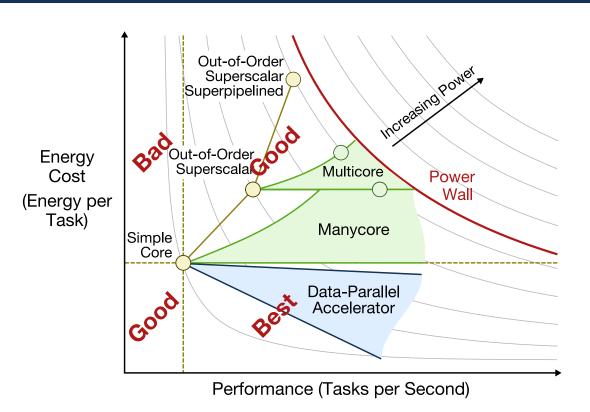

Future manycore processors be energy-constrained, and thus the primary metric for evaluating these architectures will be their energy-efficiency. In this work, we investigate architectural and microarchitectural mechanisms which enable a wider array of applications to be mapped to energy-efficient vector units.

# **Architectural Patterns**

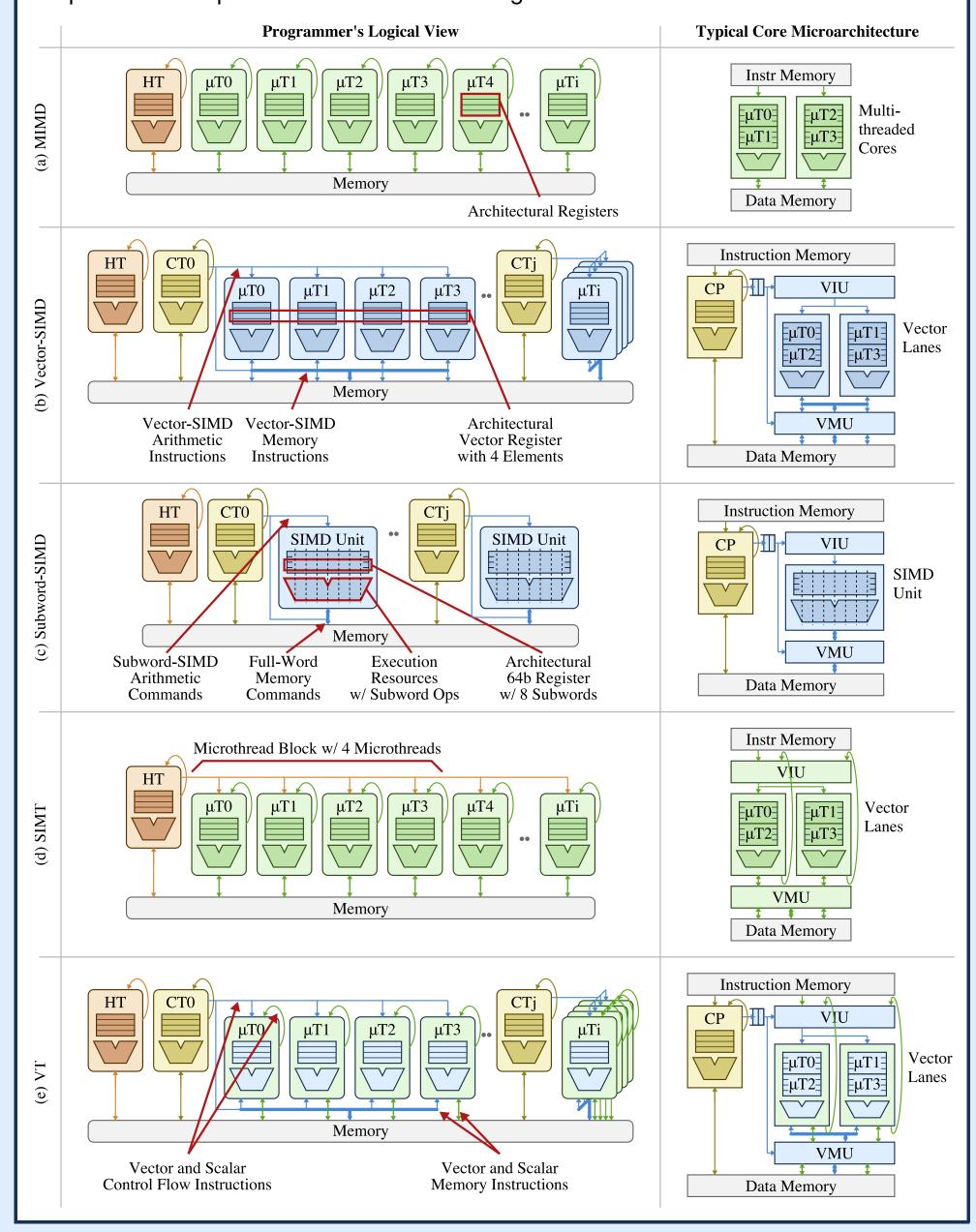

Three different architectural patterns (excluding subword-SIMD and SIMT) were evaluated in terms of their performance, energy efficiency and area. Maven is a new vector-thread architecture, which is based on a vector-SIMD architecture, adds minimal hardware to support irregular DLP well, and is considerably simpler to implement than previous vector-thread designs.

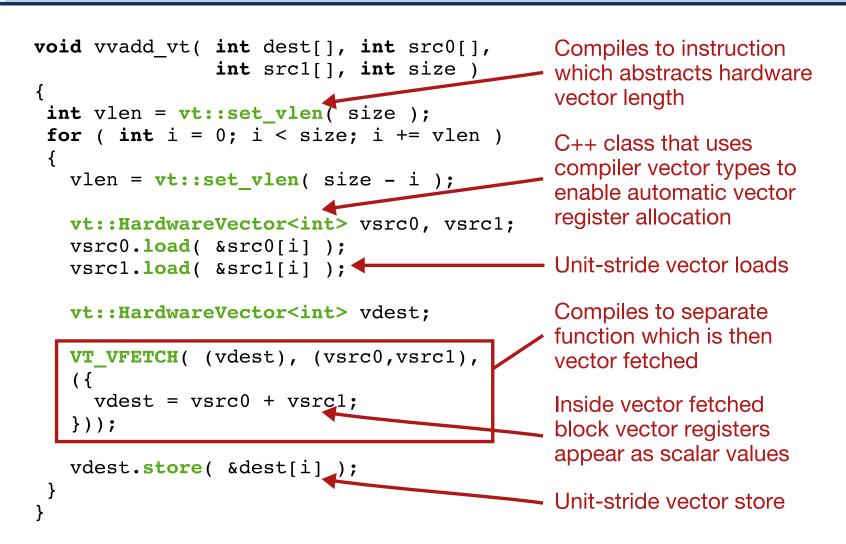

# **Maven Programming Methodology**

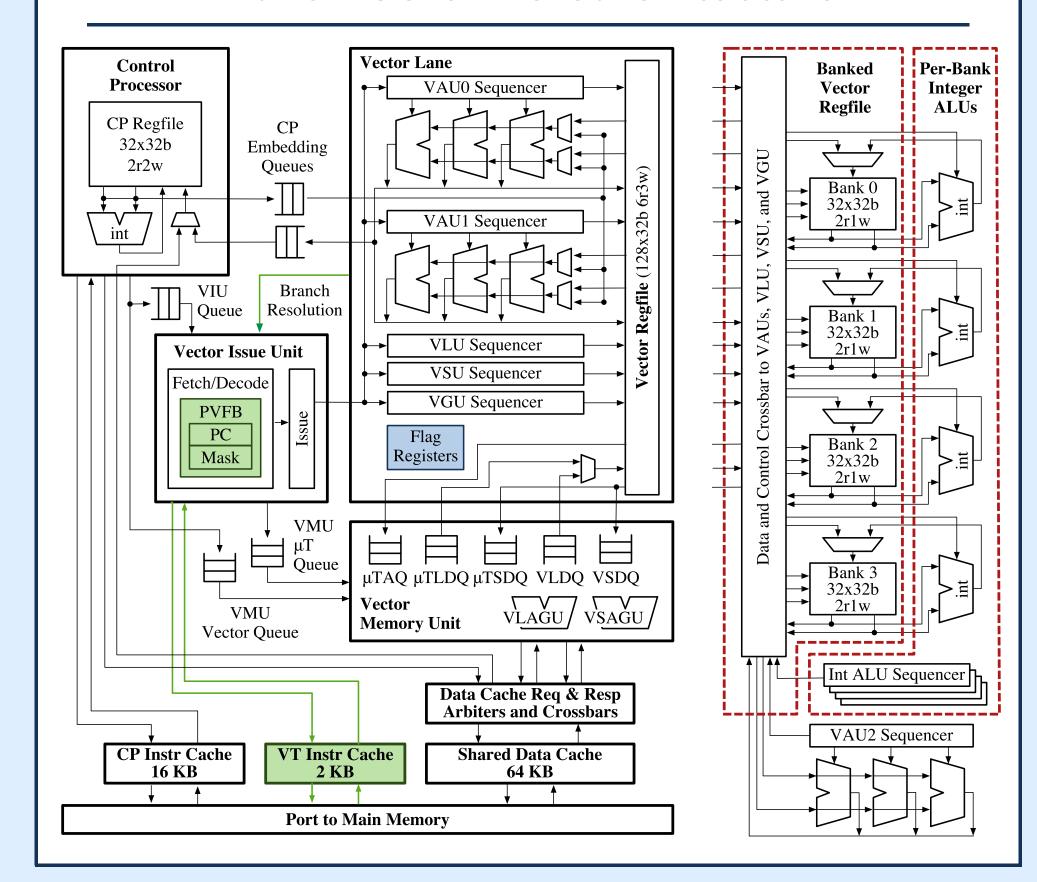

## **Maven Tile Microarchitecture**

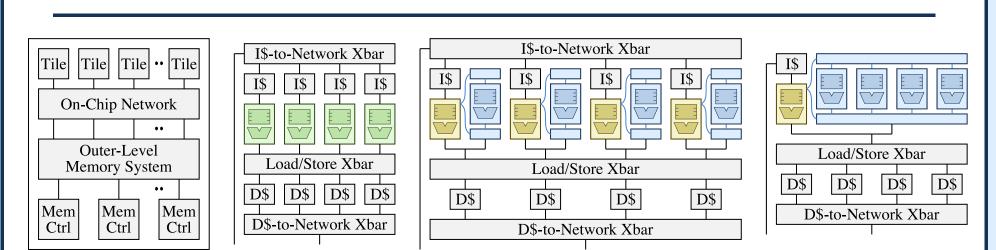

We focus on comparing the various architectural design patterns with respect to a single data-parallel tile. Example tiles are a MIMD tile, a vector tile with four single-lane cores, or one four-lane core. To manage complexity of many design points, we developed a library of parameterized synthesizable RTL components.

## **Tile Configurations**

#### **Maven Core Microarchitecture**

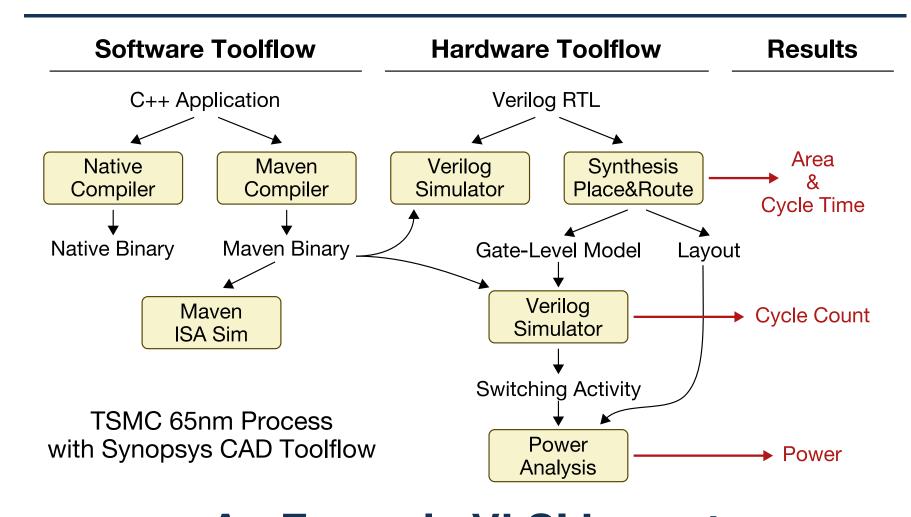

# **Evaluation Framework**

**Toolflow**

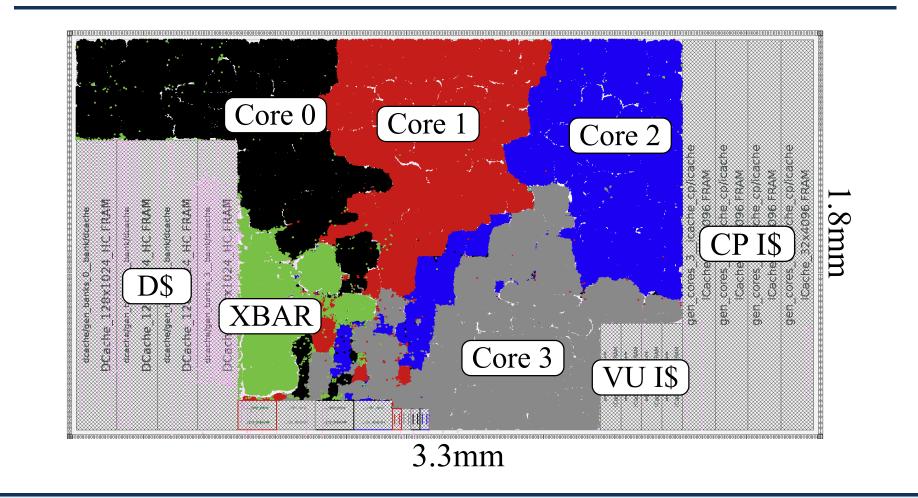

# **An Example VLSI Layout**

## **Evaluation Results**

6

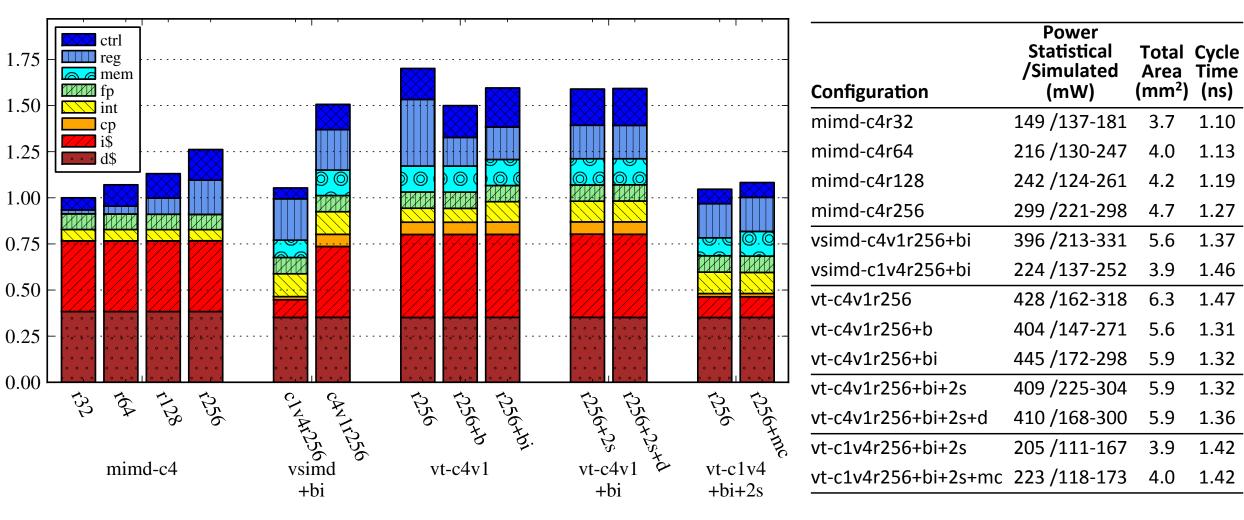

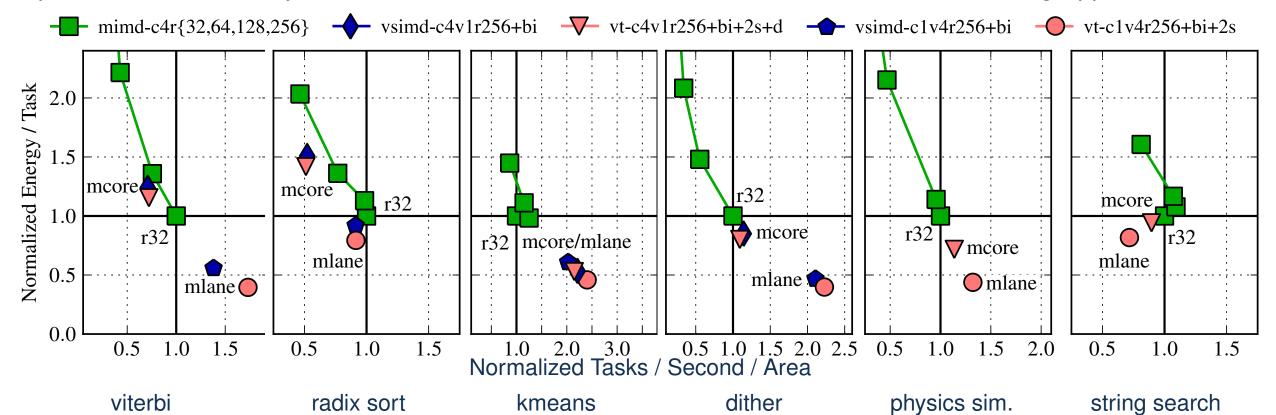

We first compare tile configurations based on their cycle time and area before exploring the impact of various microarchitectural optimizations. We then compare implementation efficiency and performance of the Maven VT pattern against the MIMD, and vector-SIMD patterns for the six application kernel.

# **Area & Cycle Time**

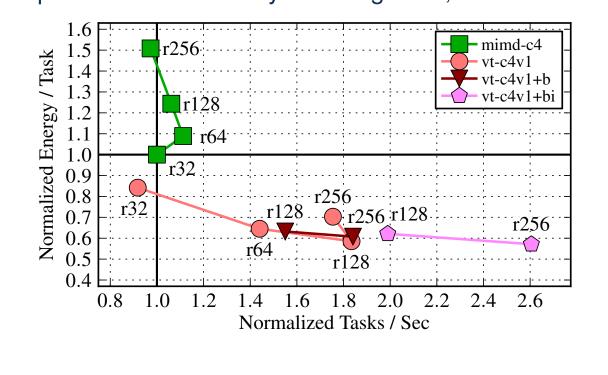

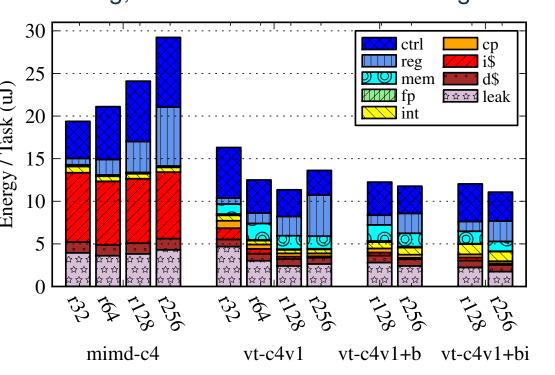

# Performance and Energy Efficiency

Impact of Additional Physical Registers, Intra-Lane Regfile Banking, and Additional Per-Bank Integer ALUs

vec ld/st

Impact of Density-Time Execution and Stack-Based Convergence Schemes / Impact of Memory Coalescing

Implementation Efficiency and Performance for MIMD, vector-SIMD, and VT Patterns Running Application Kernels

### Conclusions

- The Maven vector-thread architecture is more area and energy efficient than MIMD architectures on regular DLP and (surprisingly) on irregular DLP

- 2. The Maven vector-thread architecture is a promising alternative to traditional vector-SIMD architectures, providing greater efficiency and easier programmability

- 3. Using real RTL implementations and a standard ASIC toolflow is necessary to compare energy-optimized future architectures

For more details, see our ISCA '11 paper below or use the QR code on the right with a barcode reader. "Exploring the Tradeoffs between Programmability and Efficiency in Data-Parallel Accelerators"

This work was supported in part by Microsoft (Award #024263) and Intel (Award #024894, equipment donations) funding and by matching funding from U.C. Discovery (Award #DIG07-10227). The authors acknowledge and thank Jiongjia Fang and Ji Kim for their help writing application kernels, Christopher Celio for his help writing Maven software and developing the vector-SIMD instruction set, and Hidetaka Aoki for his early feedback on the Maven microarchitecture.