# Fully Integrated Switched-Capacitor DC-DC Conversion

**Elad Alon**

In collaboration with Hanh-Phuc Le, Seth Sanders

Berkeley Wireless Research Center University of California, Berkeley

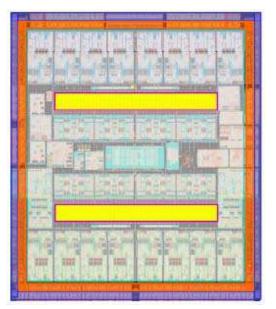

### **Multi-Core Chips Are Here**

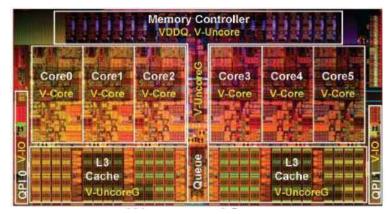

#### **Intel Westmere**

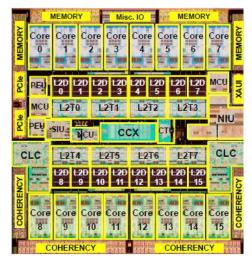

**IBM POWER7**

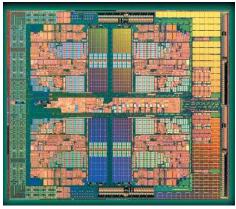

#### **AMD** Phenom

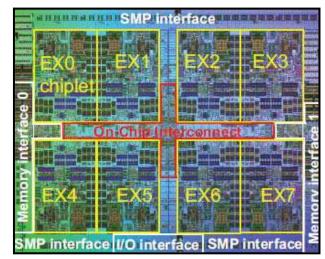

**Sun Rainbow Falls**

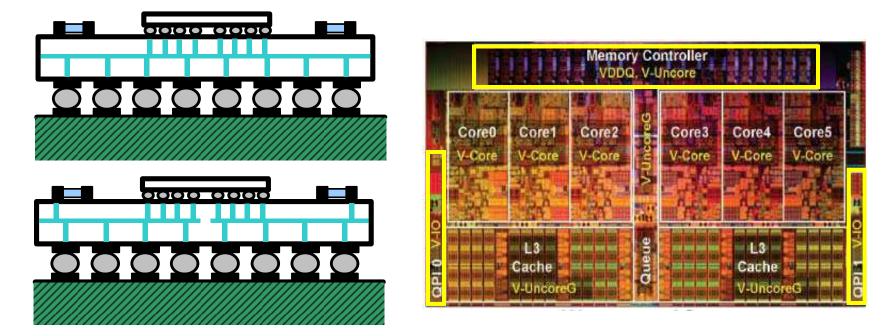

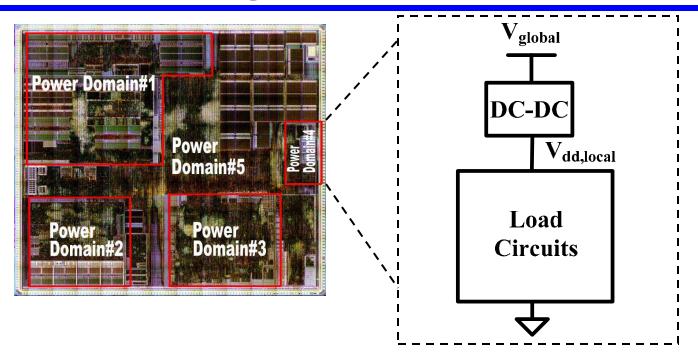

# **Multi-Supply Chips?**

- Separate supply voltages clearly desirable

- Power management, compensate variability, etc.

- But, true multi-supply adoption slow

- Except for power gating

Shin, ISSCC 2010

• Why not use multiple external converters?

# **Supply Impedance and Split Planes**

- Supply impedance requirement extremely low

- 1V, 100A part  $\rightarrow$  1m $\Omega$

- Split power planes bad for impedance

- Load and decap isolation

- Reason I/O's often placed on edges even with flip-chip

### **On-Die Voltage Conversion**

- Enables single, low-impedance global input voltage

- Key challenge: fully integrated DC-DC

- Energy storage must be integrated on-die too

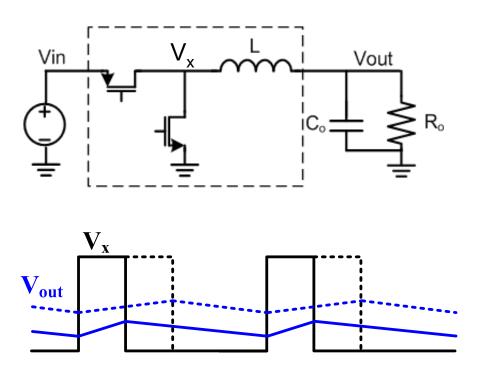

# **Switching Converter Options**

#### Inductor:

- Conversion ratio set by duty cycle

- Very popular for offchip converters

#### Capacitor:

- Conversion ratio set by topology

- Many perceived disadvantages

# So Why Switched-Capacitor (SC)?

- Key motivation: integration with <u>low cost</u>

- Dense, high-quality capacitance widely available

- (Development of on-die magnetics can be leveraged for SC converters too)

- Integrated SC design can mitigate perceived downsides

- Component count no longer critical

- What is achievable efficiency, power density?

8

### **Selected Previous Designs**

| Work                              | Breussegem, VLSI 09                          | Somasekhar, VLSI 09     |

|-----------------------------------|----------------------------------------------|-------------------------|

| Technology                        | 130nm Bulk                                   | 32nm Bulk               |

| Тороlоду                          | 2/1 step-up                                  | 2/1 step-up             |

| Interleaved Phases                | 16                                           | 32                      |

| Converter Area (mm <sup>2</sup> ) | 2.25                                         | 6.678x10 <sup>-3</sup>  |

| Power density @ η <sub>max</sub>  | 0.002 W/mm <sup>2</sup>                      | 1.123 W/mm <sup>2</sup> |

| Efficiency (η <sub>max</sub> )    | 82%                                          | 60%                     |

|                                   | EC_1FC_2EC_3FC_4<br>Cout<br>EC_5FC_6FC_7FC_8 | Pump 0-15 Pump 16-31    |

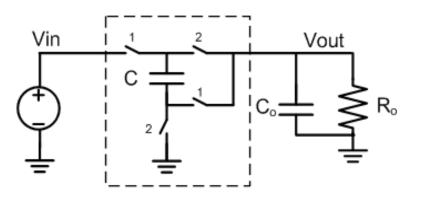

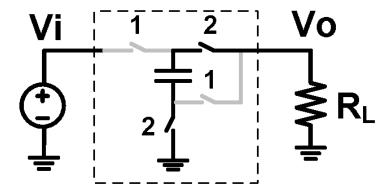

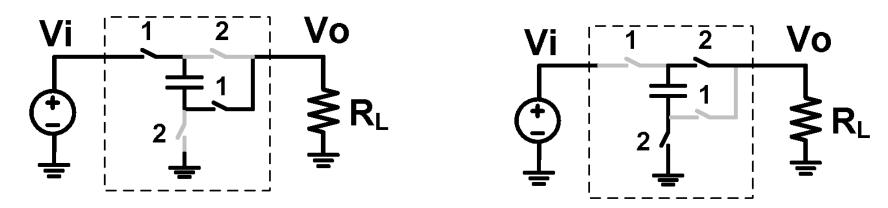

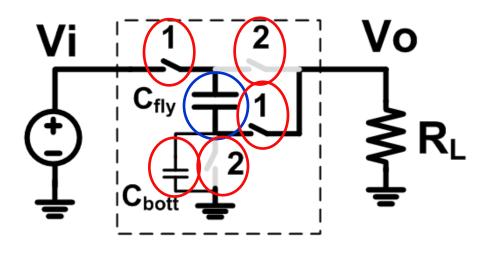

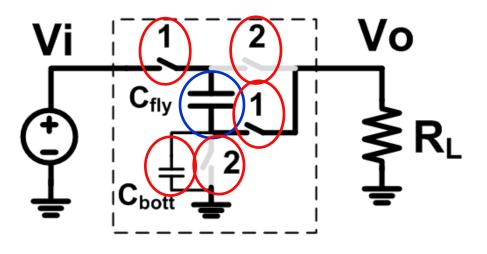

### **Review: SC Basics**

Phase 1:

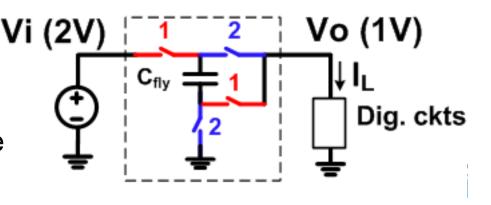

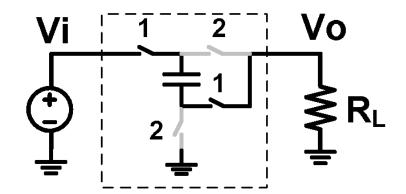

# **Switched Capacitor (SC) Basics**

Phase 1:

- Conversion ratio set by topology

- Works in other direction too

- Step-up: reverse V<sub>i</sub>, V<sub>o</sub>

## **SC Converter Loss Mechanisms**

- Intrinsic loss

- Fundamental to converter operation

- Switch/parasitic loss

- Non-idealities of the capacitor(s) and switches

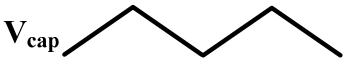

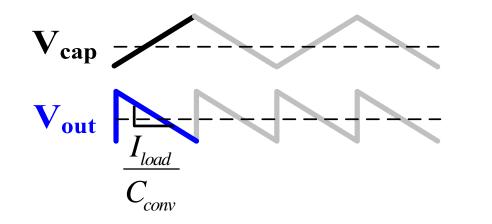

# SC Converter Loss with Digital Loads

- Gate delay depends on  $V_{dd}$ : • Performance set by  $V_{min}$ • SC converter effective output resistance (for  $V_{min}$ ):  $R_{eff,Csw} = \frac{1}{M_{conv,con}C_{conv}f_{sv}}$

- But, load also draws "extra" current when V<sub>dd</sub> > V<sub>min</sub>

- This power is wasted since it doesn't improve performance

- Ripple leads to extra loss: *I*

$$P_{Reff} = \frac{2 I_{load}^2}{M_{conv,cap} C_{conv} f_{sw}}$$

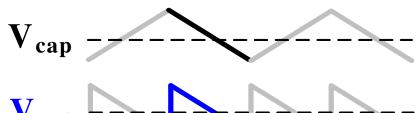

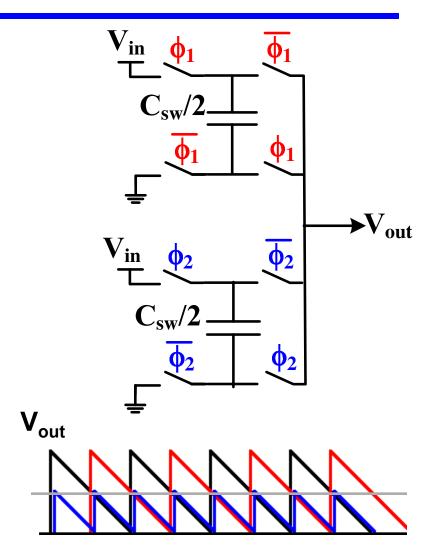

## Interleaving

- Good news: interleaving reduces ripple

- But leaves V<sub>min</sub> unchanged

- With N<sub>int</sub> interleaved converters:

$$P_{Reff} = \left(1 + \frac{1}{N_{int}}\right) \frac{I_{load}^2}{M_{conv,cap}C_{conv}f_{sw}}$$

Ripple minor for ~16+ way interleaving

D. Ma, "Robust Multiple-Phase Switched-Capacitor DC-DC with Digital Interleaving Regulation Scheme," *ISLPED* 2006.

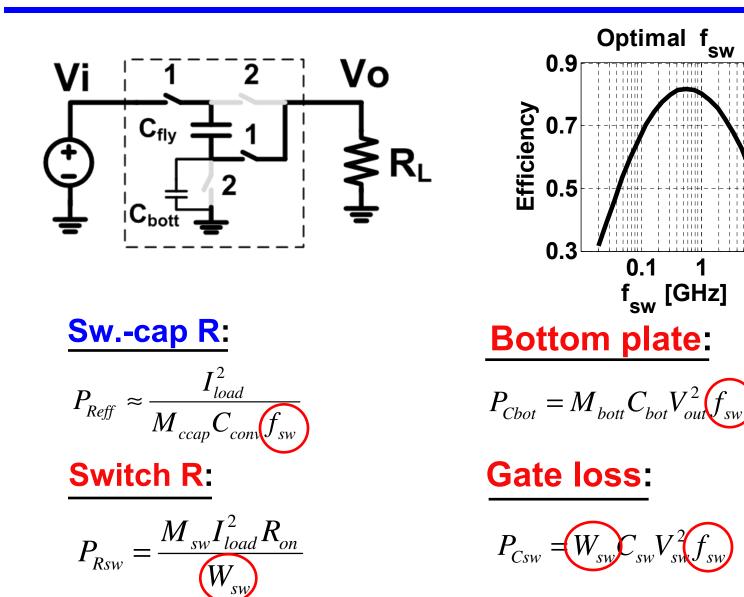

# **Efficiency Optimization**

- Intrinsic loss

- Reduced by  $\uparrow$  C density

- Reduced by  $\uparrow f_{sw}$

- Switch/parasitic loss

- Reduced by  $\uparrow$  switch  $f_T$

- Increased by  $\uparrow f_{sw}$

- Efficiency optimization: choose  $f_{sw}$  and  $W_{sw}$  to balance loss terms

### Loss Terms Detail

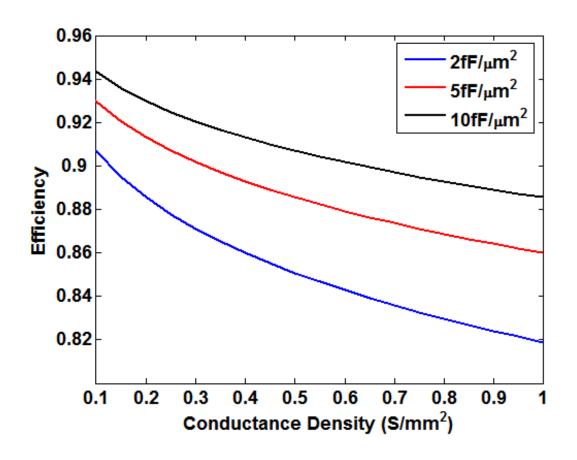

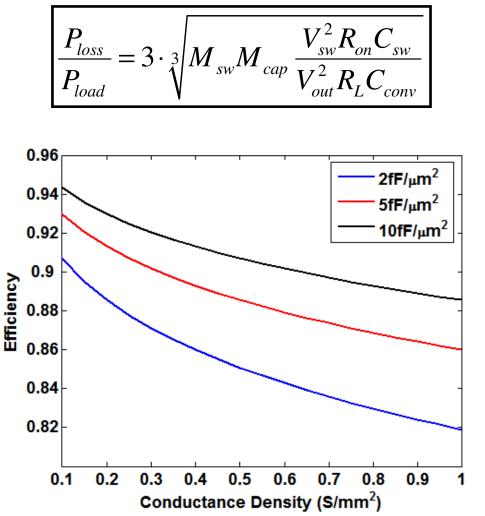

## **Optimized Efficiency**

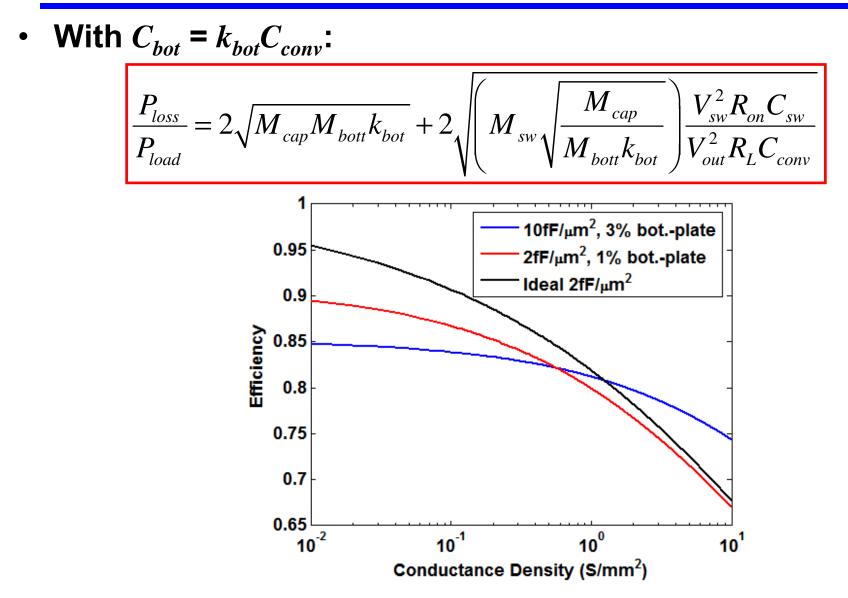

• Ignoring bottom-plate:

$$\frac{P_{loss}}{P_{load}} = 3 \cdot \sqrt[3]{M_{conv,sw}} M_{conv,cap} \frac{V_{sw}^2 R_{on} C_{sw}}{V_{out}^2 R_L C_{conv}}$$

# **Optimized Efficiency** cont'd

- Efficiency set by conductance density

- I.e.,  $(I_{load}/V_{out})$  / Conv. Area

- (Equivalent to power density for given V<sub>out</sub>)

- Typical numbers (1V)

- Mobile device: ~0.1 S/mm<sup>2</sup>

- Processor: ~1 S/mm<sup>2</sup>

- Efficiency trades off with converter area overhead.

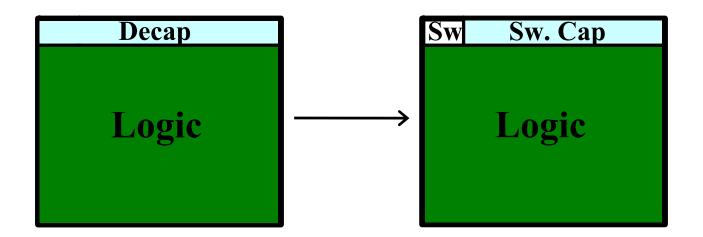

### **Side Note**

- Explicit decoupling capacitance usually required for supply integrity

- Can largely replace decap with converter

- In order to fit, converter needs to deliver ~10X higher density than load

### **Impact of Bottom-Plate**

# Impact of Bottom-Plate cont'd

**Bottom plate sets min. loss:**  $P_{loss}/P_{load} \approx 2\sqrt{M_{cap}M_{bott}k_{bot}}$ • E.g., 2:1 step-down, 1% bottom plate  $\rightarrow$  10% loss

In the limit of low power density:

ullet

- Converter area does not affect efficiency

- Low parasitics more important than cap. density

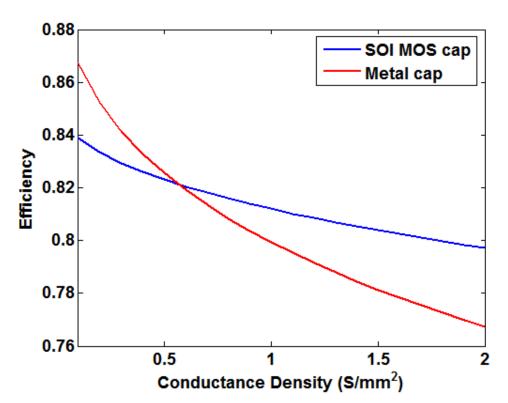

# **Achievable Performance**

- 45nm, 2:1 converter:

- 75% 80% efficiency at 1W/mm<sup>2</sup>

- Even in standard CMOS

- Looks promising

- Reminder: mobile device ~0.1W/mm<sup>2</sup>

- But, only checked one conversion ratio so far...

- How to handle variable voltages?

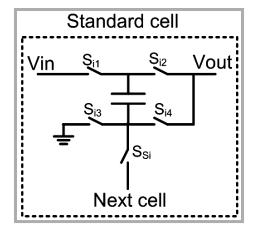

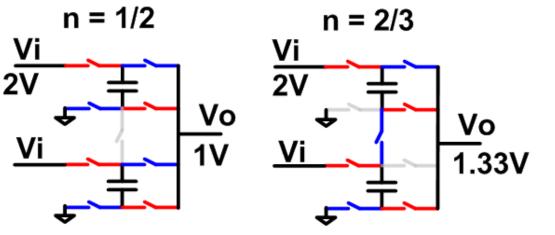

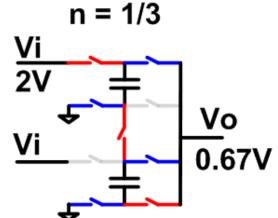

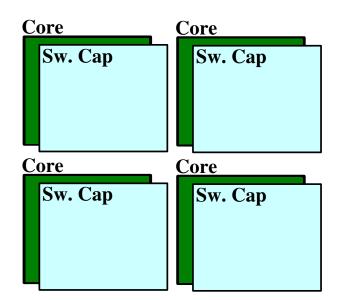

# SC "Standard Cell" Converter

- Integrated capacitors/switches easily partitioned

- "Standard cell" configuration sets conversion ratio

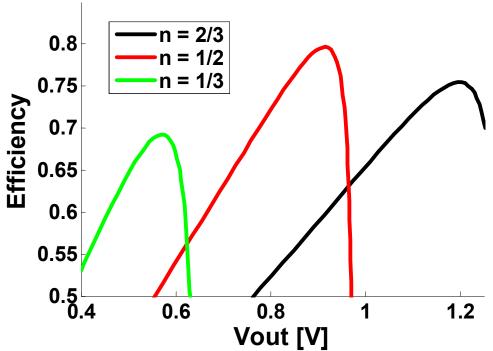

# **Efficiency vs. Conversion Ratio**

- Change topology,  $W_{sw}$ , and  $f_{sw}$

- $R_{out} \sim 1/(Cf_{sw})$

- Just like linear regulator

- Probably need only ~4-5 topologies

- Clustered around 2:1

- Watch out for switch drivers

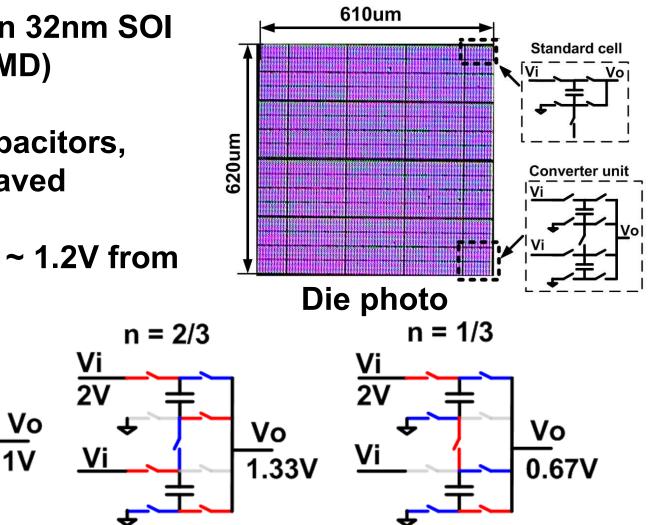

## Prototype

- Implemented in 32nm SOI test-chip (w/AMD)

- MOS flying capacitors, 32-way interleaved

n = 1/2

<u>Vi</u>

Vi

$2\overline{V}$

Supports 0.6V ~ 1.2V from 2V input

H.-P. Le, S. Sanders, and E. Alon, "Design Techniques for Fully Integrated Switched-Capacitor DC-DC Converters," *JSSC* Sept 2011.

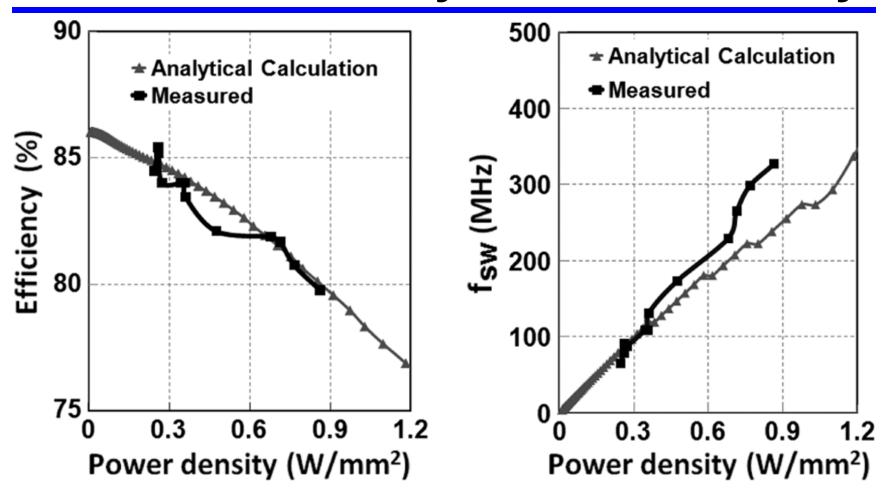

Measured Efficiency vs. Power Density

- Measured with n = 1/2 (Vi = 2V, Vo  $\approx 0.88V$ )

- Matches analysis: ~80% efficiency @ 0.86 W/mm<sup>2</sup>

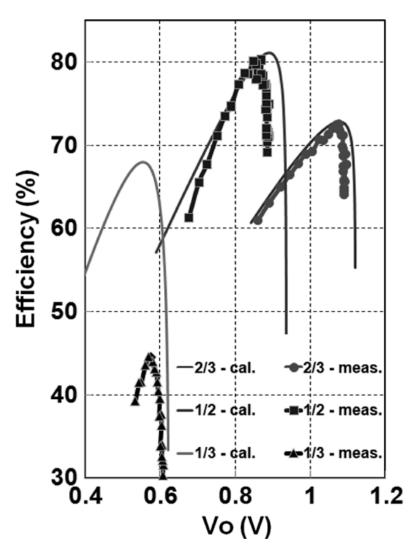

### Measured Efficiency vs. Topologies

- All three topologies functional

- (3:1 efficiency limited by breakdown)

- Efficiency still >70% for 0.75V – 1.15V Vo with 2V Vin

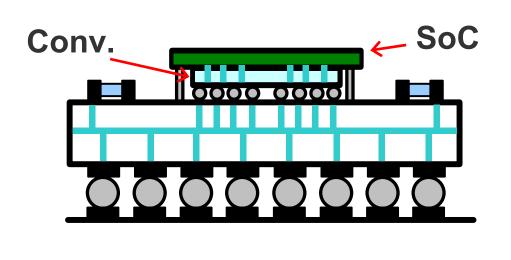

# Looking Forward: Leveraging 2.5/3D Integration

- Enables converter to use entire area over core

- Mitigates efficiency vs. power density tradeoff

- Converter die can use older, lower-cost technology

- While still meeting efficiency & density requirements

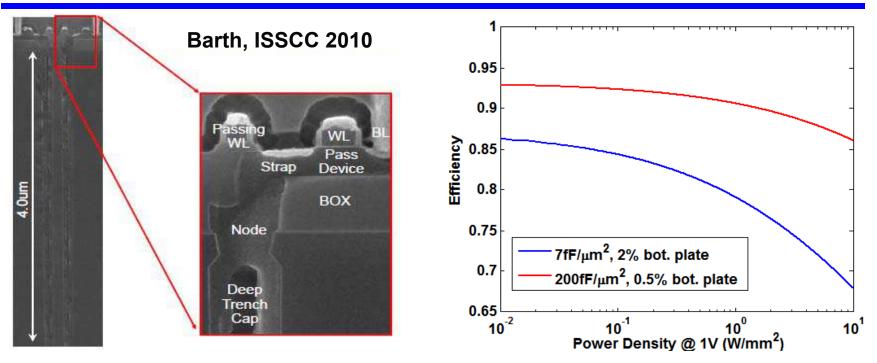

# Looking Forward: Dense Capacitors

- Dense capacitors already exist for DRAM/eDRAM

- IBM eDRAM 2:1 converter\*: 90% efficiency @ 2.3A/mm<sup>2</sup>

- Opportunity to further leverage stacked DRAM

\*L. Chang *et al.*, "A Fully Integrated Switched-Capacitor 2:1 Voltage Converter with Regulation Capability and 90% Efficiency at 2.3A/mm<sup>2</sup>," *IEEE Symposium on VLSI Circuits*, Jun. 2010

### Summary

- Clear need for fully-integrated DC-DC converters

- Multiple off-chip supplies costly, degrade impedance

- Switched-capacitor converters in standard CMOS can achieve:

- In 2:1: ~80% efficiency @ 0.86 W/mm<sup>2</sup>

- >70% efficiency for Vo from ~0.75V to 1.15V with

Vi = 2V

- Low-cost technologies to enable even higher densities, efficiencies already exist

### Acknowledgments

- BWRC students, faculty, and staff

- Focus Center Research Program

- IFC and C2S2

- AMD

- Sam Naffziger, Vishvesh Sathe, Rich DeSantis

- IBM Faculty Award