# Status and Prospect for MRAM Technology

Dr. Saied Tehrani Nonvolatile Memory Seminar Hot Chips Conference August 22, 2010 Memorial Auditorium Stanford University

Everspin Technologies, Inc. - © 2010

#### Agenda

- Current status of MRAM products

- MRAM features

- Current MRAM product operation

- Recent advancement in MRAM technology

- Prospect for MRAM

# **Everspin Introduction**

- Formed as Everspin in June 2008 Previously part of Freescale Semiconductor

- The leading developer and manufacturer of integrated magnetic products

- Industry-first MRAM supplier since June 2006

- Embedded MRAM systems

- Integrated magnetic sensors

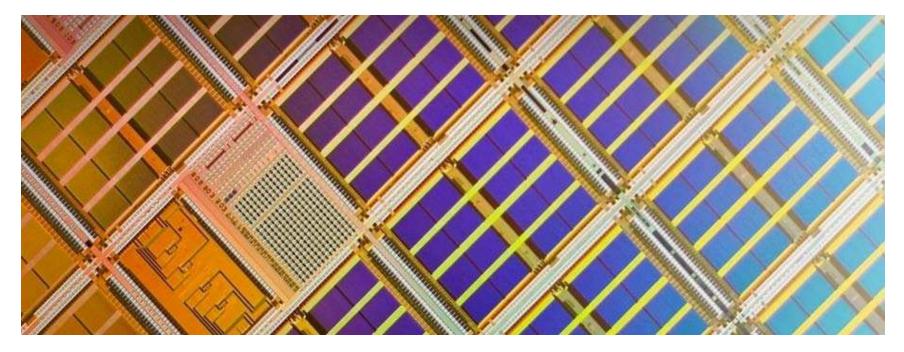

#### Current MRAM products

- Parallel interface products ranging from 256k-16Mb

- Infinite endurance, >20 year data retention, 35 ns read & write speed

- Serial interface products ranging from 256kb-1Mb

- 40 MHz SPI interface, No write delay, infinite endurance

3

# **Everspin MRAM Technology**

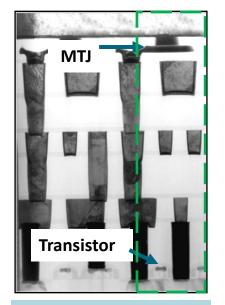

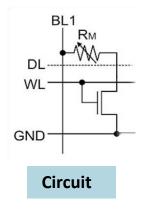

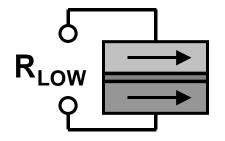

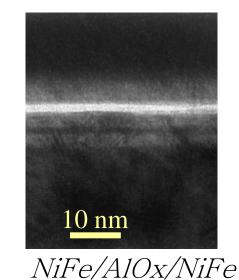

**Cross-sectional view**

- Simple 1 transistor + 1 MTJ memory cell

- Data stored in magnetic polarization, not charge

- State of bit detected as change in resistance

- Always non-volatile

- Non-destructive read, unlimited endurance

- Leverage CMOS semiconductor ecosystem

- Everspin "Electron spin is forever"

LOW RESISTANCE

4

HIGH RESISTANCE

| Parameter                      | Capability                                                                                                                                              |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Non-volatile capability        | <ul> <li>Data retention &gt;20 years</li> </ul>                                                                                                         |  |  |  |

| Performance                    | <ul> <li>Symmetric read/write – 35ns</li> </ul>                                                                                                         |  |  |  |

| Endurance                      | Unlimited cycling endurance                                                                                                                             |  |  |  |

| CMOS integration               | <ul> <li>Easily integrates in manufacturing back-end</li> <li>Compatible with embedded designs</li> <li>No impact on CMOS device performance</li> </ul> |  |  |  |

| Temperature range, reliability | <ul> <li>-40°C &lt; T &lt; 150°C operation demonstrated</li> <li>Intrinsic reliability &gt; 20 years lifetime at 125°C</li> </ul>                       |  |  |  |

| Soft error immunity            | <ul> <li>MRAM cell radiation tolerant</li> <li>Soft error rate from alpha radiation too low to measure (&lt;0.1 FIT/Mb)</li> </ul>                      |  |  |  |

| Environmentally friendly       | <ul> <li>No battery, RoHS compliant, low power</li> </ul>                                                                                               |  |  |  |

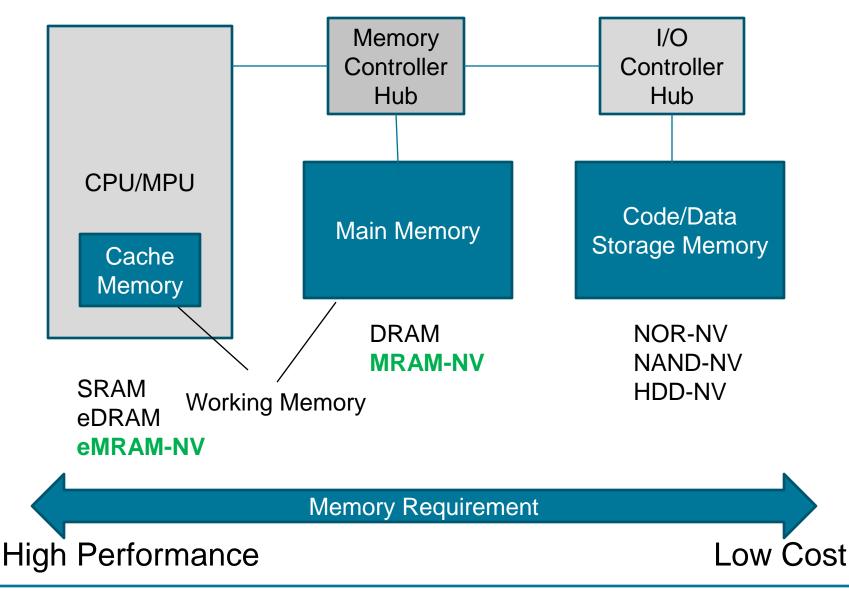

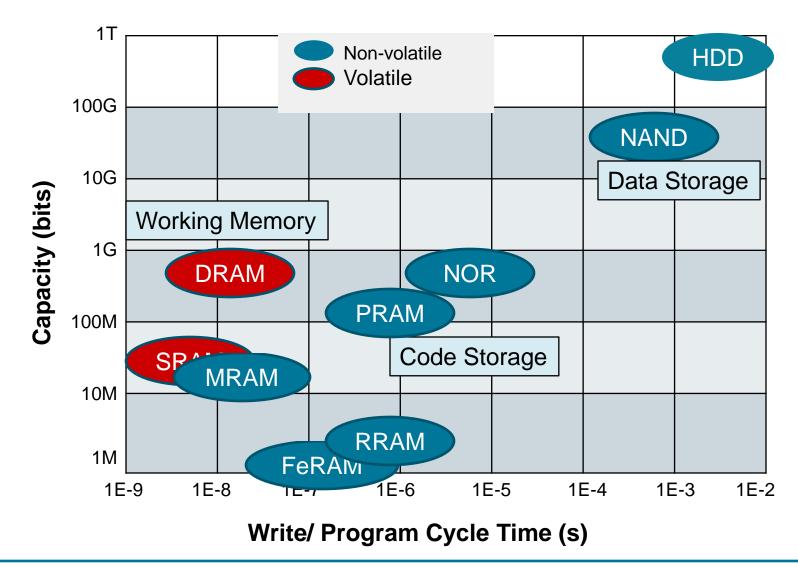

#### **Memory System Hierarchy**

#### Memory Capacity vs. Cycle Time

Memory Endurance vs. Cycle Time EVERSP

#### Agenda

- Current status of MRAM products

- MRAM features

- Current MRAM product operation

- Recent advancement in MRAM technology

- Prospect for MRAM

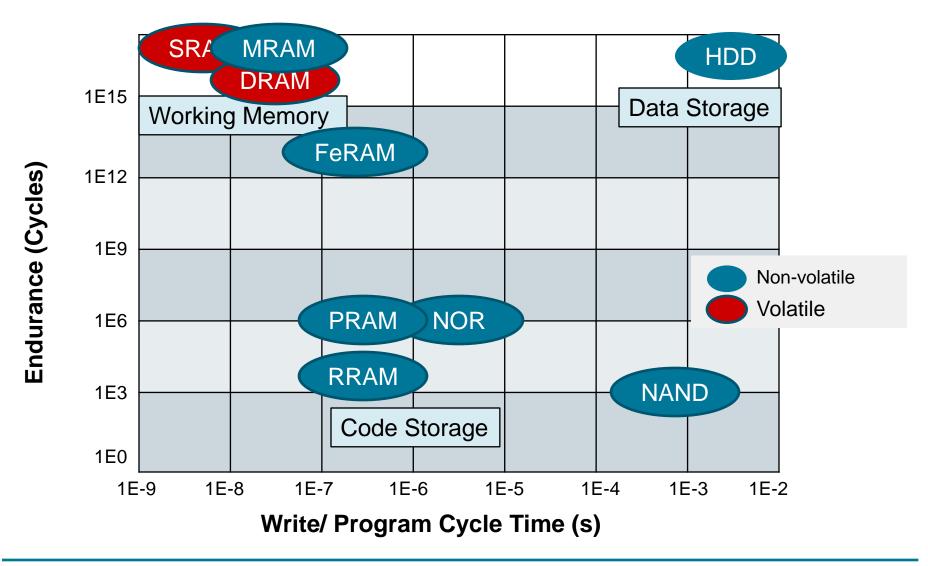

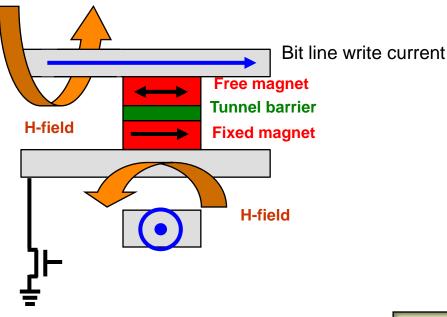

# **MRAM Writes and Reads**

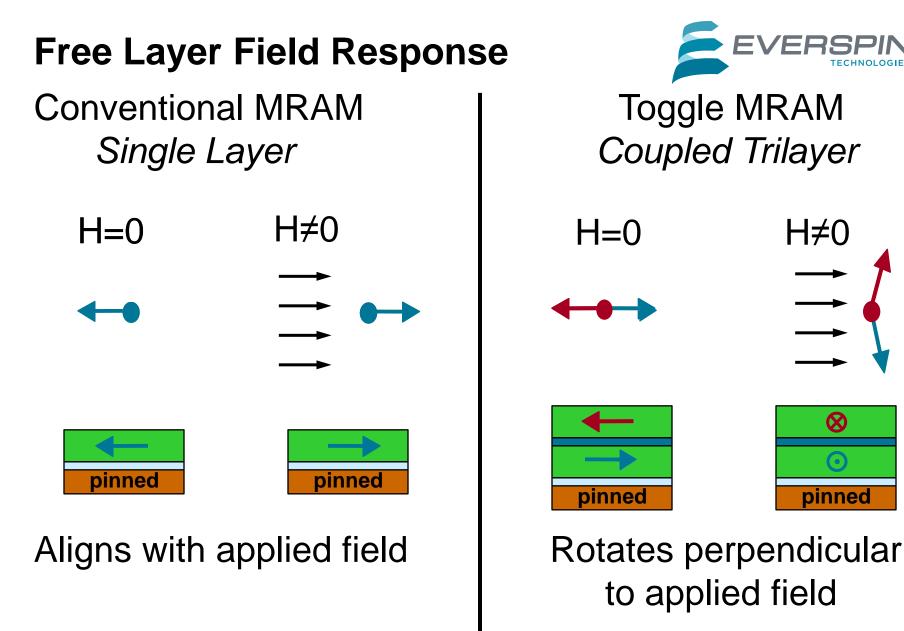

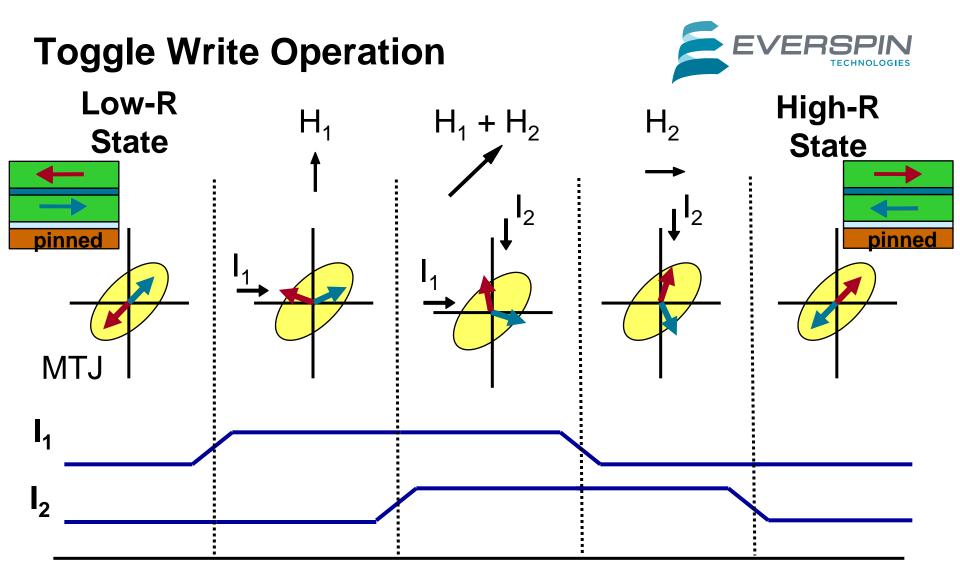

#### Toggle-MRAM in production

Cross-point architecture

Current along bit line and digit line to switch at intersection

- Write Current Flows Down

Write Line 1 & 2

- Magnetic Tunnel Junction (MTJ) At Cross-Point Is

Polarized

- Polarization State Is Read By Selecting Pass Transistor to Sense Resistance of Specific MTJ

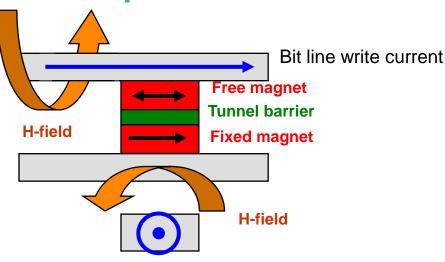

#### **Toggle MRAM Bit Cell**

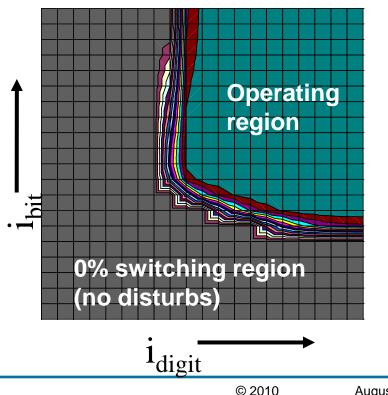

#### Advantages: Eliminates disturb - Large operating window

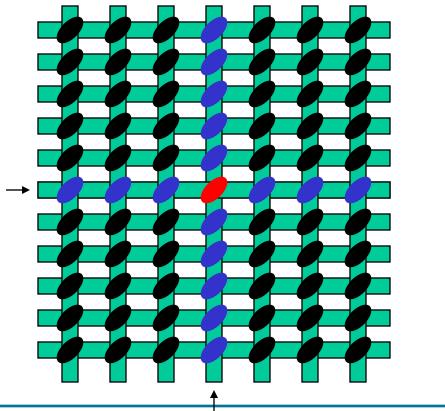

# **Toggle-Bit Selection**

- No ½-select bit disturb

- All bits along <sup>1</sup>/<sub>2</sub>-selected current lines have increased energy barrier during programming

- Single write line can not switch bits

4Mb, March6N Toggle Map

14

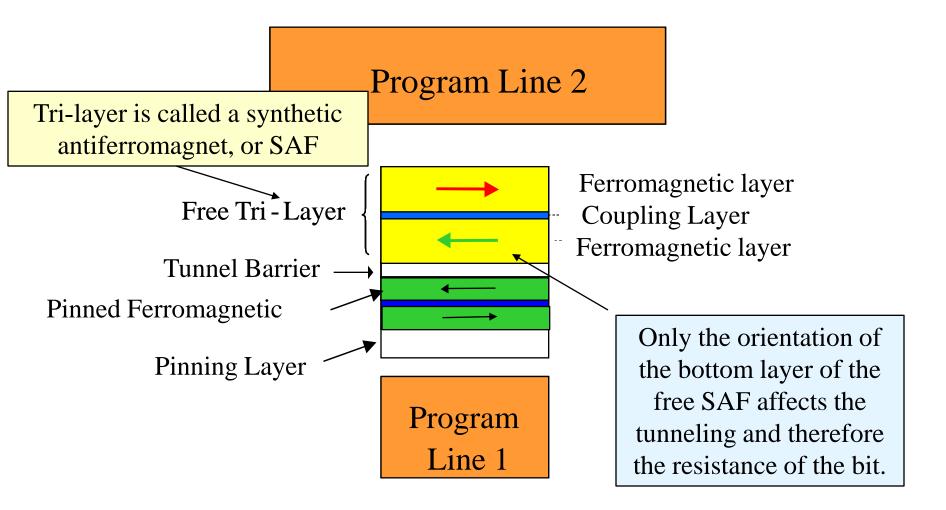

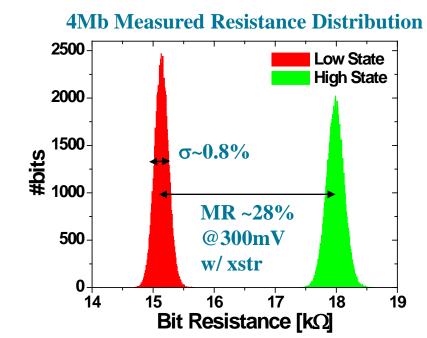

#### **MRAM Storage Concept**

Free Layer Tunnel Barrier Fixed Layer

**Anti-Parallel = High Resistance**

**Parallel = Low Resistance**

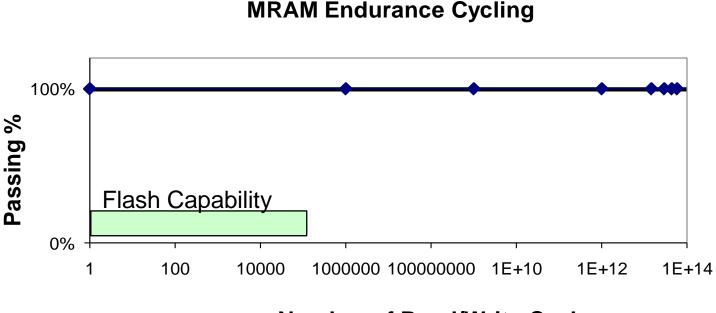

# MRAM: Unlimited Read/Write Endurance

Number of Read/Write Cycles

- MRAM Endurance Tested to 58 Trillion Cycles with No Change in Critical Parameters.

- Data from > 2800 bits from 900 devices

- 8 orders of magnitude more cycles than current Flash technology

- No known failure modes are seen or expected

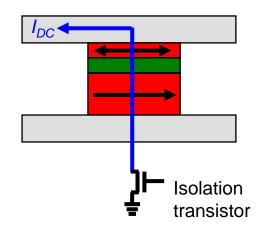

# **MRAM bit switching**

#### Toggle-MRAM in production

#### ST-MRAM in development

Cross-point architecture

Current along bit line and digit line to switch at intersection

- Current  $I_{DC}$  flows through MTJ and transistor

- Fixed magnet polarizes  $I_{DC}$

- Spin-transfer torque programs free magnet

- Conservation of angular momentum

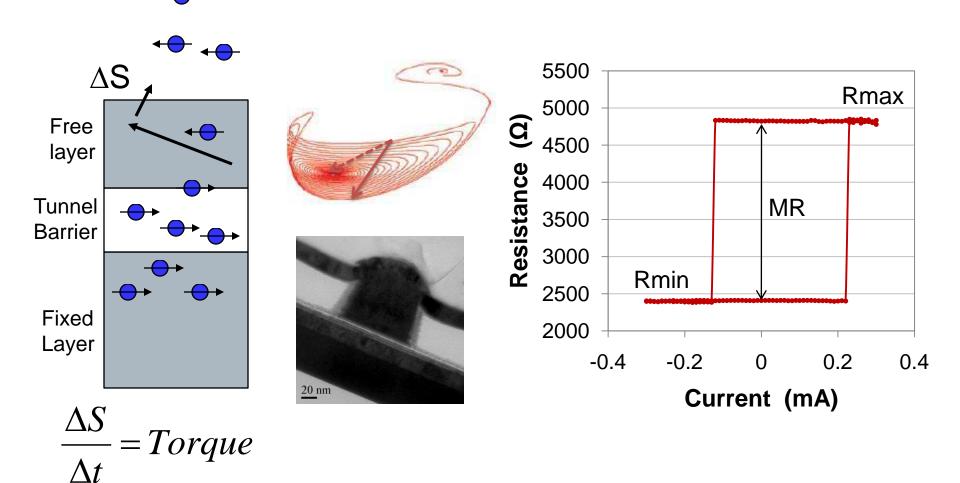

# Spin Torque MRAM

Use spin momentum from current to change direction of S, m.

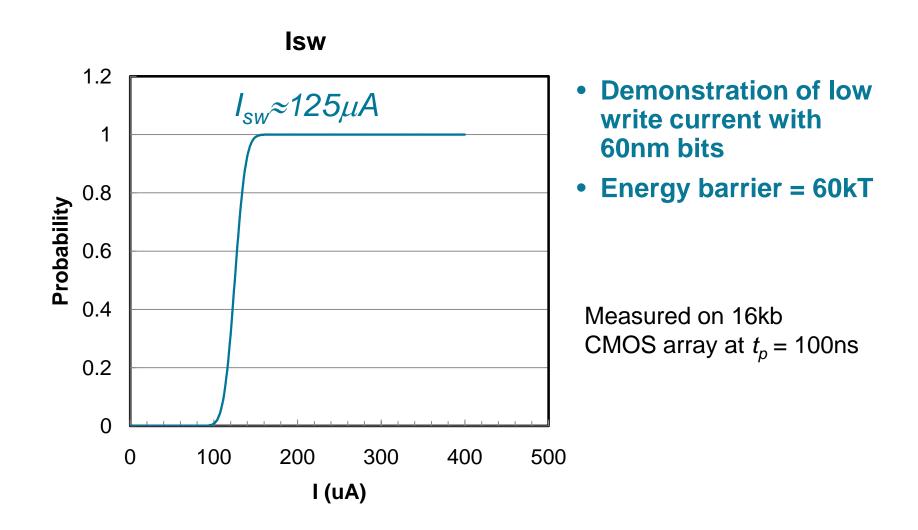

#### Low Switching Current

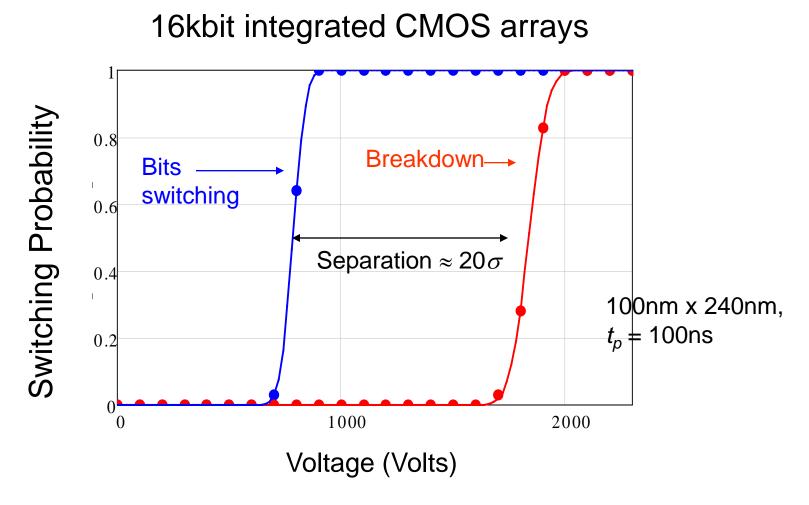

#### Large Separation of $V_{sw}$ and $V_{bd}$

• Excellent separation  $\approx 20\sigma$ , due in part to  $\sigma_{sw} \approx \sigma_{bd} \approx 4\%$

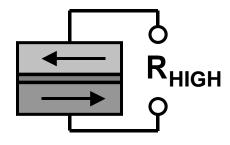

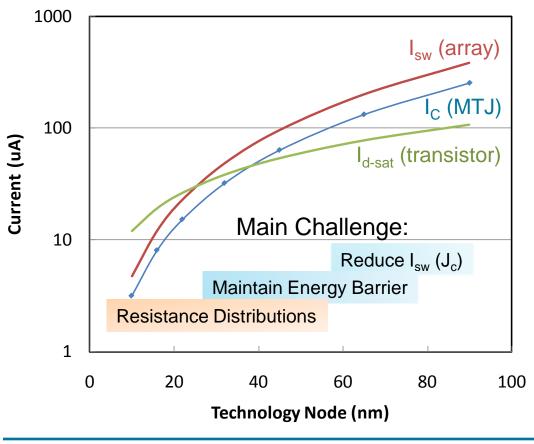

# **Scaling ST-MRAM**

- Today: Reduce  $J_c$  for reliability and smaller transistors

- Continued scaling: maintain energy barrier and manage resistance distributions

- ST-MRAM bits scale favorably to available current from transistor

- Low Jc for reliability is the bigger issue

- Continued scaling requires innovative magnetic devices and materials

- Enhanced energy barrier

- Increased TMR

#### **Memory comparison**

|                       | Toggle<br>MRAM<br>(180 nm) | Toggle<br>MRAM<br>(65 nm)* | ST<br>MRAM<br>(65 nm)*       | FLASH<br>(65 nm)+                                   | DRAM<br>(65 nm)+         | SRAM<br>(65 nm)+   |

|-----------------------|----------------------------|----------------------------|------------------------------|-----------------------------------------------------|--------------------------|--------------------|

| cell size<br>(µm²)    | 1.25                       | 0.16                       | $\underline{0.04^{\dagger}}$ | 0.04                                                | 0.03                     | 0.3                |

| Read time<br>(ns)     | 35                         | 10                         | 10                           | 10 - 50                                             | 10                       | 1                  |

| Program<br>time       | 5 ns                       | 5 ns                       | 10 ns                        | 0.1-100 ms                                          | 10 ns                    | 1 ns               |

| Program<br>energy/bit | 150 pJ                     | 100 pJ                     | <u>1 pJ</u>                  | 10 nJ                                               | 5 pJ<br>Needs<br>refresh | 5 pJ               |

| Endurance             | > 10 <sup>15</sup>         | > 10 <sup>15</sup>         | >10 <sup>15</sup>            | > 10 <sup>15</sup> read,<br>> 10 <sup>5</sup> write | > 10 <sup>15</sup>       | > 10 <sup>15</sup> |

| Non-<br>volatility    | YES                        | YES                        | YES                          | YES                                                 | NO                       | NO                 |

\* 65nm MRAM values are projected

+ These values are from the ITRS roadmap

† This cell size only considers bit area and ignores CMOS limitations

#### Summary

- MRAM is a highly reliable, highperformance, nonvolatile memory ICs, with unlimited endurance

- MRAM has the unique characteristics of a working memory while providing non-volatility

- Current MRAM product densities ranges from 256kb-16Mb

- Continuous advancement in the technology would allow MRAM to drive to higher densities while maintaining its unique characteristics