A Low-Cost Chip Set for Broadband Powerline Communications at 200 Mbps

Chano Gómez, DS2

HotChips'20 August 24-26, 2008 Stanford Memorial Auditorium, Palo Alto, CA

#### What is Powerline Communications?

Powerline Communications is a technology that enables transmission of high-speed data over electrical lines.

#### What are the Applications?

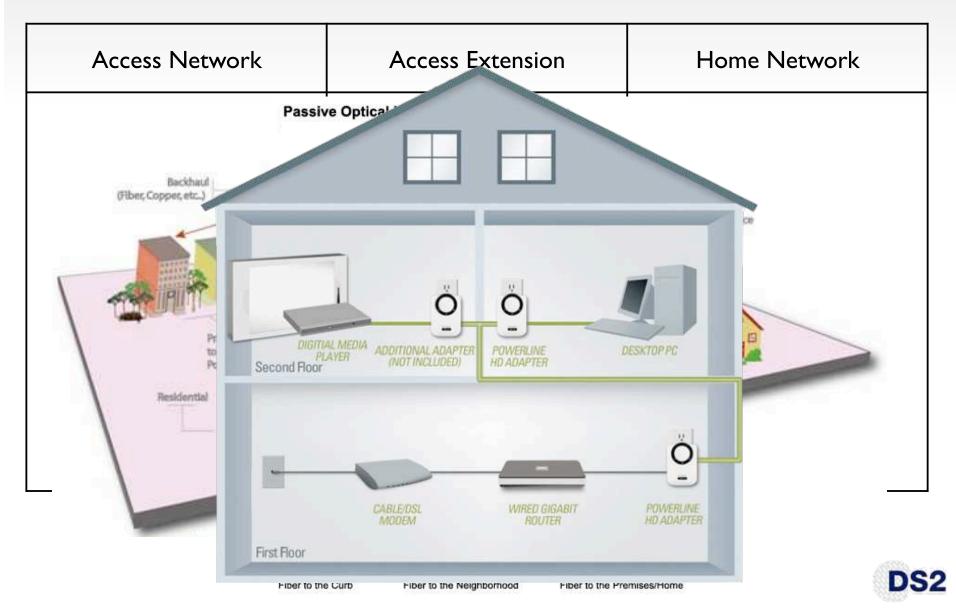

## Wall-plug is most common form factor

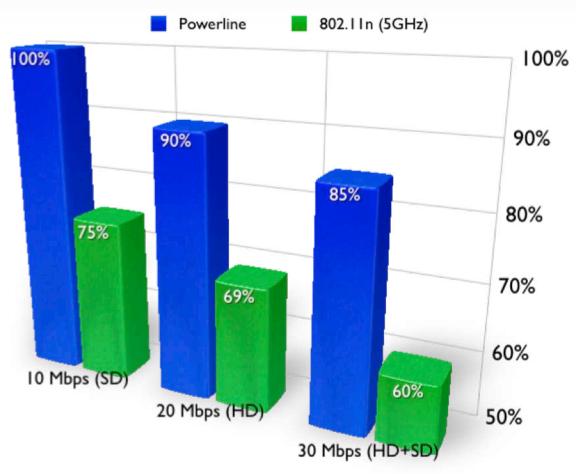

### Why not simply Wireless?

Because Powerline provides connectivity where Wireless 802.11n can't

Percentage of locations capable of delivering 10, 20 & 30 Mbps UDP streams with 0% PLR. Test performed in 9 homes in urban areas in Europe. Source: DS2

#### Powerline Networking is a Challenging Technical Problem

- Electrical wires were never designed for highspeed transmission...

- Uncontrolled and (almost unpredictable) environment

- Impedance mismatch causes Strong multipath effect

- Unknown, non-flat and non-stationary channel frequency response

- Electrical devices connected to the network generate non-gaussian, non-white, non-stationary noise

- Risk of EMC problems because of unshielded wires

#### Technical Features of Modern Powerline Communication Systems

| Feature       | Туре     | Why?                                                                                                              |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------|

| Frequency     | 2-32 MHz | Lower Frequencies are too noisy.<br>Higher Frequencies have too much<br>attenuation and FCC limits are too strict |

| Modulation    | OFDM     | OFDM systems can adapt to non-<br>frequency-flat channels well.                                                   |

| MAC           | TDMA     | Time-Division Multiple Access provides<br>better QoS than CSMA systems                                            |

| PHY Data Rate | 200 Mbps | Currently limited by available spectrum and available SNR                                                         |

| App Data Rate | 120 Mbps | MAC, LLC and FEC overhead                                                                                         |

| Encryption    | AES-256  | To avoid eavesdropping by neighbours!                                                                             |

## Dealing with the specific characteristics of the power line channel

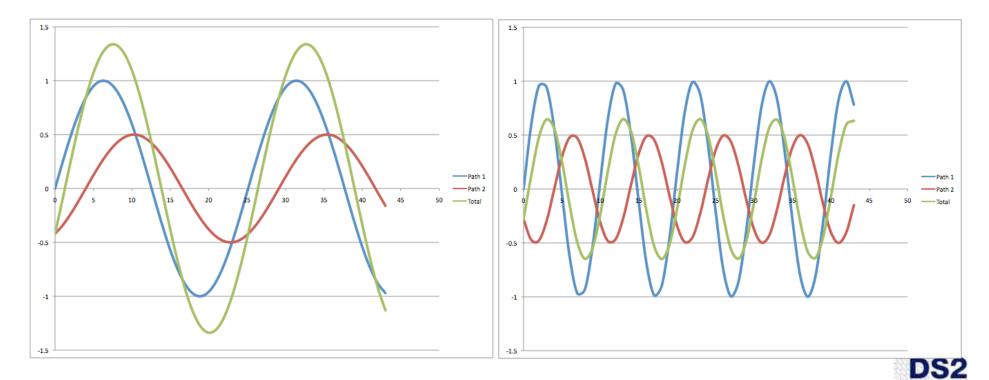

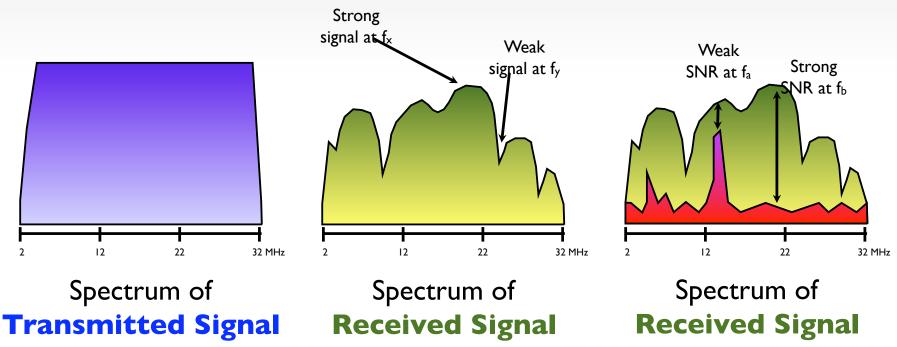

#### Multipath Effect: Channel Response is Frequency Selective

Combination of original signal + echo produce **stronger** signal at frequency f<sub>x</sub> Combination of original signal + echo produce **weaker** signal at frequency f<sub>y</sub>

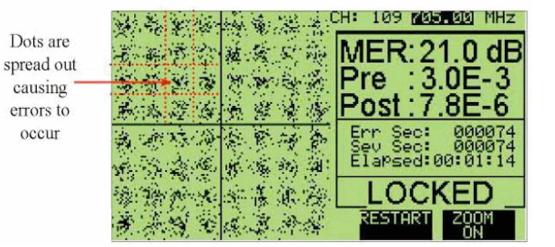

#### How do received signals look like?

+ Noise

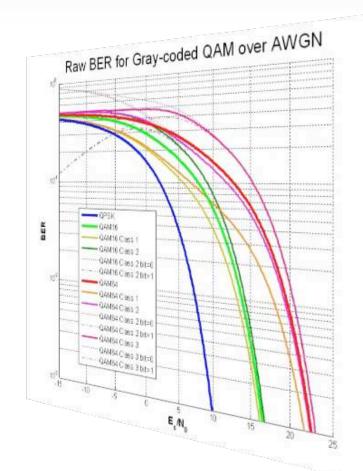

#### SNR Determines Optimum Modulation Scheme

# Each sub-carrier is modulated according to the SNR in that frequency

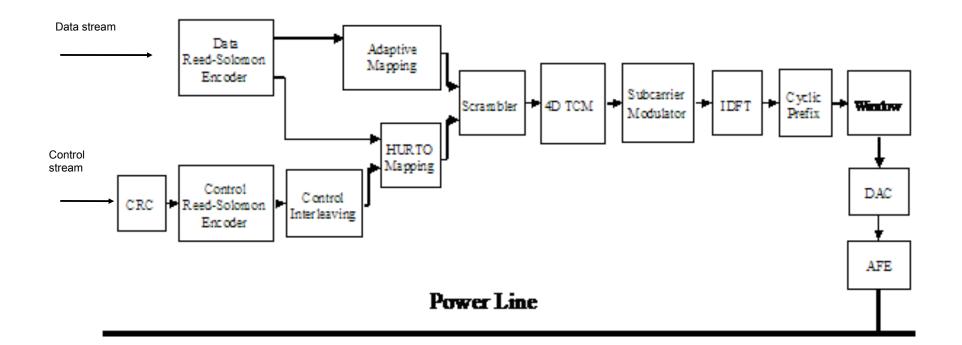

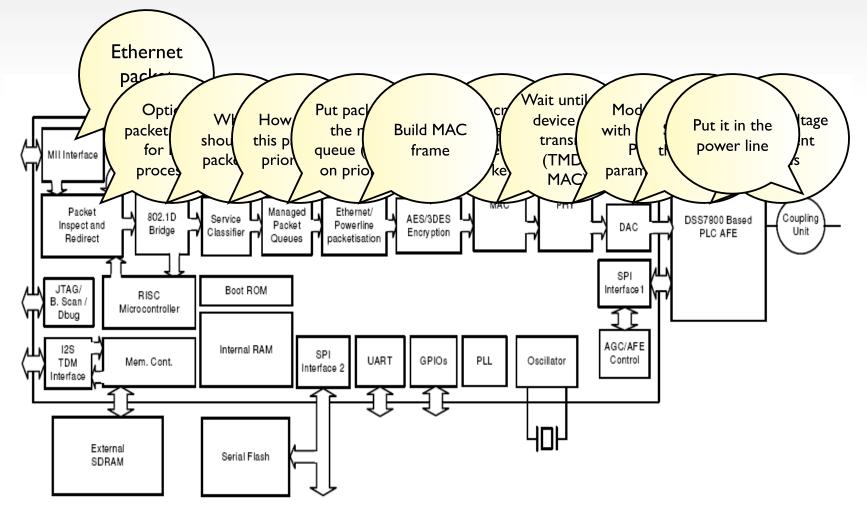

# Block diagram of a powerline communications transceiver

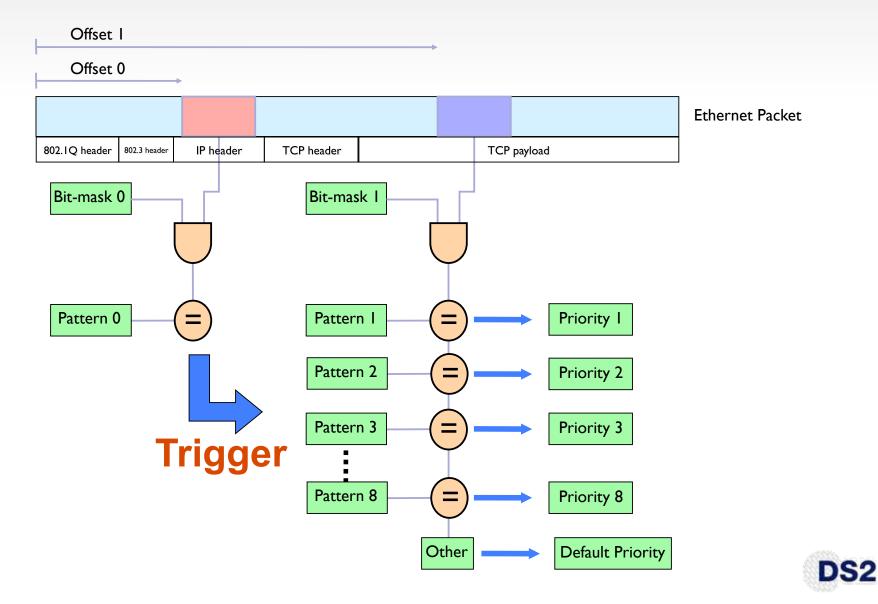

# Programmable QoS is Key

- Powerline networks are usually deployed in environments where packets may not have QoS tags (802.1p, TOS, DSCP, etc)

- Powerline devices need to figure out how to assign priorities with limited information

- Goal: Allows device manufacturers and service providers to create custom QoS rules that are appropriate for the intended application.

- Example in pseudocode:

```

if ethernet.type == IPv4 then

if ip.dst_address == 192.168.4.3 then

powerline.priority = 6

else

powerline.priority = 1

else if ethernet.vlan == 5 then

powerline.priority = 2

```

Note: in practice this is done configuring registers (see next slide...)

#### **Programming Prioritization Rules**

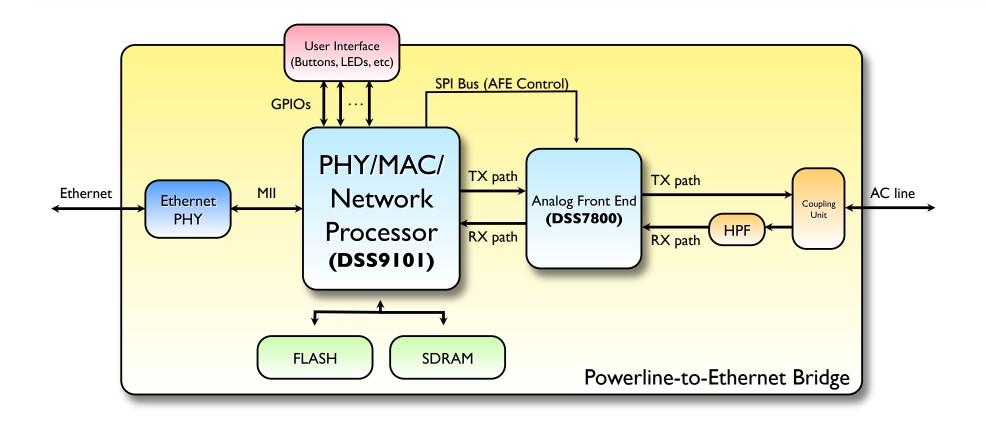

## AITANA<sup>TM</sup> Chipset

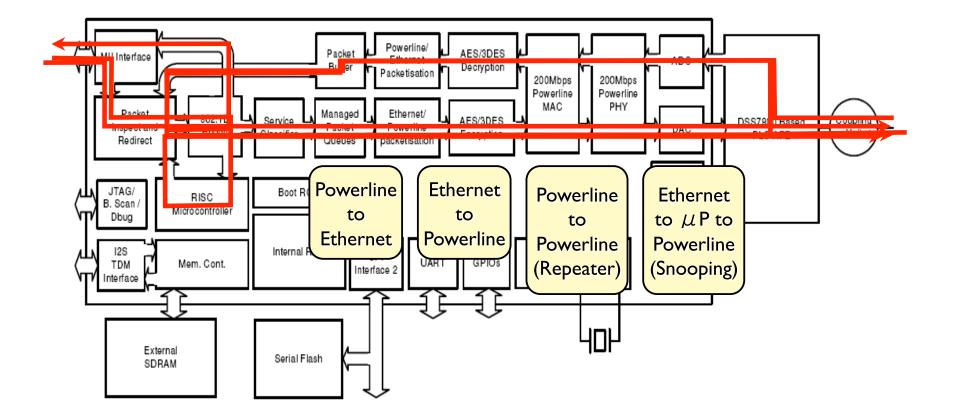

#### Block Diagram of a Powerline-to-Ethernet Bridge

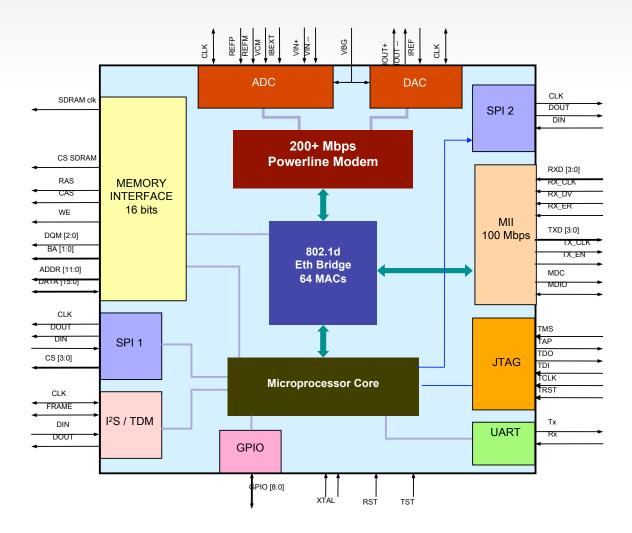

### DSS9101

| Area                   | Description                                                                                                                                                                          |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Application            | PHY, MAC & Network Processor                                                                                                                                                         |  |

| Standard               | UPA (Universal Powerline Association)                                                                                                                                                |  |

| Electrical information | <ul> <li>LQFP176</li> <li>Power consumption: 1.2W</li> <li>I/O Voltage: 3.3V</li> <li>Core Voltage: 1.5V</li> </ul>                                                                  |  |

| РНҮ                    | <ul> <li>OFDM Modulation (1536 carriers)</li> <li>2-32 MHz</li> <li>Programmable Carrier Notching</li> <li>Reed-Solomon + 4D-Trellis FEC</li> <li>Up to 16 remote devices</li> </ul> |  |

| Data Rate              | <ul> <li>200 Mbps (PHY layer)</li> <li>120 Mbps (Ethernet layer)</li> <li>128k packets/sec</li> </ul>                                                                                |  |

| Ethernet Switch        | <ul> <li>802.1d compliant, supports STP</li> <li>802.1Q compliant</li> <li>32 MAC addresses</li> <li>Packet Snooping (IGMP, etc)</li> <li>Supports automatic repeating</li> </ul>    |  |

| Security               | <ul> <li>AES-256, AES-128, 3DES &amp; DES Encryption</li> <li>Support for "One-Button Security"</li> </ul>                                                                           |  |

| QoS                    | <ul><li> 8 priorities</li><li> Programmable prioritization rules</li></ul>                                                                                                           |  |

| Embedded Processor     | <ul> <li>Tensilica Xtensa (160 MHz)</li> <li>SDK available</li> </ul>                                                                                                                |  |

| Interfaces             | • MII, 2 × SPI, I2S/TDM, 8 × GPIO, JTAG, UART                                                                                                                                        |  |

| Technology             | Toshiba SoC     ADC, DAC, PLL provided by Toshiba                                                                                                                                    |  |

## DSS9191 Block Diagram

#### Packet Flow inside the DSS9101

### Example of Supported Modes

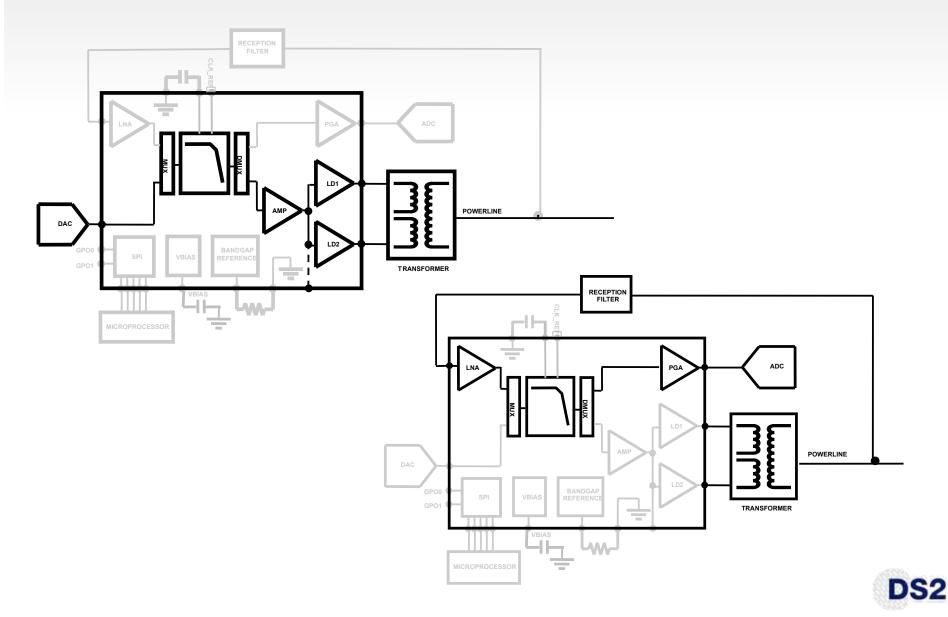

## DSS7800

| Area                      | Description                                                                                                                                                                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application               | • AFE (Filter + Line Driver)                                                                                                                                                                                                                          |

| Electrical<br>information | <ul> <li>QFN48 7x7mm RoHS</li> <li>5V Power Supply</li> <li>Power consumption:</li> <li>Tx mode: 1700 mW</li> <li>Rx mode: 685 mW</li> <li>Idle mode: 15 mW</li> </ul>                                                                                |

| Features                  | <ul> <li>Integrated Line Driver</li> <li>Integrated Low Pass Filter (Anti-aliasing &amp; Smoothing)</li> <li>Power-down Control for each path</li> <li>Programmable Low Noise Amplifier</li> <li>Fully Differential</li> <li>SPI Interface</li> </ul> |

| Manufacturing             | Austria Micro Systems                                                                                                                                                                                                                                 |

#### Transmission & Reception Mode

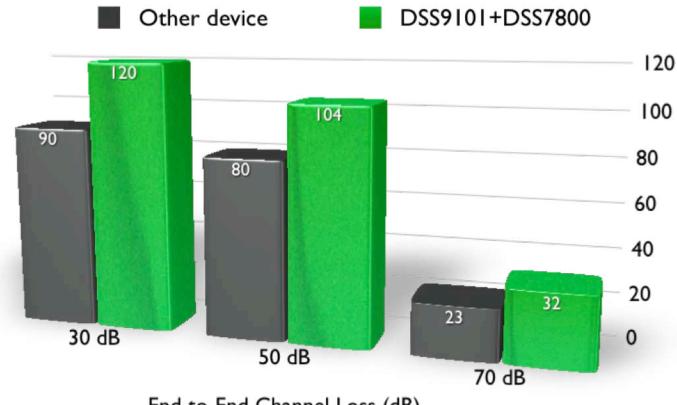

## Network Performance

#### Ethernet Throughput in Mbits/sec

End-to-End Channel Loss (dB)

Test set-up: Two powerline adapters connected through flat channel attenuators in isolated network. Test software: Chariot (bidirectional data transfer). Equipment: DS2's DW21P reference design (DSS9101 chip) and Devolo AV Easy (INT6300 chip). AC cycle: 60Hz.

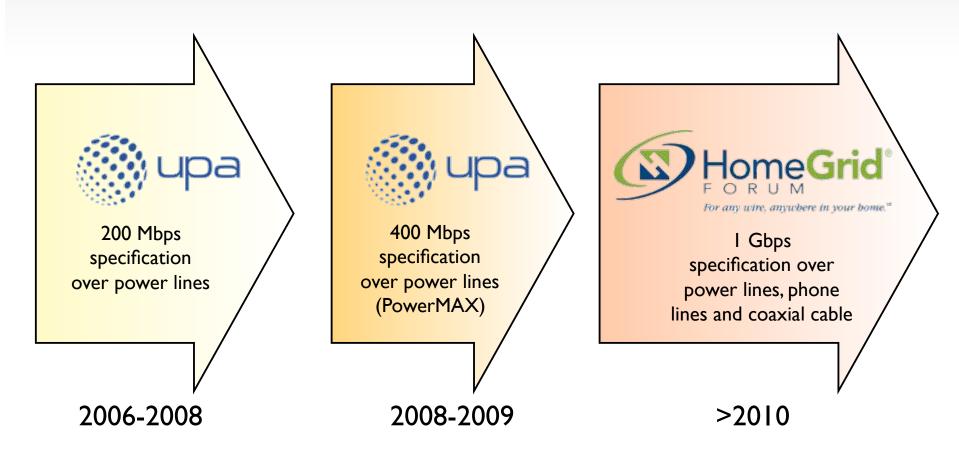

## What next?

A Low-Cost Chip Set for Broadband Powerline Communications at 200 Mbps

Chano Gómez, DS2

HotChips'20 August 24-26, 2008 Stanford Memorial Auditorium, Palo Alto, CA