## **Next-Generation Mobile Computing:** Balancing Performance and Power Efficiency

HOT CHIPS 19 Jonathan Owen, AMD

# <section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item>

# **Addressing these Challenges**

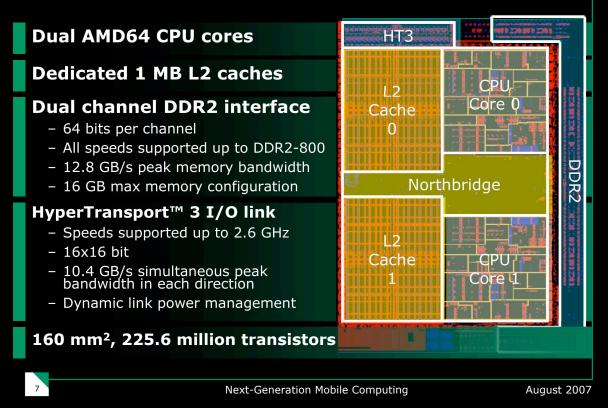

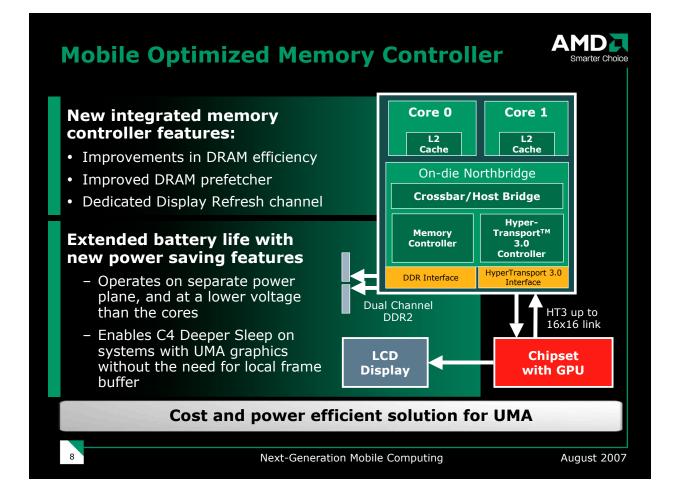

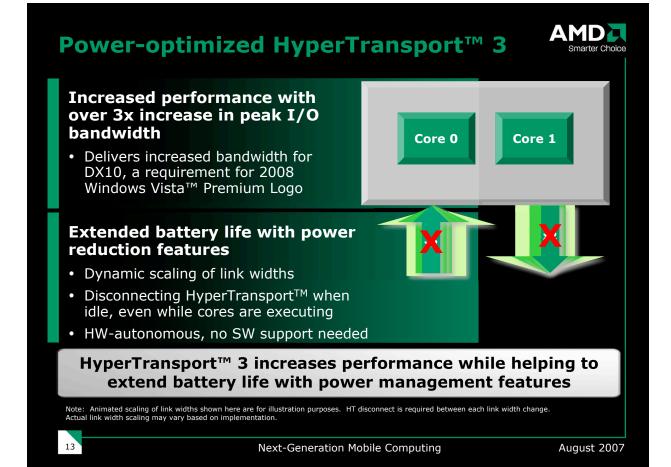

- Increase system bandwidth for UMA solutions

- Performance: HyperTransport<sup>™</sup> 3, dedicated display refresh virtual channel, maximize DRAM efficiency

- Power: HT3 power management extensions, Memory controller on its own power plane

- Power efficiency

5

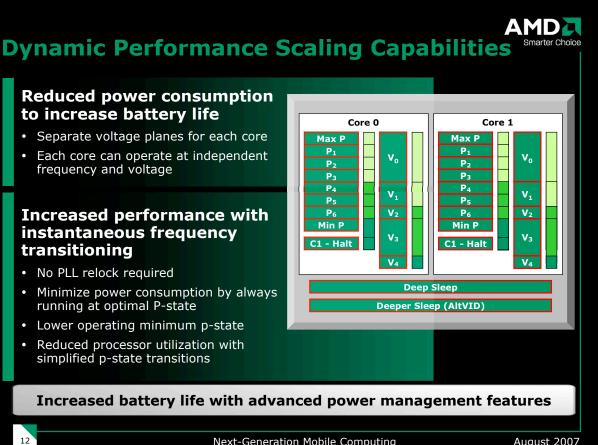

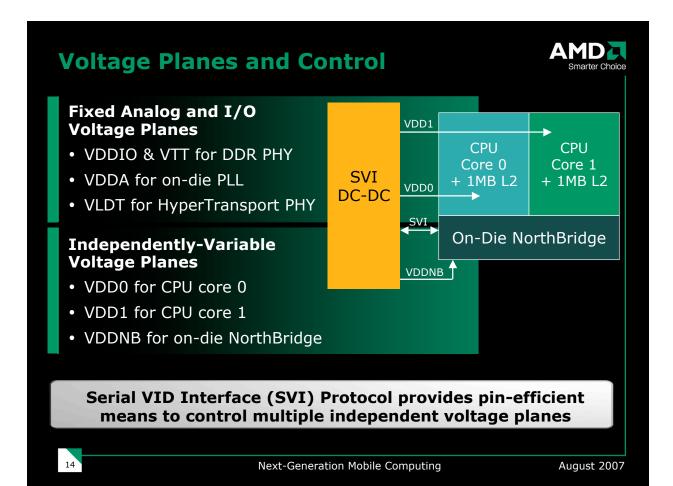

- Split power planes, independent frequency selection (core0, core1, NB are independent)

- Fast frequency changes without PLL relock using digital frequency synthesizers

- Improved efficiency allows lower power for fixed workloads, or higher performance for fixed power

Next-Generation Mobile Computing

August 2007

# **A Few Details**

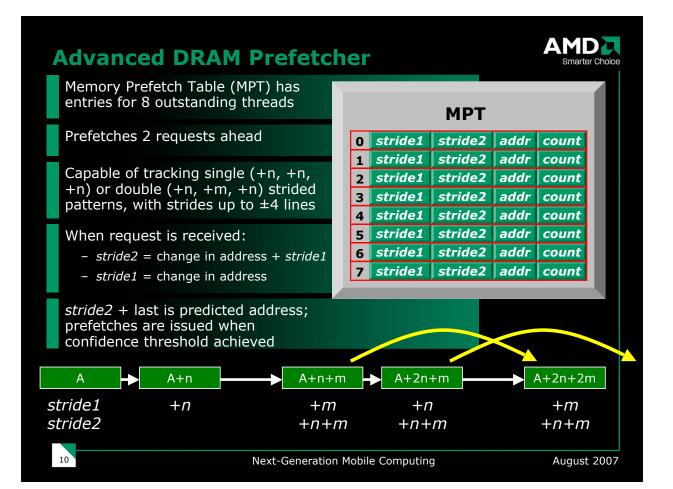

## **DRAM Efficiency Maximization**

#### Aggressive use of bypass paths to minimize idle latency

#### Bank state tracking

- Chip selects are interleaved to increase number of distinct banks

- Unganging of DRAM channels further increases number of banks

- 16 banks per channel are tracked, using LRU algorithm

- Pages can be closed dynamically, based on bank access pattern

### Out of Order (OOO) scheduling of requests, based on:

- Request priority (programmable by type: low/med/high)

- Page status (miss/hit/conflict)

#### Write bursting

9

Writes are accumulated and done at once to minimize bus turnaround

Next-Generation Mobile Computing

# **Display Refresh Optimization**

11

High bandwidth, high latency, but latency guarantee required to avoid display buffer underrun

Doesn't fit well in existing HyperTransport<sup>™</sup> VC sets

- Base channels provide no latency guarantees

- Isoc channels are low bandwidth; can starve other traffic

Requests arrive via HyperTransport<sup>™</sup> Isoc channel

- Detected by decoding coherence and ordering requirements

- Has dedicated buffer and routing resources internally

- Chipset must manage interaction with Isoc traffic

Memory controller priority is variable based on age

Next-Generation Mobile Computing

# **Fine Grain Power Management**

#### **CPU core power-state transitions**

• Simple software interface

15

Cores continue execution while frequency changes are in progress

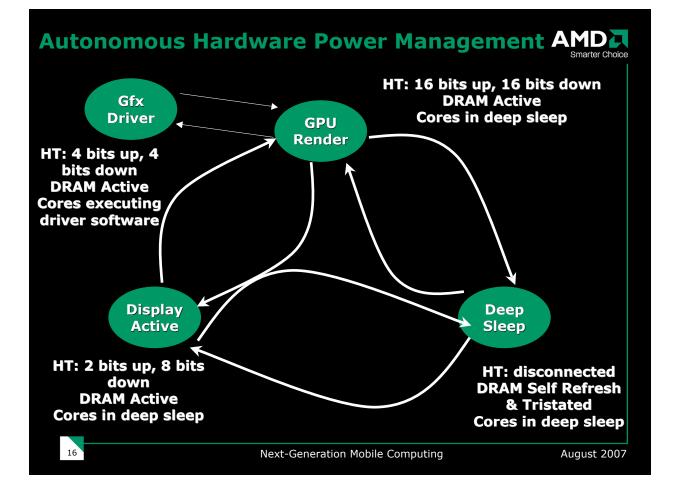

#### Autonomous hardware power management

- CPU and chipset work together to establish the most power efficient settings

- Eliminates reliance on software for maximum power efficiency

- The CPU informs the chipset when P-states change or HALT condition reached

- The chipset monitors I/O traffic and CPU state and establishes the optimal power management profile for a given set of system conditions

Current-generation power management schemes remain supported

Power efficiency via dynamic hardware power management

Next-Generation Mobile Computing

# **Power and Performance Tradeoffs**

AMD Smarter Choice

| Feature                                                        | Attributes                                                       |  |  |  |  |

|----------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| Independent CPU core voltage planes and frequency selection    | Power consumption matches<br>CPU performance delivered           |  |  |  |  |

| Separate voltage plane for on-<br>die NorthBridge              | Enables CPU deep sleep with integrated graphics.                 |  |  |  |  |

| Dynamic HT ™ link power<br>management                          | Power consumption matches<br>interconnect bandwidth<br>delivered |  |  |  |  |

| Autonomous hardware control of CPU core deep sleep state       | Increased residency in CPU deep sleep state                      |  |  |  |  |

| Autonomous hardware control of DRAM self-refresh state         | Increased residency in DRAM sleep state                          |  |  |  |  |

| CPU core deep sleep wakeup to service probes at lowest P-State | Increased residency in CPU<br>deep sleep state                   |  |  |  |  |

|                                                                |                                                                  |  |  |  |  |

| Next-Generation Mobile Computing August 200                    |                                                                  |  |  |  |  |

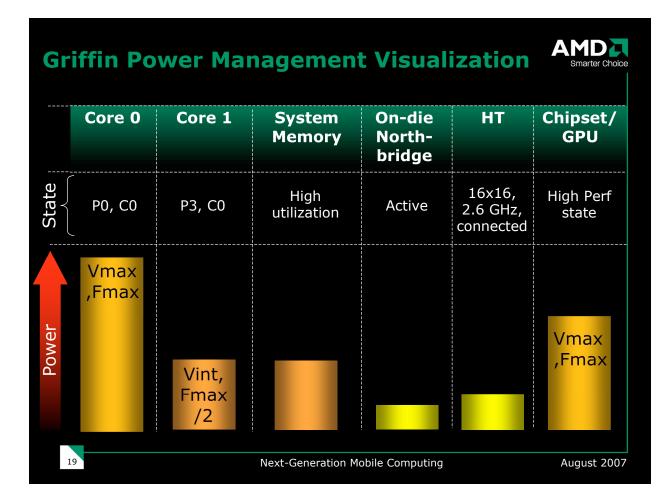

# Griffin Power Management Visualization

|       | Core 0        | Core 1        | System<br>Memory    | On-die<br>North-<br>bridge | НТ                              | Chipset/<br>GPU    |

|-------|---------------|---------------|---------------------|----------------------------|---------------------------------|--------------------|

| State | P0, C0        | P0, C0        | High<br>utilization | Active                     | 16x16,<br>2.6 GHz,<br>connected | High Perf<br>state |

| Power | Vmax<br>,Fmax | Vmax<br>,Fmax |                     |                            |                                 | Vmax<br>,Fmax      |

| 18    | 3             |               | Next-Generation Mo  | obile Computina            |                                 | August 2007        |

#### **Griffin Power Management Visualization** Smarter Choice Core 1 System **On-die** Chipset/ Core 0 HT North-GPU Memory bridge State 16x16, High Perf High Pmin, C1 P3, C0 Active 2.6 GHz, utilization state connected Power Vmax ,Fmax Vint, Fmax Vmin /2 20 Next-Generation Mobile Computing August 2007

| Gri   | Smarter Choice              |          |                    |                            |                   |                   |

|-------|-----------------------------|----------|--------------------|----------------------------|-------------------|-------------------|

|       | Core 0                      | Core 1   | System<br>Memory   | On-die<br>North-<br>bridge | НТ                | Chipset/<br>GPU   |

| State | Pmin, C1                    | Pmin, C1 | Self refresh       | Clocks<br>gated            | Dis-<br>connected | Low Perf<br>state |

| Power | C1E with<br>appl<br>(Deeper | lied     |                    |                            |                   |                   |

| 21    |                             |          | Next-Generation Mo | obile Computing            |                   | August 2007       |

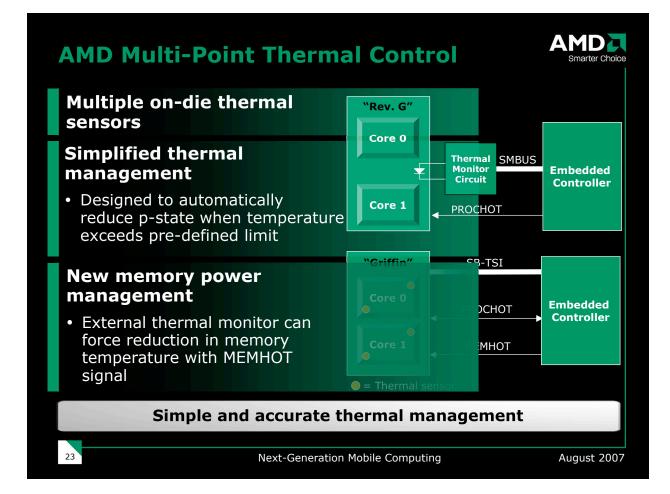

# **Griffin Power Management Visualization**

|       | Core 0                     | Core 1                           | System<br>Memory | On-die<br>North-<br>bridge | HT                            | Chipset/<br>GPU                |

|-------|----------------------------|----------------------------------|------------------|----------------------------|-------------------------------|--------------------------------|

| State | Pmin, C1                   | Pmin, C1                         | Active           | Active                     | 2x8,<br>2.6 GHz,<br>connected | Low Perf<br>state<br>(refresh) |

| Power | C1E with<br>app<br>(Deeper | lied                             |                  |                            |                               |                                |

| 2     | 2                          | Next-Generation Mobile Computing |                  |                            |                               |                                |

AMD Smarter Choice

#### Disclaimer

The information presented in this document is for information purposes only.

The information contained herein is subject to change and may be rendered inaccurate for many reasons, including, but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION.

AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY DIRECT, INDIRECT, SPECIAL OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN OR FOR THE PERFORMANCE OR OPERATION OF ANY PERSON, INCLUDING, WITHOUT LIMITATION, ANY LOST PROFITS, BUSINESS INTERRUPTION, DAMAGE TO OR DESTRUCTION OF PROPERTY, OR LOSS OF PROGRAMS OR OTHER DATA, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **Trademark Attribution**

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. PCIe is a registered trademark of PCI-SIG. HyperTransport is a licensed trademark of the HyperTransport Consortium. Other names used in this presentation are for identification purposes only and may be trademarks of their respective owners.

©2007 Advanced Micro Devices, Inc. All rights reserved.

Next-Generation Mobile Computing