IBM Research – T. J. Watson Research Center

# CMOS Technology Nodes: Trends, Challenges, Opportunities?

Ghavam Shahidi IBM Research Division

#### IBM Research

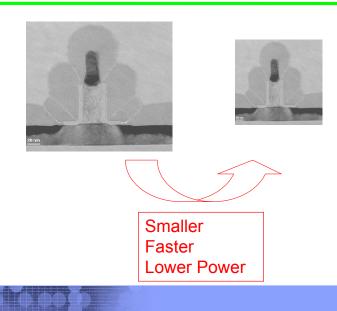

## **CMOS Scaling: Dennard's Theory**

#### Scaled technology generations

IBM

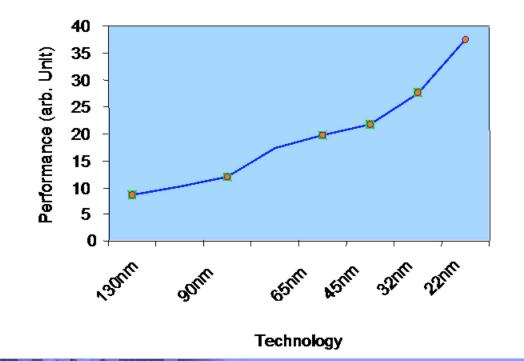

## **Device Performance: ~30% per Generation**

### IBM Research

### **Performance Challenge**

- Technology performance gain continuing

- Through 32-22 nm nodes

- Power-delay curve improving

- Issue: Supply voltage not going down

- Power density (and power)

- Solution: Industry moving to multi "low-power" cores

- Performance not through frequency

- Do we care as much about performance?

- System performance: Number of cores vs. the frequency

- Drive to higher VT's and lower supply => Effectively devices not as fast

IB

IBM Research

## **Device Pitch Scaling**

IBM

| Node | Device Pitch (nm) | Year    |

|------|-------------------|---------|

| 65   | 230-350           | 2006    |

| 45   | 170-180           | 2008    |

| 32   | 120-130           | 2010    |

| 22   | 90-100            | 2012    |

| 15   | 70-80             | 2014-15 |

| 11   | 55-65             | 2017-18 |

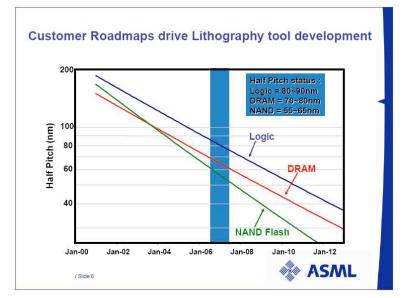

## Lithography Roadmap (ASML)

IBM

IBM

70-80 nm pitch (15 nm node) is feasible with immersion

IBM Research

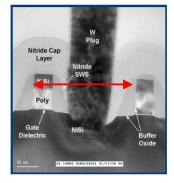

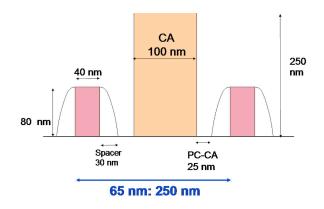

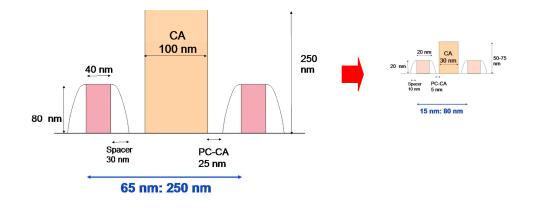

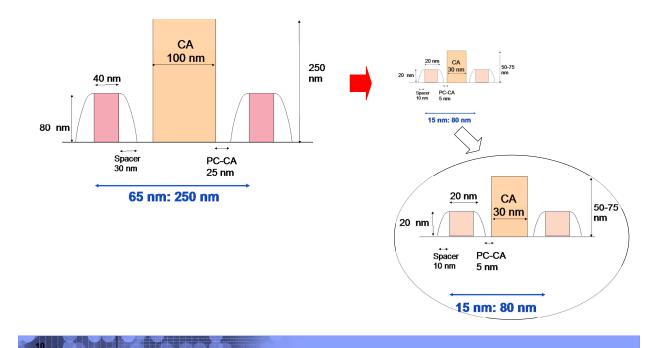

15 nm (Post 22) Node Cross Section:

IBM

## 15 nm (Post 22) Node Cross Section:

#### IBM Research

## 15 nm (Post 22) Node Cross Section:

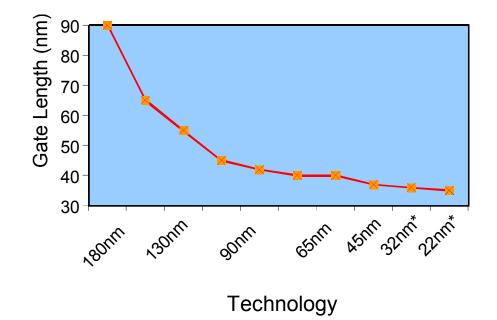

## **Challenge: L Scaling**

IBA

IBM

#### IBM Research

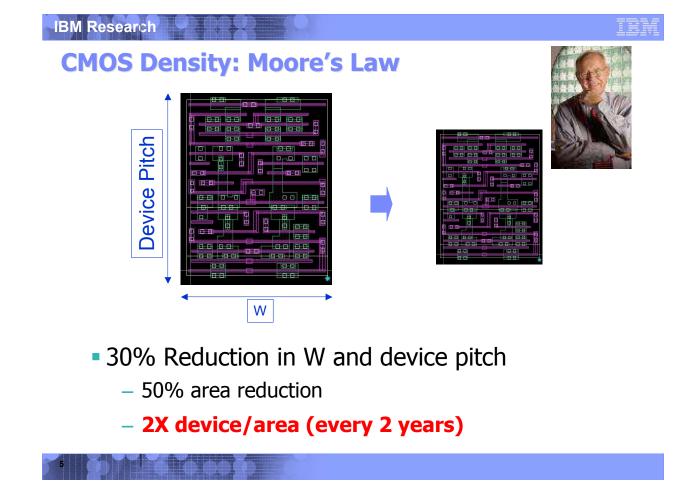

## Value of CMOS Scaling: Transistors/Unit Area

Extrapolate from 65 nm Intel's Xeon and IBM's Power 6 dual cores

| Node | Transistors /<br>cm2 | Transistors /<br>450 mm2 |

|------|----------------------|--------------------------|

| 65   | 0.2 B                | 0.9 B                    |

| 45   | 0.4 B                | 1.8 B                    |

| 32   | 0.8 B                | 3.6 B                    |

| 22   | ~1.6 B               | 7.2 B                    |

| 15   | ~3.2 B               | 14.4 B                   |

| 11   | ~6.4 B               | 25.8 B                   |

## Value of CMOS Scaling: Transistors/Unit Area

Extrapolate from 65 nm Intel's Xeon and IBM's Power 6 dual cores

| Node | Transistors /<br>cm2 | Transistors /<br>450 mm2 |

|------|----------------------|--------------------------|

| 65   | 0.2 B                | 0.9 B                    |

| 45   | 0.4 B                | 1.8 B                    |

| 32   | 0.8 B                | 3.6 B                    |

| 22   | ~1.6 B               | 7.2 B                    |

| 15   | ~3.2 B               | 14.4 B                   |

| 11   | ~6.4 B               | 25.8 B                   |

3D will add another 2-3X more transistors/unit area

IBM Research

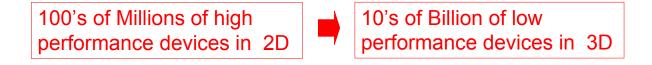

## **CMOS Paradigm Shift**

- Device count will continue to go up

- Moore's Law goes on

- Key challenges:

- What to do with multi billion transistors / cm2

IEI

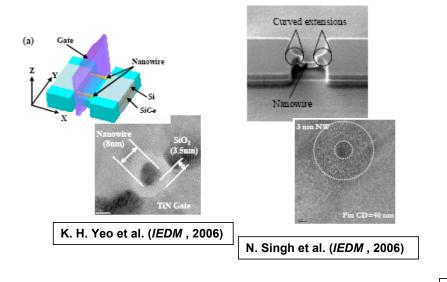

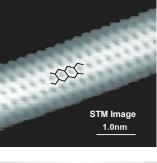

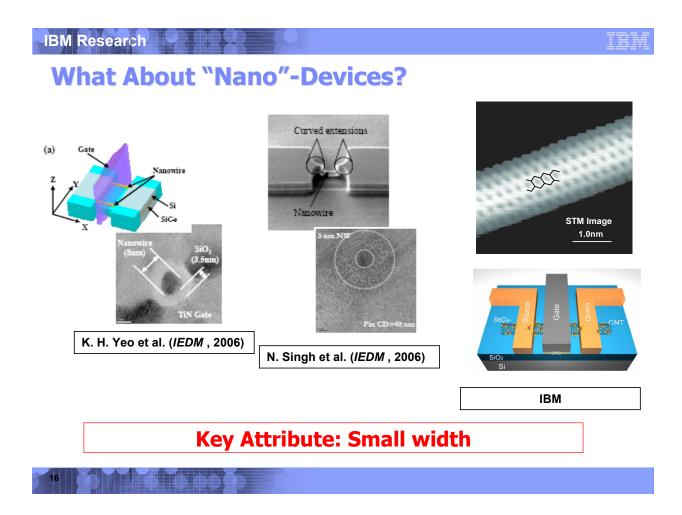

## What About "Nano"-Devices?

IBM

### When Will We Get to Real Nano?

• Key Attribute: Small width

| Node | Minimum W (nm) |

|------|----------------|

| 45   | 70-80          |

| 32   | 50-60          |

| 22   | 35-45          |

| 15   | 25-35          |

| 11   | 16-25          |

| 8    | 10-16          |

| 5    | 7-10           |

Nano-devices by 2020-2025 in production?

17