# Facing the Hot Chip Challenge (Again)

#### Bill Holt General Manager Technology and Manufacturing Group Intel Corporation

Hot Chips 17 August, 2005

# Key Messages

- The driving force behind Moore's Law

- Power has always been a consideration

- Process and design collaboration required to address power challenges

- Technology Advances provide a transistor budget to support innovation

- Efficient Design utilizes transistor budget to deliver product performance

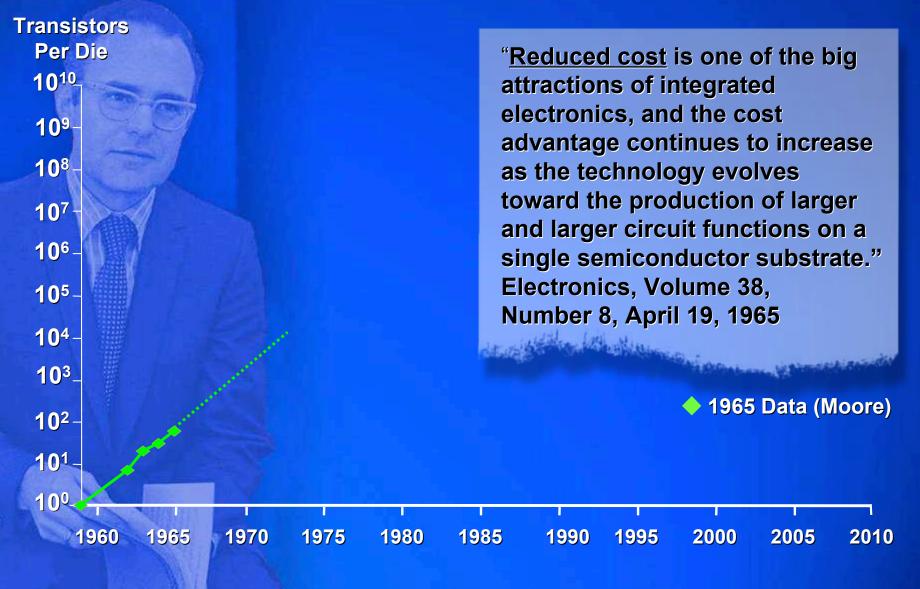

### Moore's Law - 1965

Source: Intel

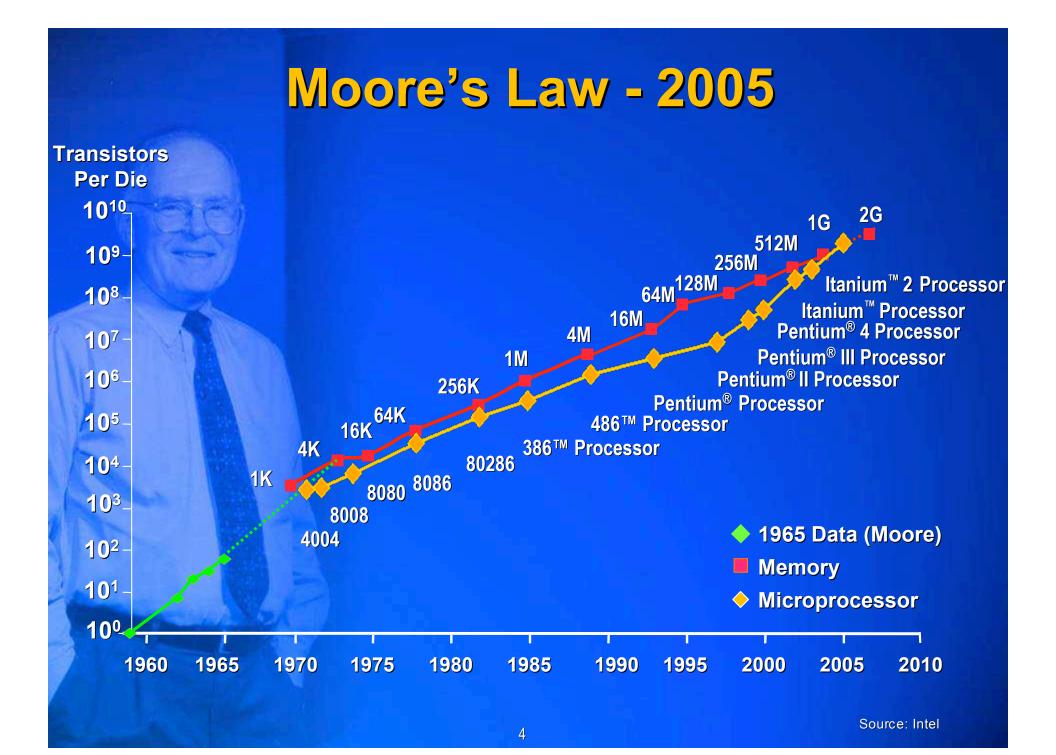

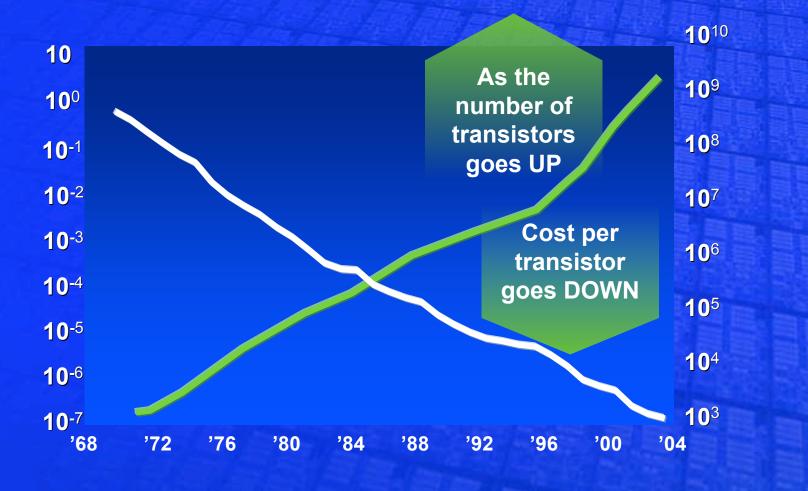

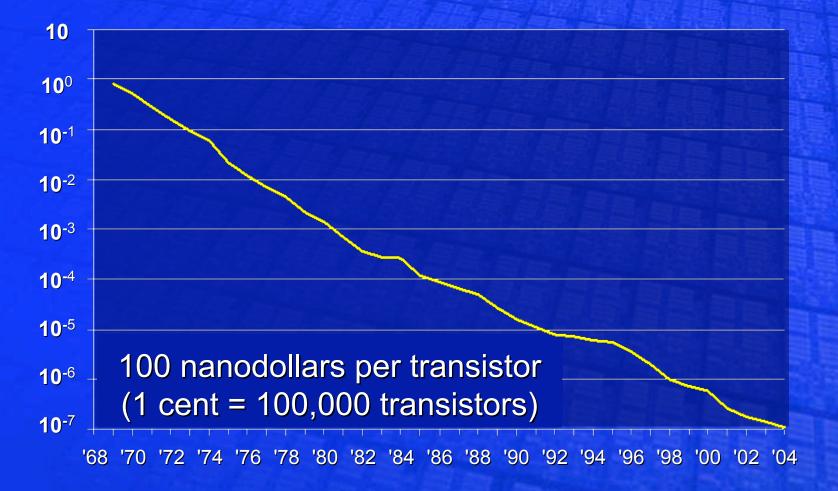

# The Economics of Moore's Law

5

Source: WSTS/Dataquest/Intel

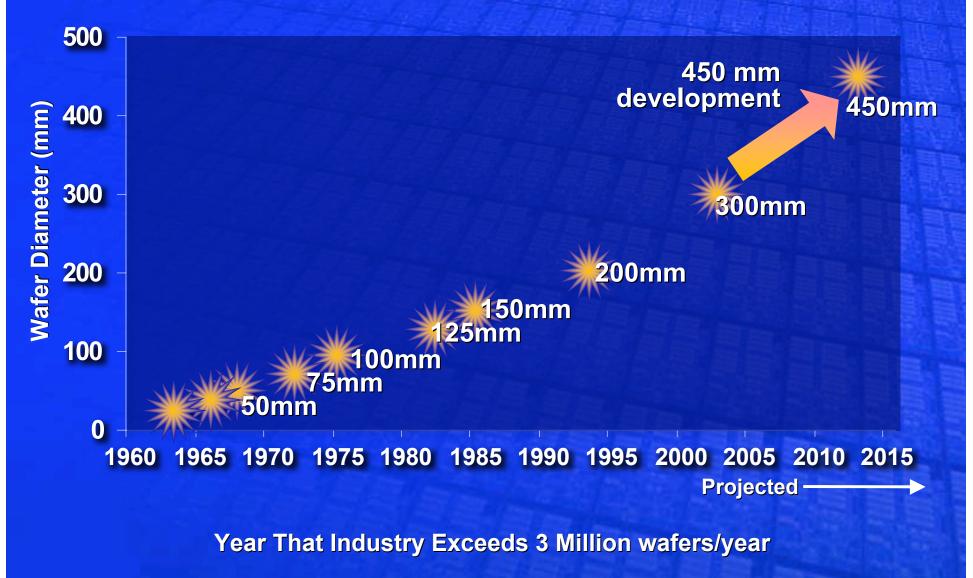

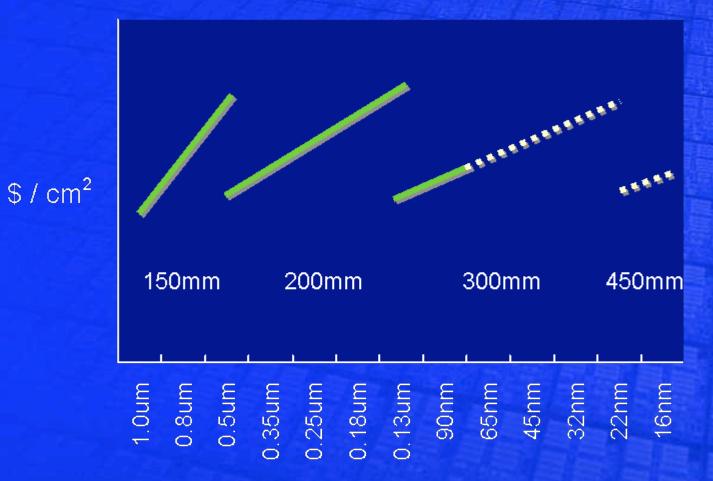

# Wafer Size: Enables Cost Efficiency

Source: VLSIR

#### **Processed Wafer Cost**

Wafer size conversions offset trend of increasing wafer processing cost

Source: Intel

# Moore's Law + Bigger Wafers = Lower Cost/function

Source: WSTS/Intel, 5/05

# Key Messages

- The driving force behind Moore's Law

- Power has always been a consideration

- Process and design collaboration required to address power challenges

- Technology Advances provide a transistor budget to support innovation

- Efficient Design utilizes transistor budget to deliver product performance

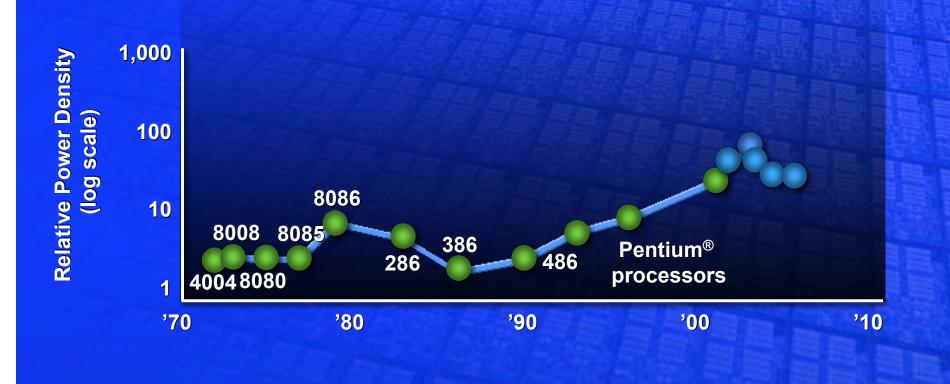

#### Power challenges are neither new nor fundamental

"Will it be possible to remove the heat generated by 10's of thousands of components?"

**G. Moore**, *Cramming more components onto integrated circuits*, Electronics, Volume 38, Number 8, April 19, **1965**

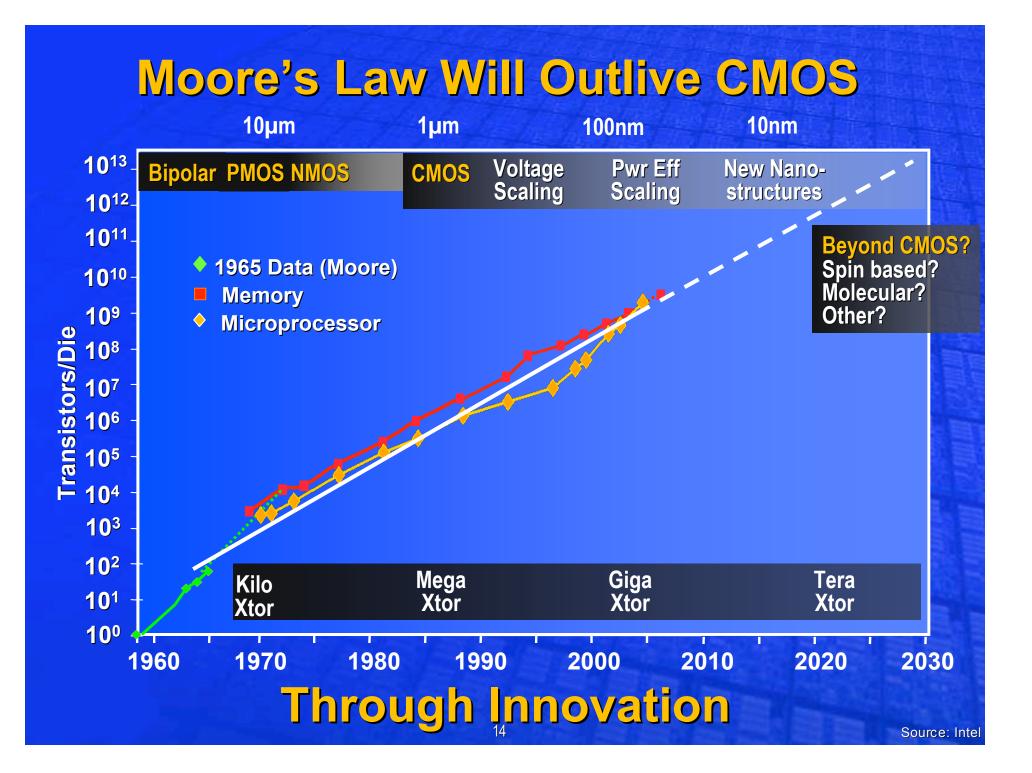

#### Moore's Law Preceded CMOS

"The **power barriers** now facing alternative semiconductor processes indicate that only CMOS will allow chip makers to capitalize on the density that can be achieved with gate arrays and standard cells."

"Once, maybe twice a decade the electronics industry encounters a force that affects not only the way circuits are physically designed but also the way the industry thinks. **CMOS is just such a force**." Silicon Technology has Changed to Increase Power Efficiency

1960's: Bipolar

1970's: PMOS, NMOS

1980's: CMOS

1990's: Voltage scaling (P = CV<sup>2</sup>f)

2000's: Power efficient scaling/design

# Key Messages

- The driving force behind Moore's Law

- Power has always been a consideration

- Process and design collaboration required to address power challenges

- Technology Advances provide a transistor budget to support innovation

- Efficient Design utilizes transistor budget to deliver product performance

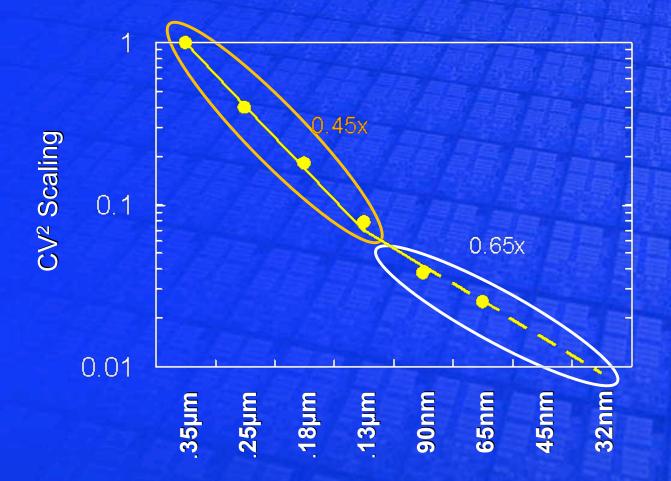

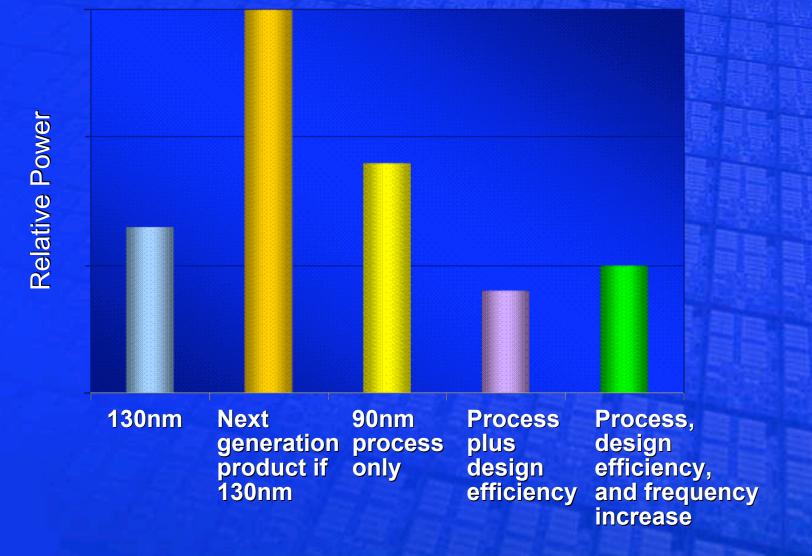

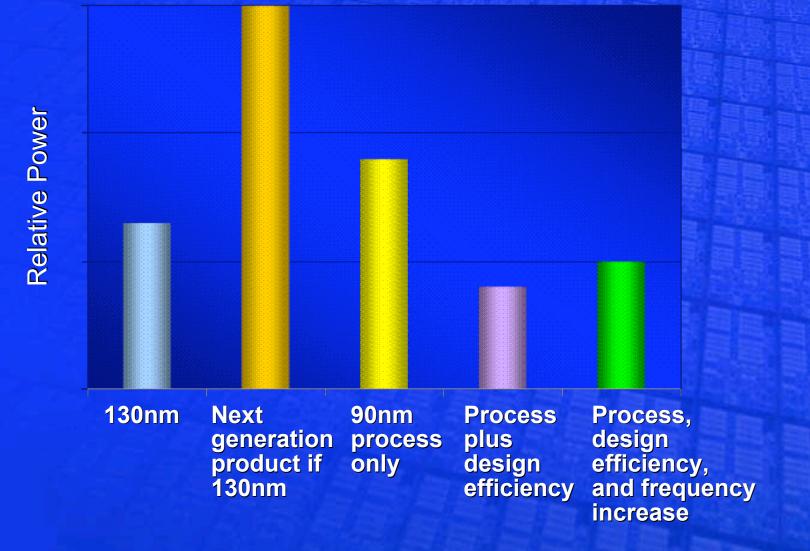

#### **Process Advances Still Scale Power**

but the rate has slowed and collaboration is required

#### Leakage becomes Significant

Power scaling vs. process for the last 10 years (includes frequency increasing with process speed)

17

#### However, Power Density Has Leveled Off

#### Effective Process and Design Collaboration Succeeds in Power Improvements

# Key Messages

- The driving force behind Moore's Law

- Power has always been a consideration

- Process and design collaboration required to address power challenges

- Technology Advances provide a transistor budget to support innovation

- Efficient Design utilizes transistor budget to deliver product performance

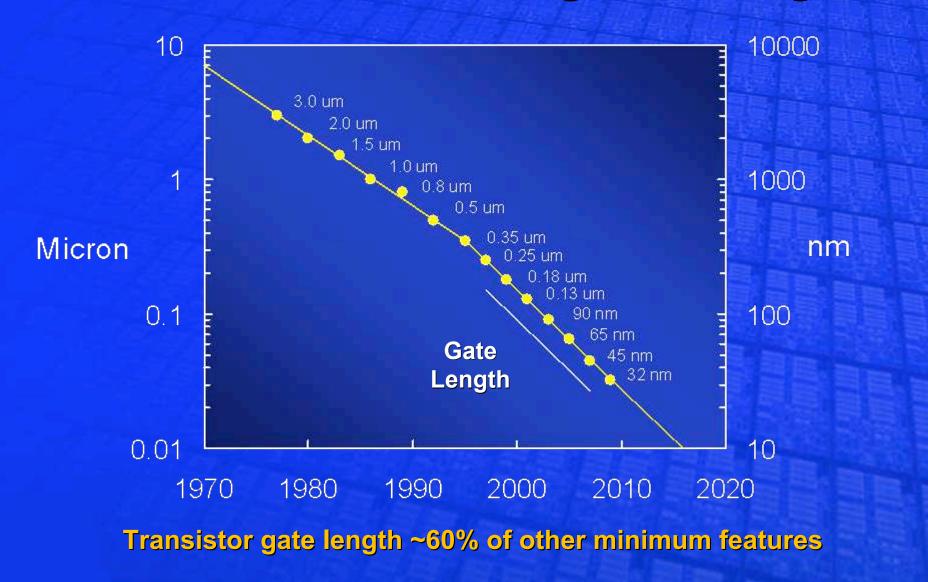

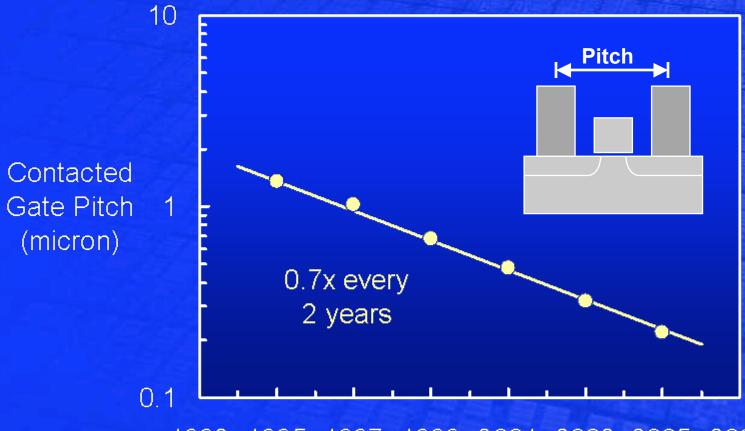

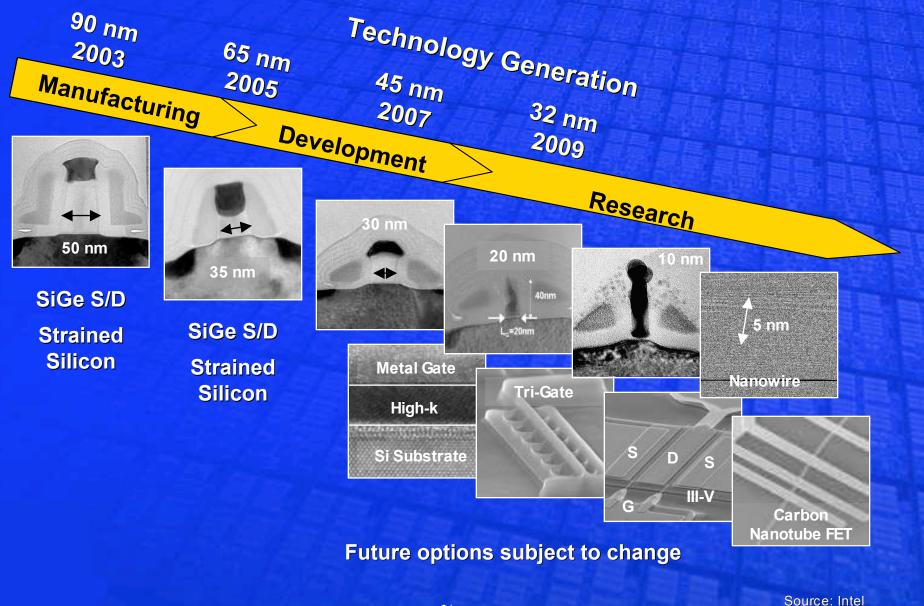

#### Silicon Technology Advances **Feature Size Scaling** 10 10000 3.0 um 2.0 um 1.5 um 1.0 um 1000 0.8 um 0.7x every 0.5 um **3 years** 0.35 um Micron nm 0.25 um 0.18 um 0.13 um 0.1 100 90 nm 0.7x every 65 nm 45 nm 2 years 32 nm 0.01 10

New technology generation every 2 years

2000

2010

2020

1990

1970

1980

## **Transistor Gate Length Scaling**

#### **Key Density Indicator Continues to Scale**

#### 1993 1995 1997 1999 2001 2003 2005 2007

Gate pitch continues to scale 0.7x per generation, providing ~2x transistor density improvements

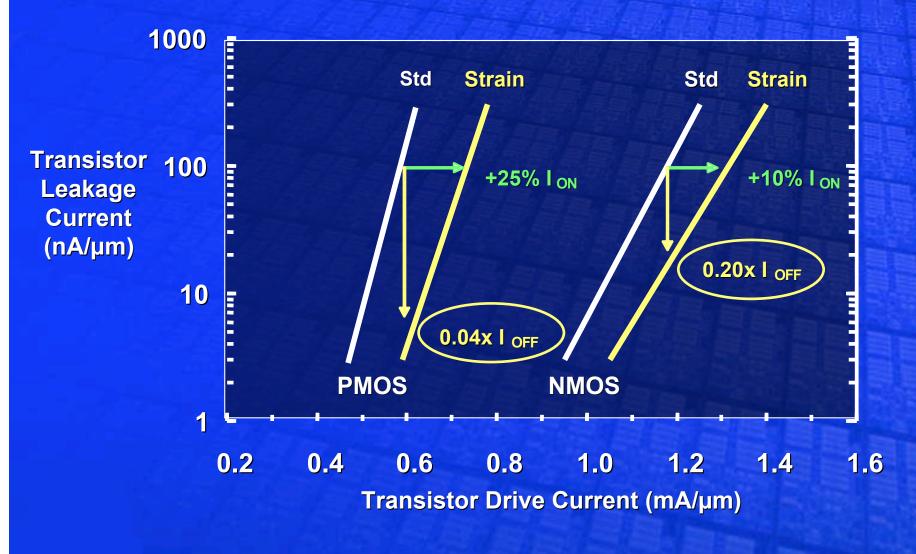

#### Strained Silicon Improves Transistor Performance and Leakage Today

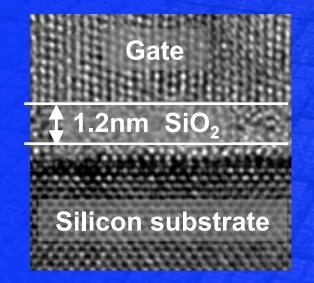

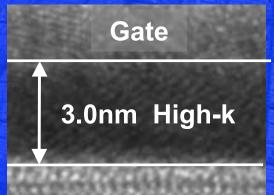

### High-k Dielectric Can Reduce Gate Leakage Tomorrow

Silicon substrate

|                            | High-k vs. SiO <sub>2</sub> | Benefit            |

|----------------------------|-----------------------------|--------------------|

| Gate capacitance           | 60% greater                 | Faster transistors |

| Gate dielectric<br>leakage | > 100x reduction            | Lower power        |

**Process integration is the key challenge**

Source: Intel

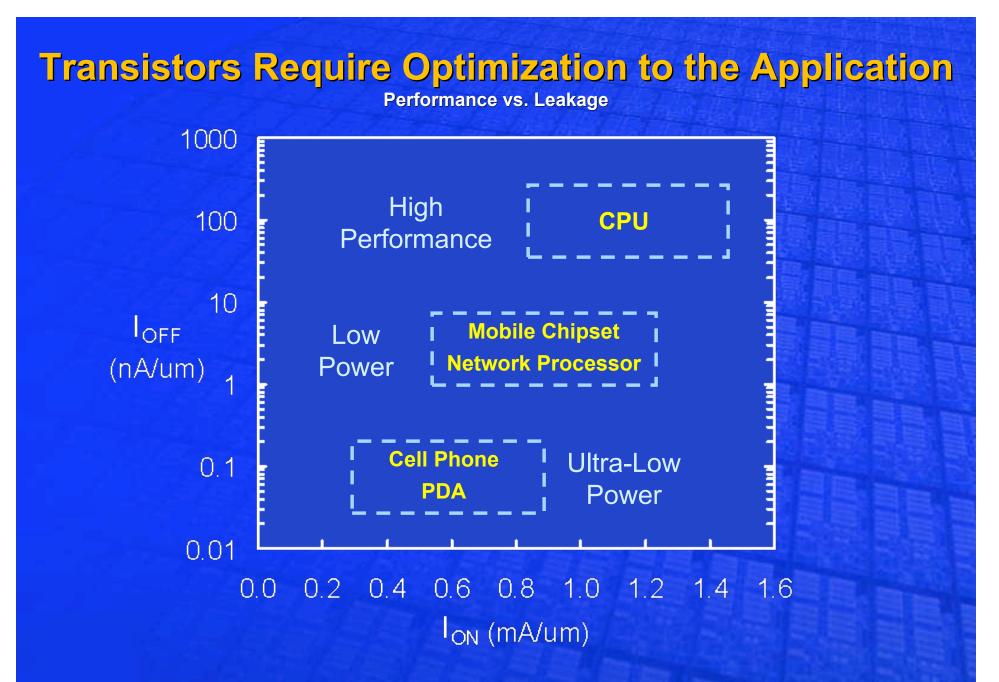

**Optimized transistors can provide ~1000x lower leakage**

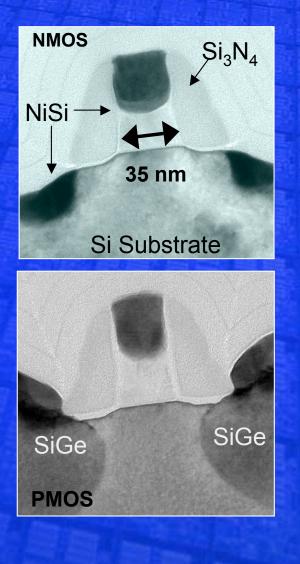

### **65 nm Generation Transistors Today**

- 35 nm gate length

- 1.2 nm gate oxide

- 220 nm gate pitch

- NiSi for low resistance

- 2<sup>ND</sup> generation strained silicon for enhanced performance/power

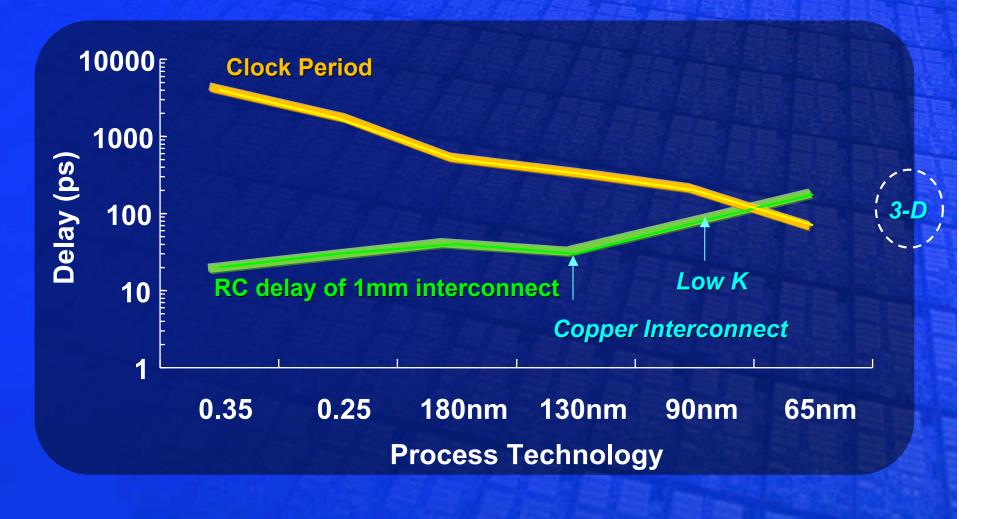

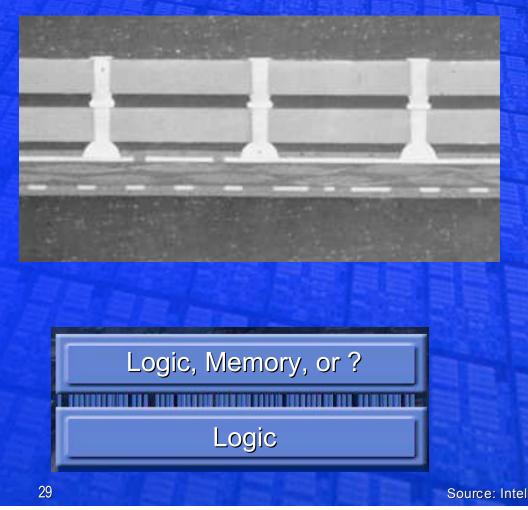

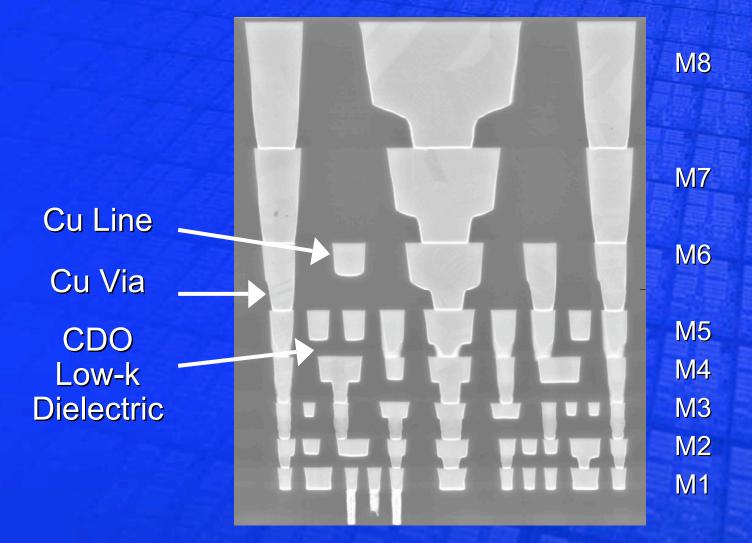

#### Innovations Required to Reduce Interconnect RC Challenges

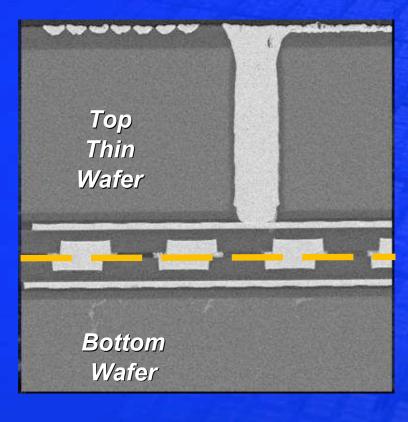

# 3D Silicon Stacking Wafer Die

#### **65 nm Generation Interconnects**

# Innovation-Enabled Pipeline in Place

# Key Messages

- The driving force behind Moore's Law

- Power has always been a consideration

- Process and design collaboration required to address power challenges

- Technology Advances provide a transistor budget to support innovation

- Efficient Design utilizes transistor budget to deliver product performance

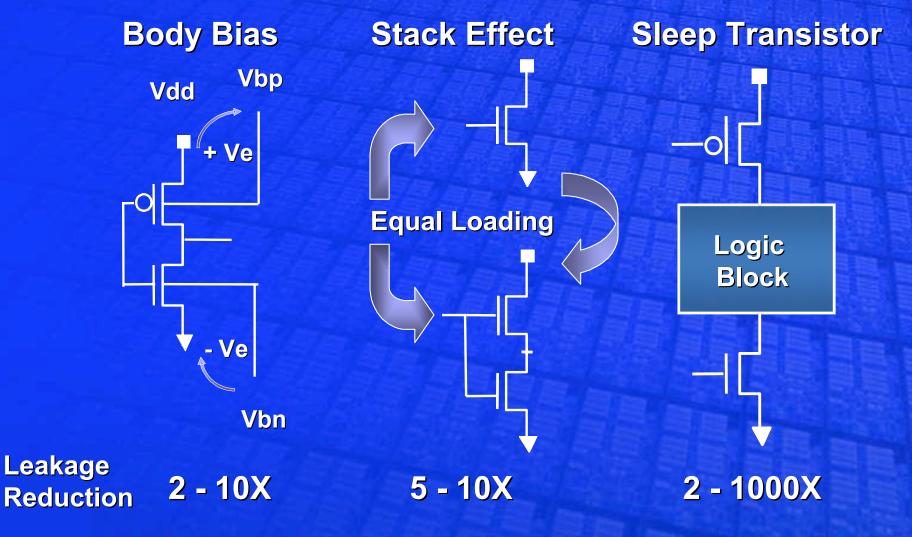

#### **Power Reduction Techniques**

- Optimum Design

- Leakage Control

- Active Power Reduction

- Increase On-die Memory

- Multi-threading

- Dual Core and Multi-core

- Special Purpose Hardware

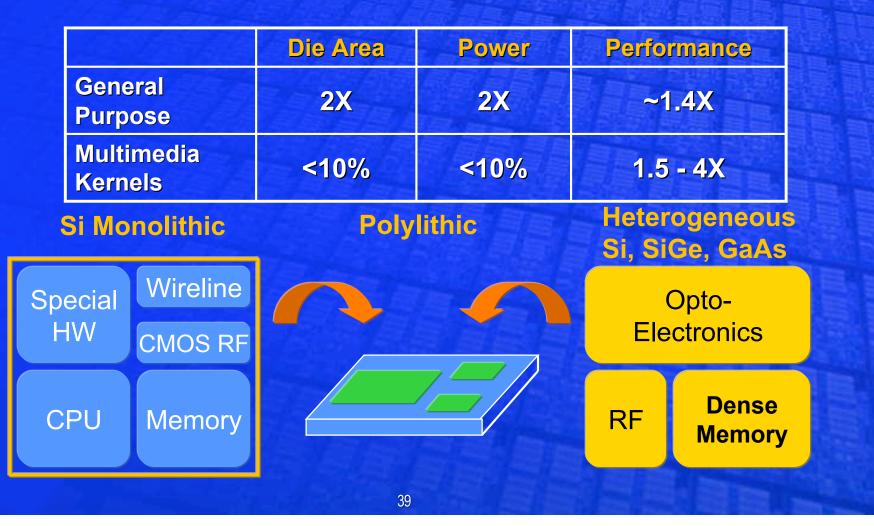

- Function Integration through SOC/SIP

# Circuit Techniques Reduce Source Drain Leakage

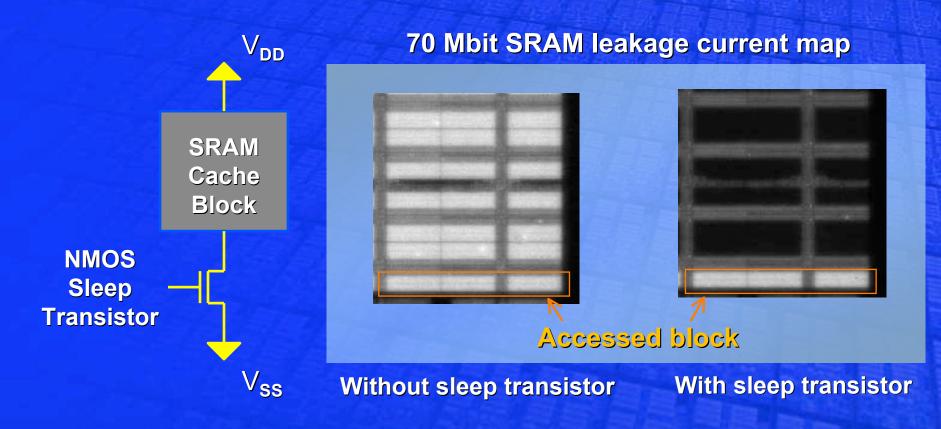

## Sleep Transistor Reduces SRAM Leakage Power

>3x SRAM leakage reduction on inactive blocks

Source: Intel

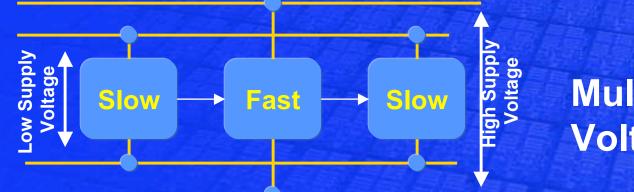

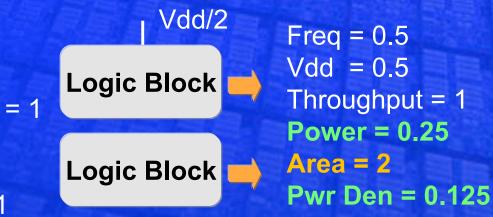

#### **Active Power Reduction**

#### Multiple Supply Voltages

**Replicated Designs**

Freq = 1 Vdd = 1 Throughput = 1 Power = 1 Area = 1 Pwr Den = 1

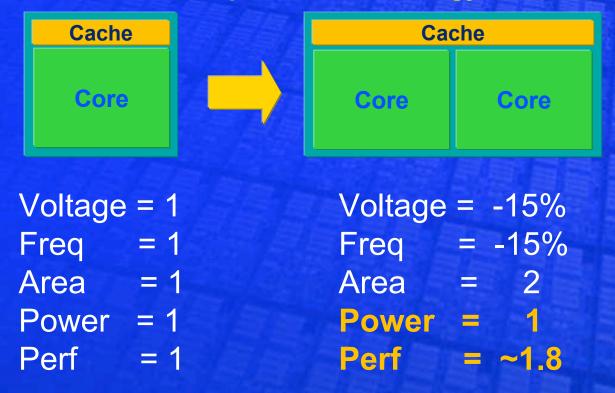

#### Dual Core

Rule of thumb

| Voltage | Frequency | Power | Performance |

|---------|-----------|-------|-------------|

| 1%      | 1%        | 3%    | 0.66%       |

In the same process technology...

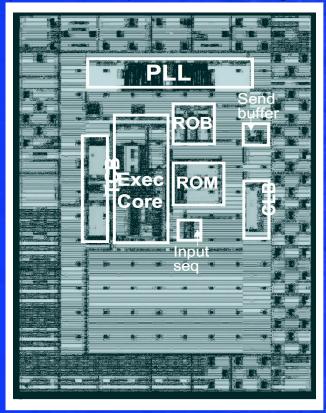

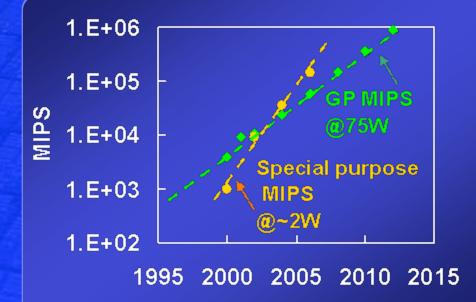

#### **Special Purpose Hardware**

#### Special Purpose HW Engine

2.23 mm x 3.54 mm, 260K transistors

Opportunities: MPEG Encode/Decode Speech recognition Graphics

Special purpose HW—Best Mips/Watt

#### Value of Integration

- Special-purpose hardware -> more MIPS/mm<sup>2</sup>

- SIMD integer and FP instructions in several ISAs

### Joint Power Reduction Technology Roadmap

| Process<br>Technology  | Dual Vt<br>Copper                                         | Dual Vt (Le)<br>Strain engineering<br>Low K ILD                                | FinFET (Tri-<br>Gate)<br>Metal Gate<br>3D |

|------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|

| Circuits and<br>Design | Sizing<br>Clock gating                                    | Sleep transisto<br>Stack effect<br>Multiple supply<br>Body Bias                |                                           |

| Micro-<br>Architecture | Shallower<br>pipelines<br>Large caches<br>Multi-threading | Multi-threaded Multi-core<br>Increasing multi-processing<br>Special purpose HW |                                           |

Future options subject to change

#### Effective Process and Design Collaboration Succeeds in Power Improvements

## ... and it works

|                             | 130 nm         | 90 nm            |  |

|-----------------------------|----------------|------------------|--|

|                             | <u>Madison</u> | <u>Montecito</u> |  |

| Cores/Threads               | 1/1            | 2/4              |  |

| Transistors                 | 0.41           | 1.72 Billion     |  |

| L3 Cache                    | 6              | 24 MByte         |  |

| Frequency                   | 1.5            | >1.7 GHz         |  |

| <b>Relative Performance</b> | 1              | >1.5x            |  |

| Thermal Design Power        | 130            | ~100 Watt        |  |

## Conclusions

- Economics is driving force behind Moore's Law

- Power has always been a consideration

- Process and design collaboration required to address power challenges

- Technology Advances provide a transistor budget to support innovation

- Efficient Design utilizes transistor budget to deliver product performance