## output Adaptive Packet Processor (oAPP)

Olivia Wu Nikhil Jayaram

www.procket.com

## oAPP – output Adaptive Packet Processor

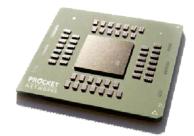

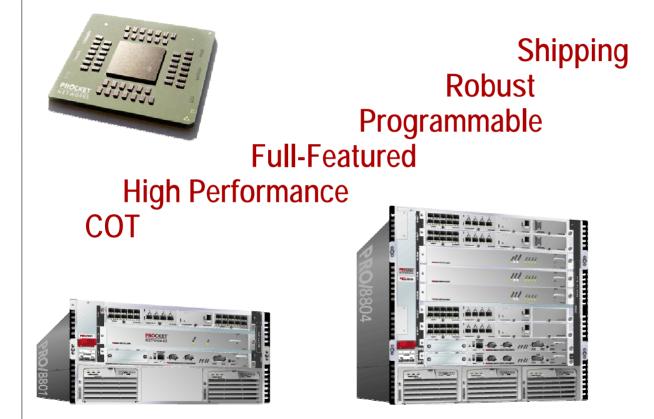

## oAPP – Shipping in PRO/8000 series

## oAPP – Agenda

## oAPP

- Features

- Top-Level

- Blocks

- Design challenges

- Design flow

- Q&A

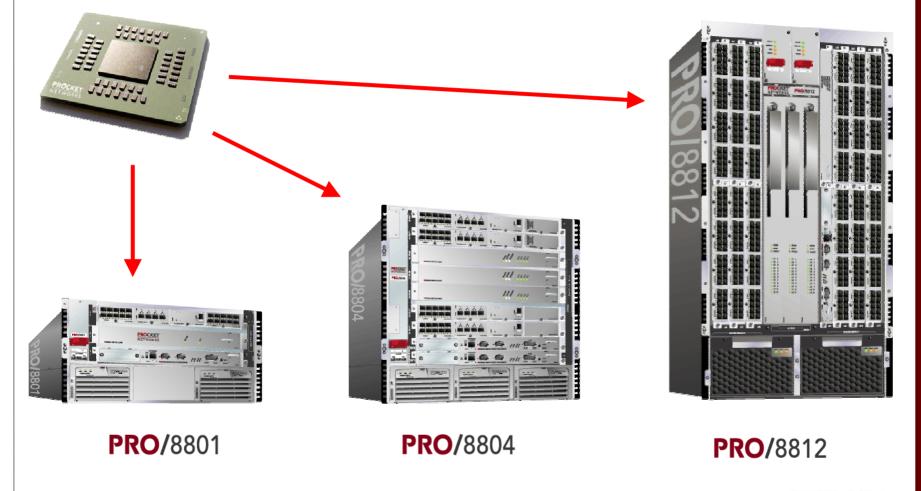

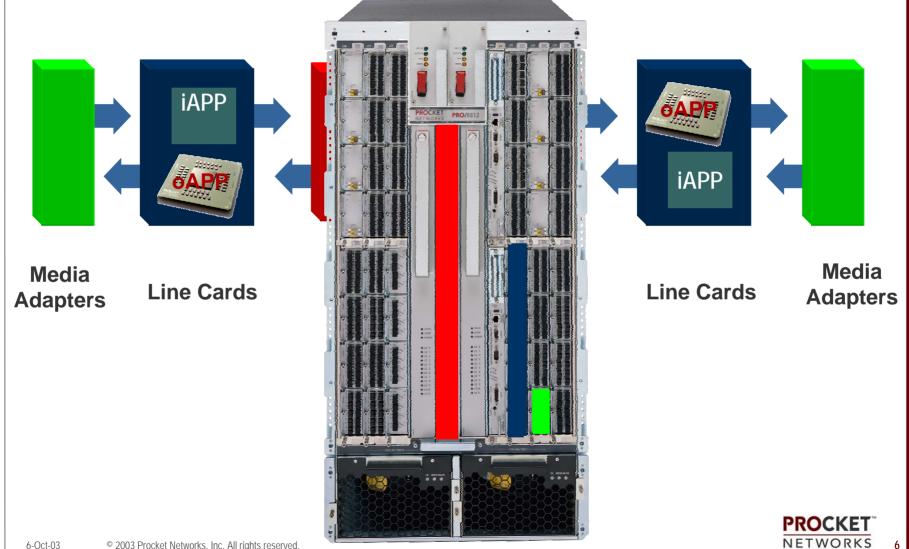

### PRO/8812

- System

- Architecture

- Key concepts

## PRO/8812 – System

## PRO/8812 – Architecture

6

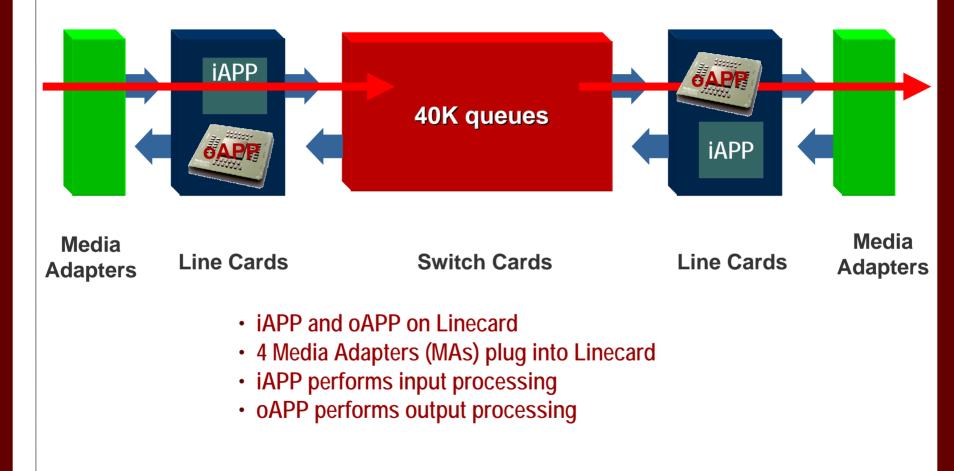

## PRO/8812 – Architecture

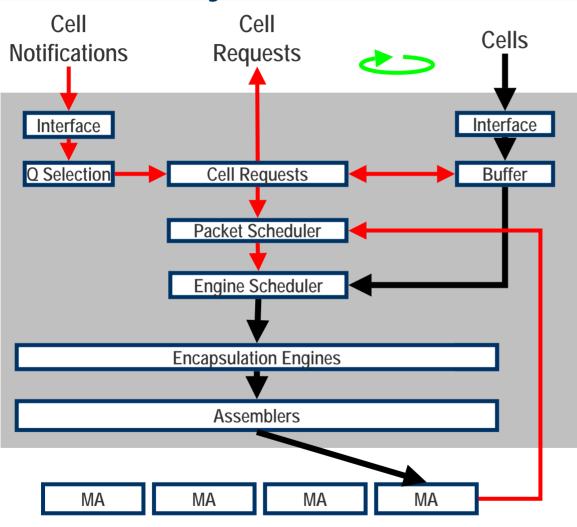

## oAPP

## High performance

- 40 Gbps

- Non-blocking

- Traffic Management

- Encapsulation

## **Fully featured**

- Shaping

- Accounting

- *QoS*

- Multicast

- Fragmentation

#### Programmable

- QoS

- Encapsulation

## CAPP?

## Robust

- *OIR*

- BIST

- ECC/parity

- CRC24

## **Design challenges**

## oAPP – High Performance

9

## oAPP – Fully Featured

## oAPP – Fully Featured

#### Accounting

- Precise packets and bytes

- Per port

- RED drops

- Metering drops

- Multicast replication

- Fragmentation

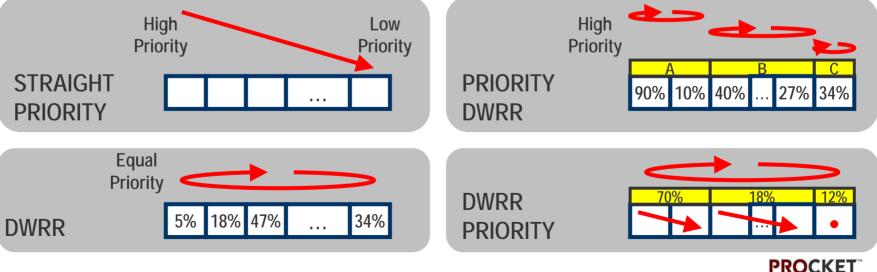

## oAPP Programmable – Queue Selection

- Queue and group-queue rate-shaping

- Selectable per interface

- Disciplines currently programmed:

NETWORKS

## oAPP Programmable – Encapsulation Engines

## Multiple Encapsulation Engines

- Fully programmable

- Easily add new encapsulations

## Encapsulation engine

- Modifies packet

- L2 encapsulation

- Physical port identifier

- Send cells to Assembler

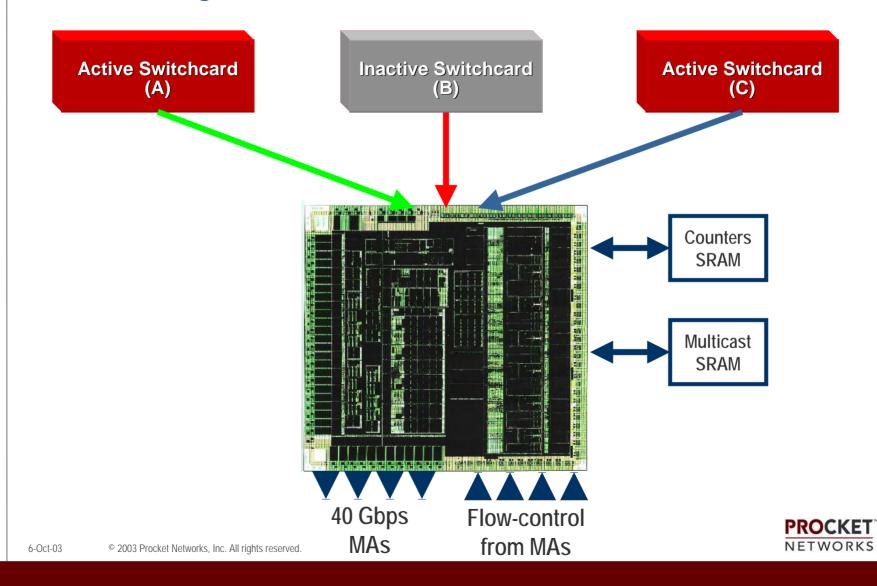

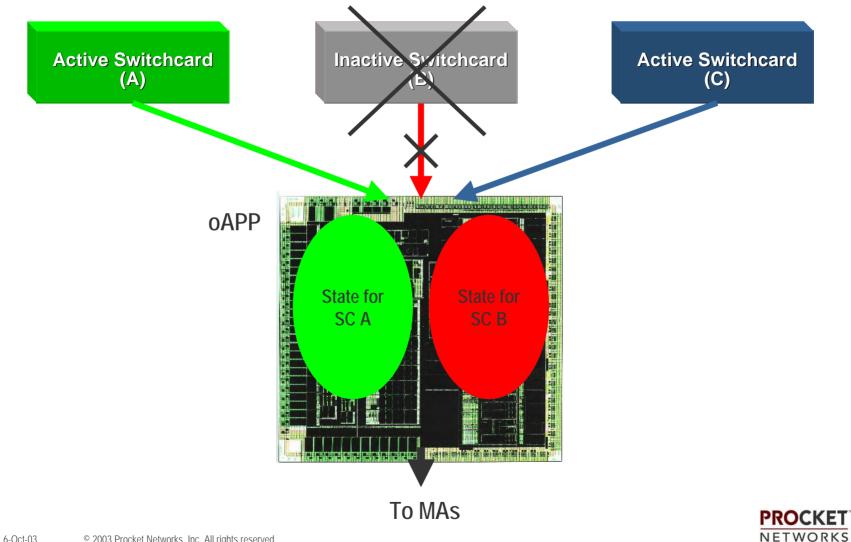

## oAPP Robustness – Switchcard Failover

## oAPP Robustness – Reliability

### • ECC/parity

- On-chip SRAM

- Off-chip SRAM

- BIST & repair

- End-to-end packet CRC-24

- Inter-chip

- CRC

- Parity

- ECC

## Internal consistency checks

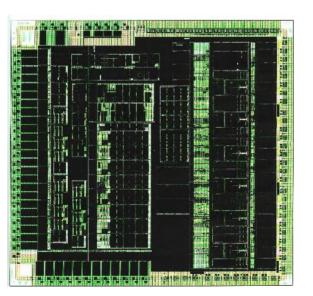

## oAPP Design Challenges

#### Speed

- 40Gbps

- 100+ Mpps

- 350 MHz

- 0.18um copper CMOS

- Scale

- Programmable engines

- 950KBytes SRAM

- 137M transistors

- 425 sq mm

#### Analog

- 170 2.5 GHz serial links

- Multiple clock domains

- Power

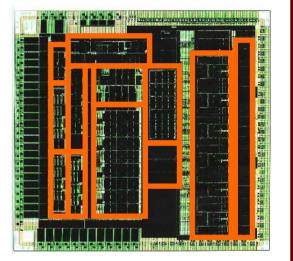

## oAPP Design Challenges – ASIC

#### Speed

- 40Gbps

- 100+ Mpps

- 350 MHz

- 0.18um copper CMOS

#### Scale

- Programmable engines

- 950KBytes SRAM

- 137M transistors

- 425 sq mm

#### Analog

- 170 2.5 GHz serial links

- Multiple clock domains

- Power

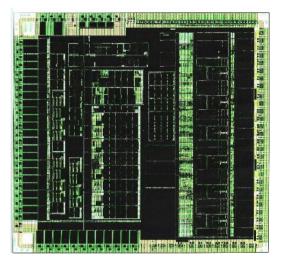

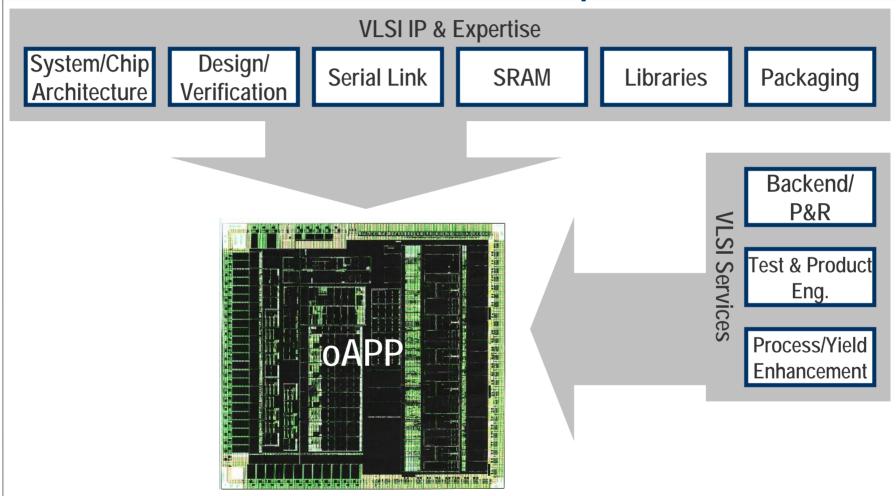

## oAPP Design Challenges – COT

#### • Speed

- 40Gbps

- 100+ Mpps

- 350 MHz

- 0.18um copper CMOS

#### Scale

- Programmable engines

- 950KBytes SRAM

- 137M transistors

- 425 sq mm

#### Analog

- 170 2.5 GHz serial links

- Multiple clock domains

- Power efficient

## oAPP Design Challenges – COT

## oAPP – Summary

**PRO/**8804

**PRO/**8812

**PRO/**8801

## PROCKET<sup>M</sup> NETWORKS

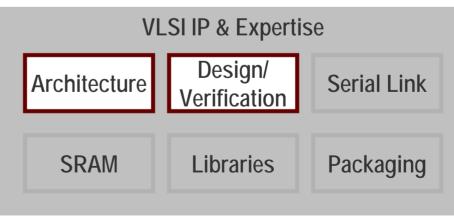

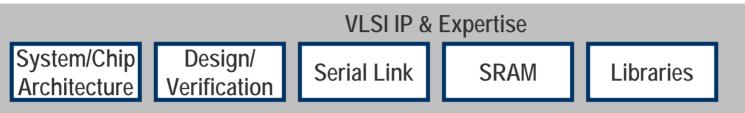

**VLSI IP & Expertise**

System/Chip Architecture

Design/ Verification

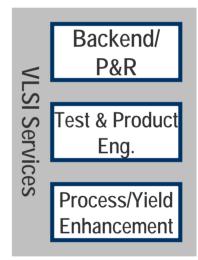

# **VLSI** Services

## 2.5 GHZ Serial Links in 0.18 and 0.13 um

- Source synchronous

- very low BER

- 48 inches backplane trace + 2 connectors

- Multilink bundling

- Low power (<200mW in 0.18 um)

- oAPP has 170 links other Procket chips more than 250

| <   |  |

|-----|--|

|     |  |

| S   |  |

|     |  |

| S   |  |

| er  |  |

| <   |  |

| Vic |  |

| ces |  |

| S   |  |

## High-performance embedded SRAM

- Creation of any configuration

- 500MHz designs achieved in 0.18

- 2-port and 4-port

- *Row/column redundancy*

- RAMBist design for test and reliability

| <        |

|----------|

|          |

| <u>I</u> |

| S        |

| er       |

| $\leq$   |

|          |

| ces      |

## Standard-Cell and IO Library Design

- *High speed/low power FFs*

- Automated RTL to I/O Frame generation

- Proprietary clock distribution

- reduced power and clock skew

VLSI Services

#### Packaging

- Flip-Chip CGA, HITCE glass ceramic

- 16 GHz bandwidth

- 58 mm. Body size

- 20 layers

- HiTCE improves reliability

- In-house automated design

**VLSI Services**

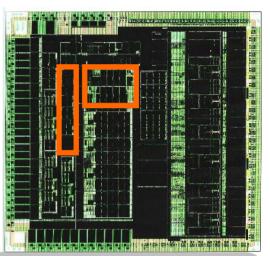

## Backend/P&R:

- Customize around standard tools

- Internal development where necessary

- Custom clock distribution

- RTL freeze to GDS TO in 2 weeks!

- ECO acceptance 2 days before GDS TO

| Backend/<br>P&R | ] |

|-----------------|---|

|                 |   |

|                 |   |

|                 |   |

## **Test & Product Engineering**

- DFT methodology

- Highest test and fault coverage

- High speed tests at wafer and module

- Process

- Automated test vector translation

- VLSI and product qualification

- Burn-in and ESD tests

- Delay and transition fault speed sorting

| ۷L           | Backend/<br>P&R        |

|--------------|------------------------|

| LSI Services | Test & Product<br>Eng. |

#### **Process/Yield Enhancement**

- Yield calculation/enhancement and FA

- Tune process

- Bit mapping and analysis of all RAMs

- Process/speed monitoring

- Data correlation

- Yield tracing

## oAPP – Procket VLSI COT Development

## PROCKET<sup>M</sup> NETWORKS