#### Vitesse Network Processors (Sitera's PRISM IQ2000 NPU Family)

#### Optimizing Architecture for Bandwidth and Flexibility

#### Authors:

Steve Sheafor Cindy Lindsay

#### **Presenter:**

Steve Sheafor, Ph. D., VP of Technology

steve.sheafor@vitesse.com

Vitesse Semiconductor Corporation Advanced Networking Products Division

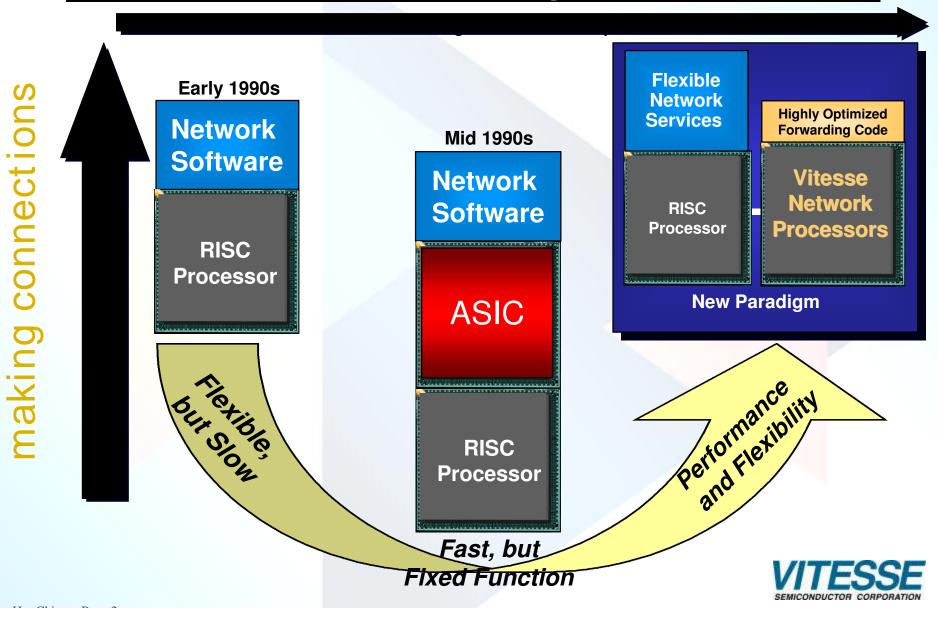

# Why Network Processors (NPUs) are Hot Chips

### **NPU-based System Solutions**

# **NPU Design Objectives**

Provide the customer with the ability to differentiate their products in the market

#### Flexibility for a Wide Variety of Network Applications

- Fully Programmable

- Simple System Connectivity

#### Cost Effective

- High Performance based on Efficient CPU utilization

- Minimized System Components

- Low Power Consumption

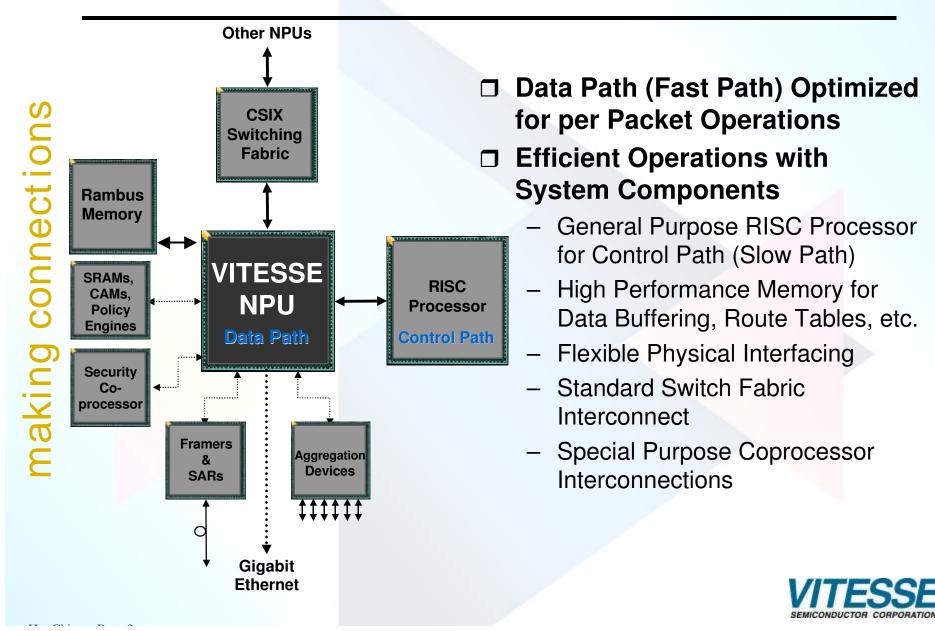

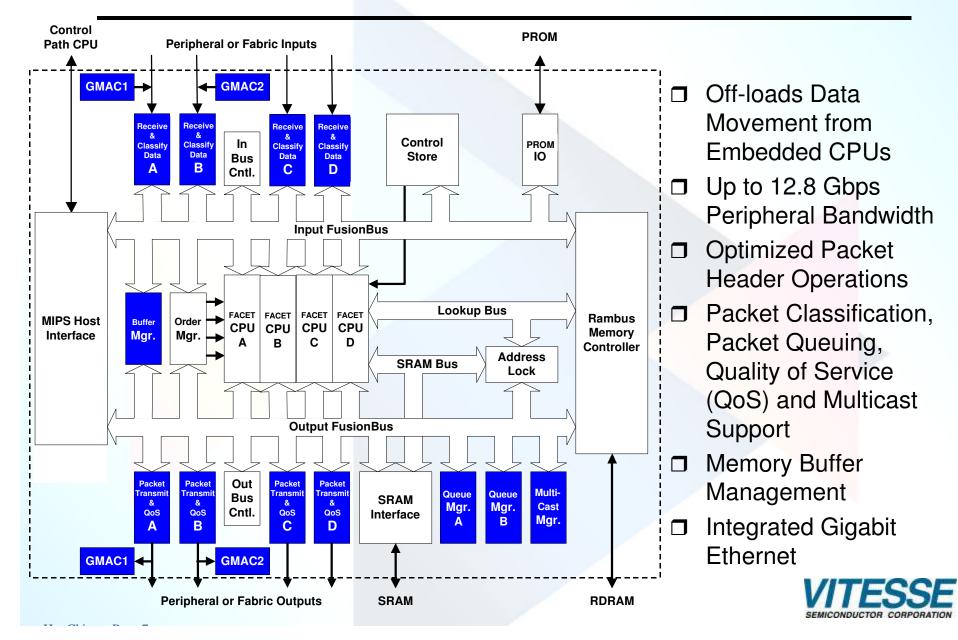

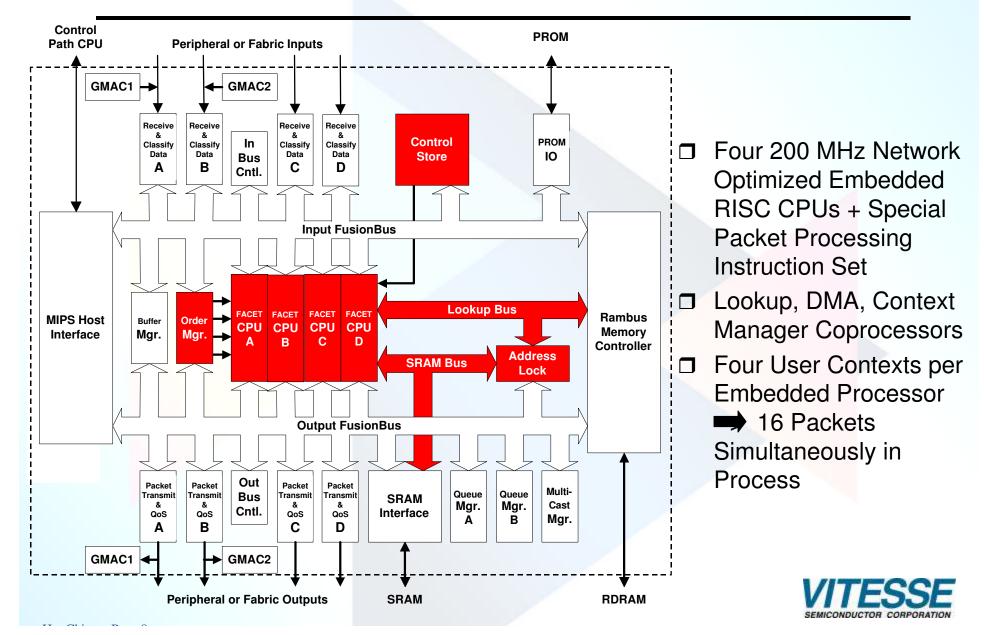

### **Vitesse NPU Block Diagram**

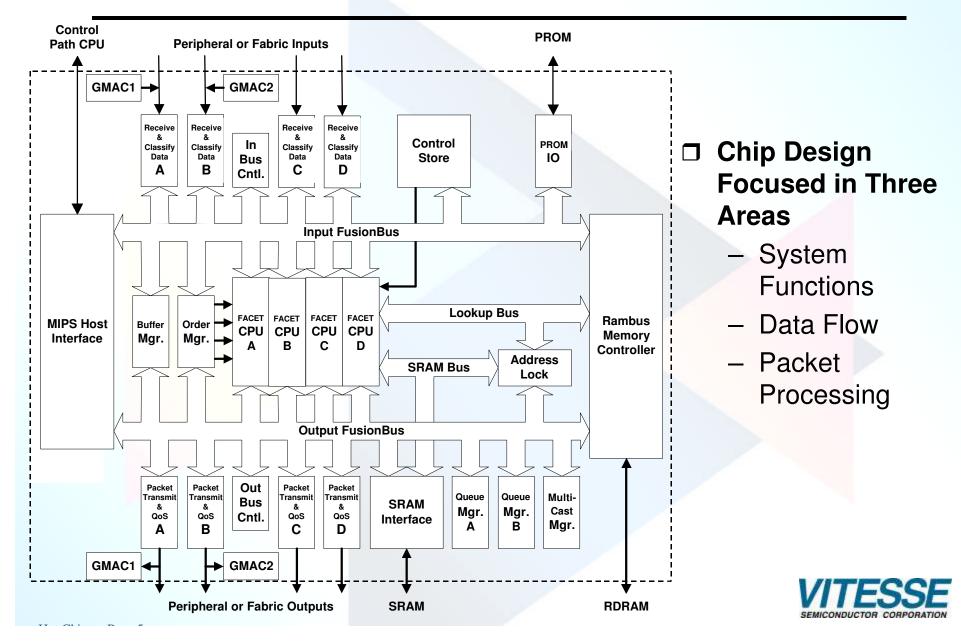

# **NPU System Functions**

- 25.6 Gbps Internal Bandwidth

- ☐ Modular FusionBus<sup>™</sup> Technology

- □ Low Cost Rambus<sup>™</sup> Dynamic Memory -12.8 Gbps

- Memory Controller supports 14 outstanding memory transactions

- Flexible RISC CPU Interface

- High Performance or Low Cost

- Optional SRAM I/F

### **NPU Data Flow Functions**

#### **Packet Processing Functions**

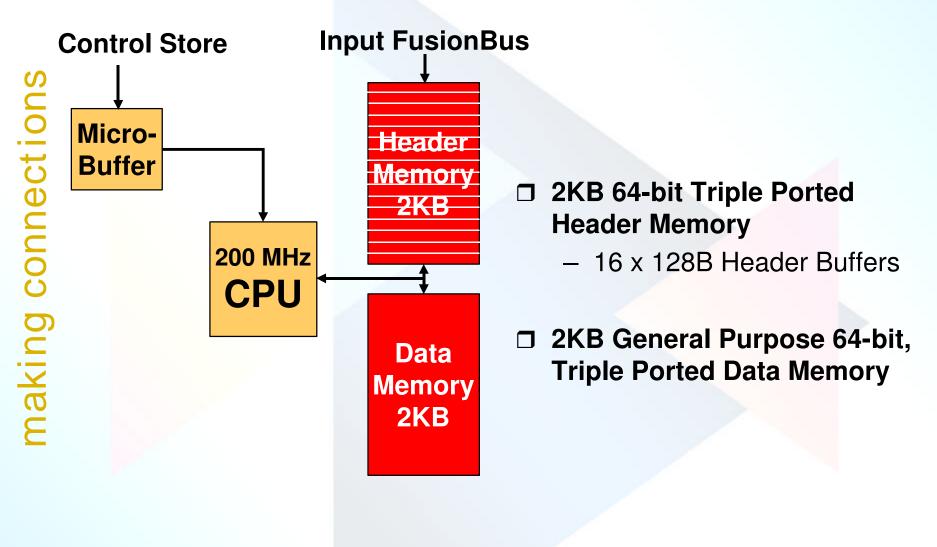

- □ 32-bit RISC Processor

- 64-bit Memory Access

- □ 16 Instruction MicroBuffer

- NPU Instruction Extensions

### **Network Optimized Instructions**

#### □ Classes of Special Instructions

- Bit Test

- Byte Test

- Field Extract

- Enhanced Immediates

- Double Load/Store

- Special Arithmetic (16-bit 1's complement)

#### Vitesse's Implementation of an RFC 1812-compliant Router

- 50% of the implemented instructions are NPU special instructions

- Special instructions are ~3 times as efficient as standard RISC instructions

- Multi-processor and Multi-Threaded Hardware for Performance Optimization

- Single Threaded Software for Ease of Programming

- Example Code

| RXR             | R3,R4      |

|-----------------|------------|

| ORUI<br>TRAPQNE | R5, 0x0040 |

//Start a DMA transfer

(possible context switch if DMA queue full)

//Set a flag

//Check for result available

(context switch on no results available)

naking connections

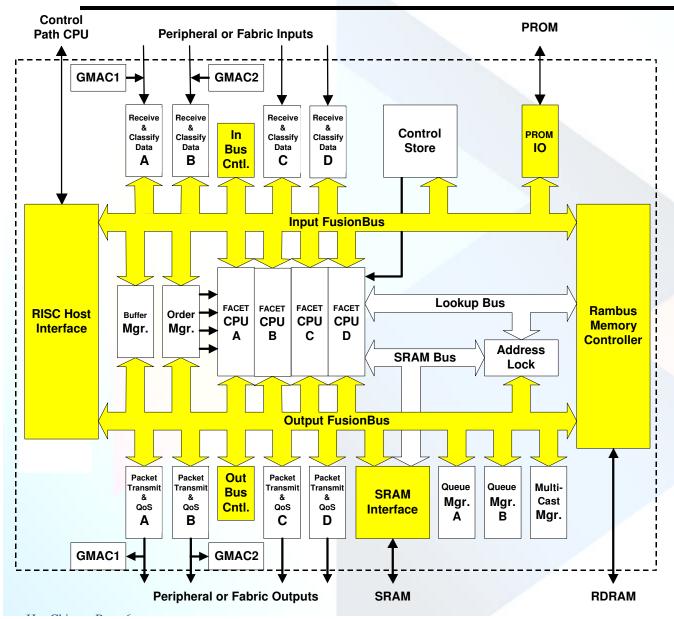

- Customers Continue to Demand the Acceleration of Bandwidth and the Flexibility, which allows them to Deliver a Wide Variety of Connectivity and Services

- Process Technology Advancements Enables More Transistors

- Vitesse's Modular Architecture for System-on-Chip Design Makes It Easy to Enhance Performance and Features

- More Processors for Raw Performance

- More Peripheral Interfaces for Data Throughput

- More Memory Bandwidth for Support of Services

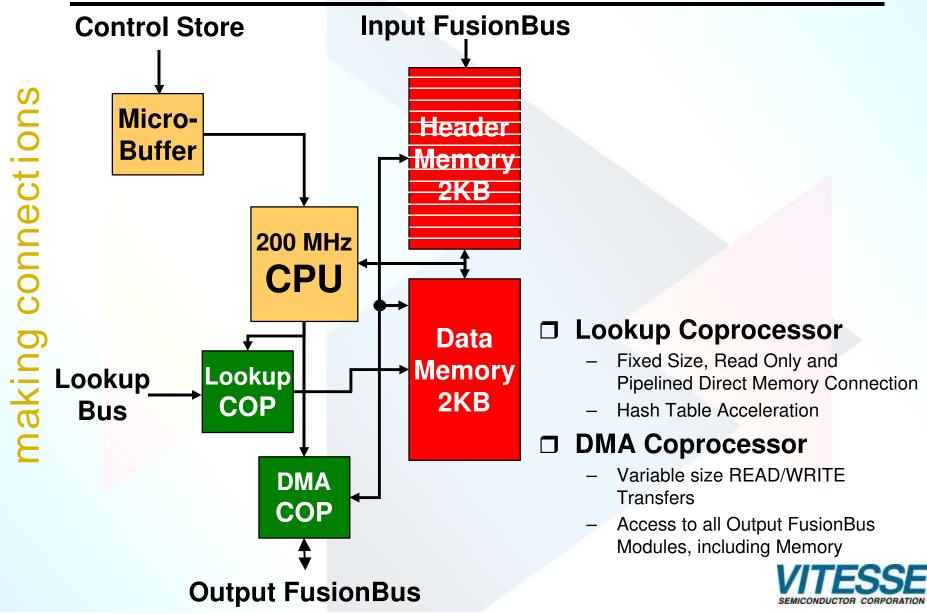

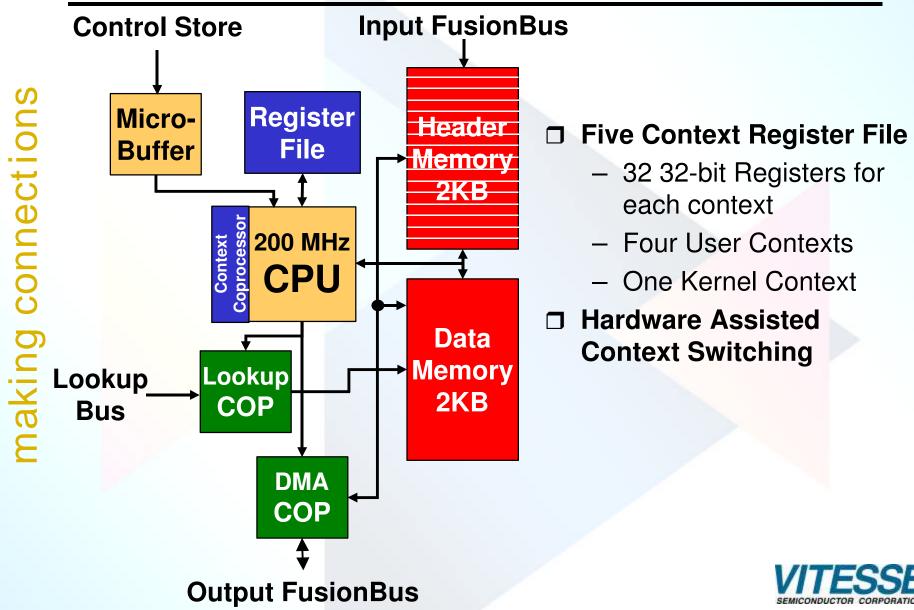

- Additional Special Purpose Coprocessors for Advanced Features