# Advanced Programmable Interrupt Controller (APIC)

Architecture

PK Nizar Intel Corporation

Page 1

# intel.

#### **AGENDA**

- Limitations of Current Interrupt Management Solutions

- \* APIC Architecture Overview

- \* APIC Features Benifits Summary

- HOT CHIPS

#### LIMITATIONS OF CURRENT INTERRUPT SOLUTIONS

Interrupt Controller Access (SPL()) by OS is Major Hot Spot

#### LIMITATIONS OF 8259A INCREASE S/W OVERHEAD

- \* Priority / IRQ Bindings Fixed

- \* One Interrupt per Priority

- \* S/W Workaround Prioritization by Early EOI, Explicit masking

- \* Increased Overhead

- \* Slow Access in I/O Space

- Mask Updates ------5.3 usec 7 or 33m 112 Interrupt Vector Fetch -----3 usec EOI Cycles ------3.1 usec

- Timing Loops -----5 -10 usec

- HOT CHIPS

Page 3

**APIC ARCHITECTURE OVERVIEW**

HOT CHIPS

intel.

#### APIC ARCHITECTURE SUMMARY

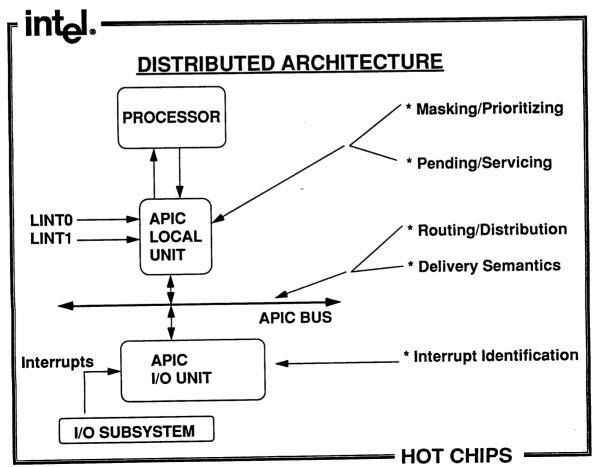

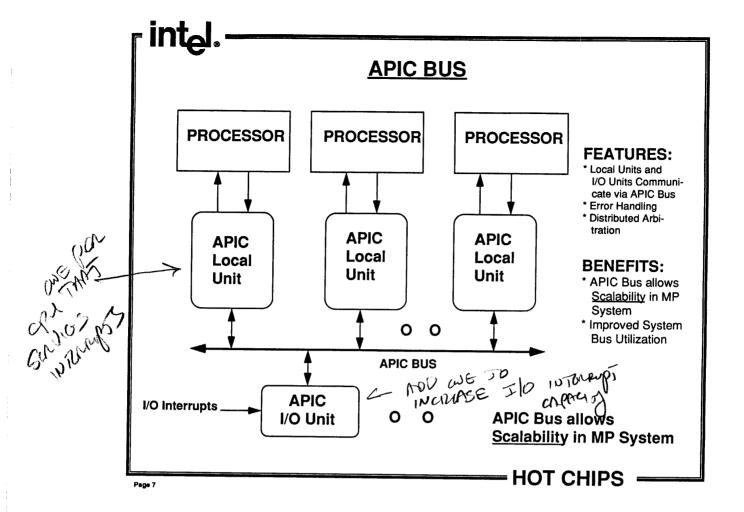

- \* Distributed Architecture

- \* Dedicated Interrupt Communications Bus

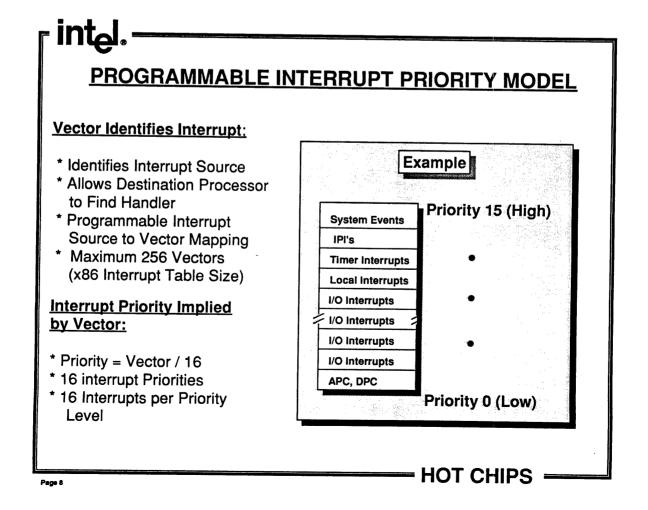

- \* Programmable Interrupt Priority Model

- \* High Performance Priority Management

- \* MP Interrupt Management

HOT CHIPS

Page 6

#### HIGH PERFORMANCE PRIORITY MANAGEMENT

- \* APIC MAINTAINS TWO PROCESSOR PRIORITY INDICATIONS

- TASK PRIORITY

- \* Tracks OS Defined Task/Process/Thread Priority

- \* Updated by Writes to Local APIC's Task Priority Register

- Task Switch

- Task Priority Changes (e.g. SPL ())

- INTERRUPT HANDLER PRIORITY

- \* Equal to Priority of Highest In-Service Interrupt

- \* Handler Can Explicitly Raise/Restore Priority via Task Priority Register

- \* APIC Tracks Handler Priority Across Interrupt Nesting/Unnesting

- \* CURRENT PROCESSOR PRIORITY IS MAXIMUM OF THESE TWO

- HOT CHIPS -

Page 9

## intel.

#### HIGH PERFORMANCE PRIORITY MANAGEMENT

- \* APIC masks all Interrupts Lower or Equal to the Current Priority Level

- Memory Mapped Task Priority Register

- \* Useful for Synchronized Access of Shared Resources in OS

- \* Provides Mutual Exclusion

- \* Faster SPL () / R/LQL () Routines

HOT CHIPS

#### MP INTERRUPT MANAGEMENT

- \* Fully Symmetric, Static/Dynamic Interrupt Distribution

- \* Group Broadcast, Fixed or Lowest Priority

- \* Focus Processor concept

- \* Logical or Physical Addressing

- \* Flexible Inter-Processor interrupts

- \* Supports Tasks Migration and Interrupt forwarding

Page 11

HOT CHIPS

### **APIC FEATURES BENEFITS SUMMARY**

| Features                          | Benefits                                       |

|-----------------------------------|------------------------------------------------|

| Programmable Interrupt Priority   | OS Customizable Priority Model                 |

| CPU/Task Priroty Tracking         | Reduces Software Overhead Faster SPL() Routnes |

| 32-bit Memory Mapped<br>Registers | Posted Writes; Performance Boos                |

| APIC Bus                          | Scalabity in MP Systems                        |

| Dynamic Interrupt Distribution    | Load Balancing in MP systems                   |

| Focus Processor                   | Improves Interrupt Latency                     |

| I                                 | ,                                              |

= HOT CHIPS :