# PCI Peripheral Component Interconnect

Hot Chips Symposium 11 August 1992

**David Carson**

ing Corporation

## **Peripheral Component Interconnect**

**Motivation - Design Objectives**

**Local Bus Alternatives**

**PCI** Characterization

**Performance Considerations**

**PCI Applications**

**Summary**

## MANUSY MASURINA What should a local bus accomplish?

#### **Enable PC innovation in:**

Performance: ✓ allow second to none graphics for PCs

✓ overcome standard bus limitations

Function:

✓ e.g., multi-media, motion video

at volume price points

Cost:

✓ highly integrated systems

✓ lowest cost peripherals

✓ investment spanning multiple CPU generations

#### by driving a

component-to-component connection standard for PCs, to complement existing board-to-board connection standards.

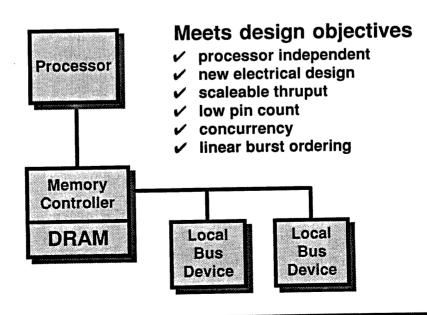

## **PCI Design Objectives**

#### Performance

- ✓ Data bursting as normal operating mode both read & write

- ✓ Linear burst ordering (NOT CAUTE WAPORDER)

- ✓ Concurrency support (deadlock, buffering solutions)

- ✓ Multi-master, peer-to-peer protocol

- ✓ Low latency guarantees for real time devices

- ✓ Access oriented arbitration (not time slice)

#### □ Cost

- ✓ No connection glue; no external data buffers

- ✓ Low pin count interface

- ✓ Implementable in existing ASIC technologies

inle

Peripheral Component Interconnect

HiChn 5

## **PCI Design Objectives**

#### □ Reliability

- ✓ Thorough electrical design for multiple loads in 33 MHz local bus environment

- ✓ Error detection, reporting

#### □ Flexibility:

- ✓ Processor independent; peripherals off processor "treadmill"

- ✓ Multi-master; peer-to-peer protocol

- ✓ Multi-media support

- ✓ Compatible with existing expansion standards

- ✓ Scaleability designed in from the beginning

- ✓ Applicable from laptop to server

## **Peripheral Component Interconnect**

intel Peripheral Component Interconnect

monp /

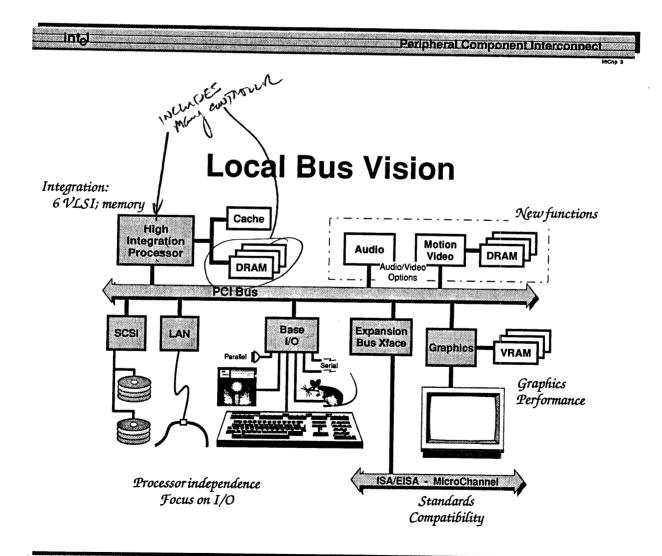

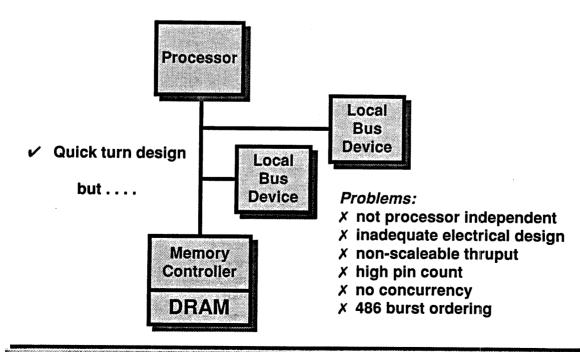

#### **Processor Bus**

Alternative 1

inta

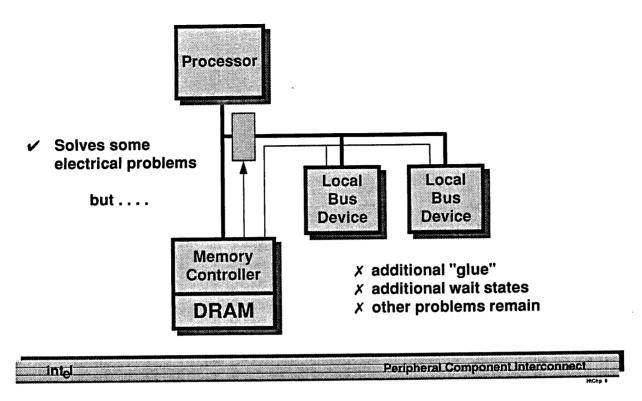

## **Buffered Processor Bus**

Alternative 2

## **Intermediate Local Bus**

Alternative 3

## **Peripheral Component Interconnect**

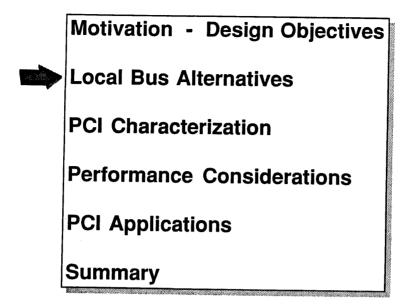

Motivation - Design Objectives

**Local Bus Alternatives**

**PCI** Characterization

**Performance Considerations**

**PCI Applications**

Summary

inta

Peripheral Component Interconnect

HtChp 1

## **PCI** Characterization

#### Protocol

- ✓ Multi-master, peer-to-peer

- √ 32-bit multiplexed, processor independent

- ✓ Low pin count; 45 slave; 47 master

- ✓ Synchronous, 8 33 MHz (132 Mbyte/sec)

- ✓ Variable length, linear bursting read & write

- $\checkmark$  Parity on address, data, command

- ✓ Concurrency/pipelining support

- ✓ Initialization hooks for auto-configuration

- ✓ Arbitration: central, access oriented, "hidden"

- ✓ Comprehends write-back cache operation

- ✓ 64-bit extension transparently interoperable with 32-bit

inta

## **PCI** Characterization

#### Electrical

- ✓ CMOS drivers; TTL voltage levels

- √ 5 V, 3.3 V interoperable; 5-volt "safe"

- ✓ Reflected wave, rail-to-rail signalling

- ✓ Dynamic current / voltage specified for drivers

- ✓ Optimized drivers minimize pwr/gnd requirements

- ✓ Direct drive no external buffers; comprehends connectors

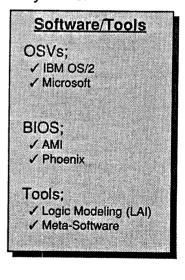

#### PCI . . . more than a paper spec

- ♦ 5000+ hours SPICE simulation completed

- → Full scale prototype correlated to SPICE model

- → PCI-optimized buffers available thru several ASIC houses

- → PCI SPICE models available thru Meta-Software

- → PCI logic/validation models available thru Logic Modeling (LAI)

**Design completeness**

RELIABILITY

inte

Peripheral Component Interconnect

## **Peripheral Component Interconnect**

**Motivation - Design Objectives**

**Local Bus Alternatives**

**PCI Characterization**

**Performance Considerations**

**PCI Applications**

Summary

## **Local Bus Bandwidth Requirements**

LAN (FDDI ~12 MB/sec)

1 MBytes/sec

❖ SCSI (multiple spindles ~10-15 MB/sec)

5+ MBvtes/sec

- Full Motion "Business Video"

- YUV-8 color space

- compressed NTSC = 0.2 MB/sec

- 320 × 240 = 2.3 MB/sec

•  $640 \times 480 = 9.2 \text{ MB/sec} (\times 2) =$

~20 MBytes/sec

Graphics:

full page

1280 × 1024

full color - RGB

× 24 bits

"flip through a book" × 10 frames/sec = 40 MBytes/sec

PCI Bandwidth:

32-bit Base

64-bit Expansion

Peak

132 MByte/s

264 MByte/s

#### **Observations**

Bandwidth needs to be efficiently shared

Transparent extensions (wider/multiple buses) are important

intel.

Peripheral Component Interconnect

MChn 1

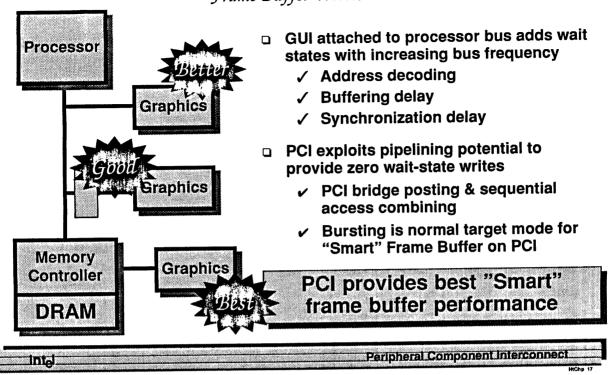

## Focus on Graphics

- □ Frame buffer access characteristics:

- ✓ Dumb Frame Buffer

~ 80% writes

✓ Windows/"Smart" Frame Buffer

> 90% writes

✓ BAPCO Benchmark

95% writes (measured)

□ Writes (not reads) determine graphics performance, consequently

Local bus design target should be ZERO processor wait-state writes especially on higher frequency processors

\_intal

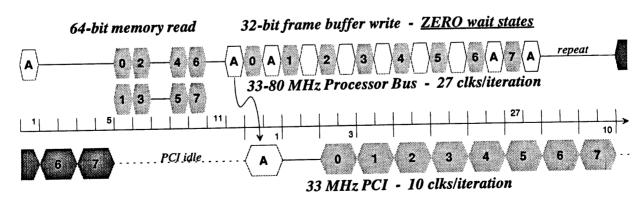

## **Graphics Performance**

Frame Buffer Writes

## An Example

Zero Wait-State Writes

Most demanding write sequence is source-copy (memory-to-screen) typically done with <u>Repeat-MOV-String</u>:

- 1. Pixel map read from memory in cache line bursts

- 2. Pixels written to frame buffer in D-word (32-bit) accesses

## **Peripheral Component Interconnect**

Intel Peripheral Component Interconnect

HtChp 1

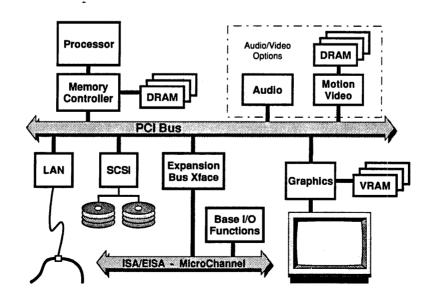

## **Desktop Application**

intal

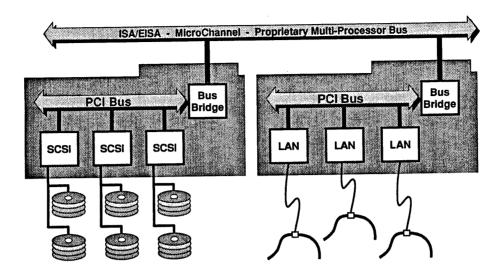

## I/O Subsystem Application

intel Peripheral Component Interconnect

## **Peripheral Component Interconnect**

Motivation - Design Objectives

Local Bus Alternatives

PCI Characterization

Performance Considerations

PCI Applications

Summary

## **Summary**

Compared with processor bus or buffered processor bus approaches, PCI provides:

Performance: Higher graphics performance.

Multi-master concurency.

Cost: Lower pin count.

Highest level of system integration.

Reliability: Thorough electrical design and

extensive modeling.

Flexibility: Processor independence.

Pre-defined, transparent scaleability.

Acceptance: Broad industry support.

⊐nt∂

Peripheral Component Interconnect

HtChp 23

## **Broad Industry Support**

"Intend to build or support PCI-compliant devices or systems."

#### **OEMs** ✓ Acer ✓ ALR ✓ AST ✓ Compaq ✓ DEC ✓ Dell ✓ Epson ✓ FUJITSU ✓ Gateway 2000 ✓ HP ✓ IBM ✓ Mitsubishi ✓ NCR ✓ NEC Tech. ✓ Oki Olivetti Siemens ✓ Tandy Unisys ✓ ZDS

| Graphics;          | Video;               |

|--------------------|----------------------|

| ✓ ATI<br>✓ Cirrus  | ✓ Intel              |

| ✓ Headland ✓ Intel | Chipsets;            |

| ✓ Matrox<br>✓ NCR  | ✓ Headland ✓ Intel   |

| ✓ Tseng Labs ✓ S3  | ✓ VLSI<br>✓ WD       |

| ✓ WD               | Board;               |

| SCSI;<br>✓ Adaptec | ✓ AMI<br>✓ Micronics |

| ✓ NCR              | Other;               |

| LAN;<br>✓ Intel    | ✓ National ✓ NCR     |

| ZTI                |                      |

inta

## **More Information?**

- □ PCI hotline: (503) 696-2000

- ✓ Request a specification

- ✓ Join PCI Special Interest Group

- ✓ Questions / Support